# VBIC Model Application and Parameter Extraction and Optimization for SiGe HBT

Sang-Heung Lee\* Regular Member, Chan-Woo Park\*\*, Seung-Yun Lee\*, Ja-Yol Lee\*, Jin-Yeong Kang\*

#### **ABSTRACT**

In 1995, a group of representatives from the integrated circuits and computer-aided design industries presented a industry standard bipolar model called the VBIC model. The VBIC model includes the improved Early effect, quasi-saturation, substrate parasitic, avalanche multiplication, and self-heating which are not available in the conventional SCiP model. This paper applies VBIC model for SiGe HBT device and develops an accurate and efficient methodology to extract all the DC and AC parameters of the VBIC model for SiGe HBT device at room temperature. Simulated results by the extracted VBIC model parameter are compared with the measurement data and show very good agreement in both DC and s-parameters prediction.

Key Words: VBIC Gummel-Poon, SiGe HBT, Parameter extraction, Parameter optimization.

# I. Introduction

The SiGe hetero-junction bipolar transistor (HBT) has been considered to be more suitable for RF integrated circuits than the Si bipolar junction transistor (BJT) because its electrical properties, current gain, power consumption, and small-signal unity-gain frequency, are superior to those of the Si BJT [1].

Users of the SPICE Gummel-Poon (SGP) model, which has been the industry standard bipolar transistor model for over 20 years, have found it to be inadequate in representing many of the physical effects important in modern advanced and scaled bipolar transistors. In 1995, a group of representatives from the integrated circuits and computer-aided design industries have collaborated and developed a new industry standard bipolar model called the vertical bipolar inter-company

(VBIC) model [2,3]. The VBIC model was developed in similar to the SGP model and overcomes its major limitations. The advantages the **VBIC** model implementation of the Early effect, improved static modeling, improved temperature forward-biased junction capacitance option, inclusion of overlap capacitance, Kirk high-current modeling, improved high-level diffusion capacitance modeling, inclusion of substrate transistor with Rc and variable beta, approximation accounting for distributed effects in the input circuit, consistent treatment of excess phase in transient and small signal analyses, models of weak avalanche effect, etc. [4].

Although an improved accuracy of the VBIC model over the SGP model has been demonstrated, procedure and steps for the extraction and optimization of the VBIC model parameters were not nearly discussed. In this

<sup>\*</sup> SiGe Device Team, Electronics and Telecommunication Research Institute (shl@etri.re.kr)

<sup>\*\*</sup> Basic Research Division, Electronics and Telecommunication Research Institute 논문번호: 030041-0127, 접수일자: 2003년 1월 27일

paper, we applies VBIC model, which was for silicon BJT, for 'compound developed semiconductor SiGe HBT device and seeks to develop an accurate and efficient methodology to extract all the DC and AC parameters of the VBIC model for SiGe HBT. Simulated results using the extracted parameters of SiGe HBT device will be compared with measurement data. The emitter area of SiGe HBT device used in extraction of model parameters is  $0.5 \times 6.0 \mu$  m<sup>2</sup>, was fabricated by Electronics Telecommunications Research Institute (ETRI), Korea. The forward DC current gain, cutoff frequency, and maximum oscillation frequency of fabricated SiGe HBT device are about 160, 40GHz and 30GHz, respectively, and the extracted model parameters will be used in design of **DSRC** 5.8GHz (Dedicated Short Range Communication) communication **ITS** for (Intelligent Transportation Systems).

# II. Extraction and Optimization of VBIC Model Parameters for SPICE Simulation

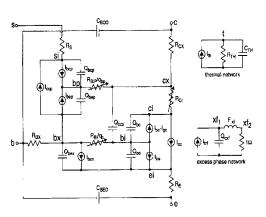

The equivalent circuit of VBIC model is shown in fig. 1. Unlike the SGP model, which has three terminals, the VBIC model is a four-terminal model comprising the base (b), emitter (e), collector (c), and substrate (s). The other nodes in VBIC model are the extrinsic base bx, parasitic base bp, intrinsic base bi, intrinsic emitter ei, intrinsic collector ci, and extrinsic collector cx. The VBIC model includes the following features that make it distinct from the SGP model. First, the effect of parasitic substrate PNP transistor was included by a simplified SGP model. Second, the quasi-saturation behavior was modeled with the elements R<sub>CI</sub>, Q<sub>bcx</sub>, and modified Q<sub>bc</sub>. Third, the effect of excess phase was modeled with a second-order sub-network through delay time TD which makes consistent small-signal to transient analysis. Fourth, in addition to the conventional strong avalanche

Fig. 1. Equivalent circuit for VBIC bipolar transistor model.

current, a weak avalanche current  $I_{gc}$  was added for the base-collector junction. Fifth, to account for the extrinsic capacitances associated with the regions in which the  $p^+$  base and  $n^+$  emitter are overlapped, two constant capacitances  $C_{BE0}$  and  $C_{BC0}$  were included in the VBIC model. Finally, a self-heating model was included as a separate option for the VBIC. The model consists of the thermal resistance  $R_{TH}$  and capacitance  $C_{TH}$ , along with the thermal power source  $I_{th}$ , which couples the power generated in the bipolar transistor to the thermal network. The local temperature rise at node t in the thermal network is linked to the electrical model through the temperature mappings of the model parameters [3,4].

To extract and optimize model parameter, the measurement was carried out HP4145/4142 semiconductor parameter analyzer while junction capacitances were measured as function voltage using HP4280A semiconductor/component test system. Also, AC measurement was performed using HP8510B vector network analyzer. The forward DC current gain, cutoff frequency, and maximum oscillation frequency of the SiGe HBT device with  $0.5x6.0\mu$ m<sup>2</sup> emitter area are about 160, 40GHz and 30GHz, respectively, and the extracted model parameter will be used in design of 5.8GHz DSRC communication for ITS. The device was fabricated by 0.8 m SiGe BiCMOS line of Electronics and Telecommunications Research

### Institute (ETRI), Korea

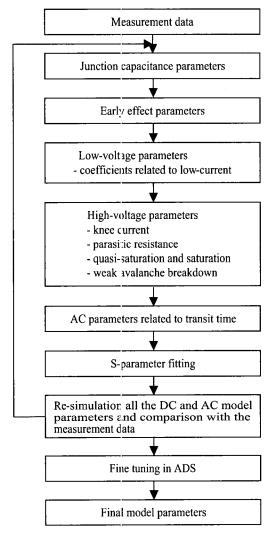

The VBIC model parameter extraction and optimization method developed in this paper was performed using UTMOST III modeling framework [5]. Fig. 2 shows the overall flowchart of the VBIC model parameter extraction and optimization procedure we have developed for SiGe HBT. The steps for extracting and optimizing VBIC parameters of SiGe HBT device are listed and discussed as follow.

Fig. 2. Flowchart for VBIC model parameter extraction and optimization of SiGe HBT.

# 2.1 Junction capacitance parameters In the VBIC model, the parameters associated

with junction capacitance are first extracted. The junction capacitance parameters are extracted using capacitance-voltage (C-V) measurement data. The depletion capacitance data should be taken in a forward bias condition up to a point till the diffusion capacitances kicks in. From measured  $C_{be}$  versus  $V_{be}$  data, in reverse bias and low forward bias regions, CJE, PE, and ME are extracted and optimized. From measured  $C_{bc}$  versus  $V_{bc}$  data, in reverse bias and low forward bias regions, CJC, CJEP, PC, and MC are extracted and optimized. From measured  $C_{sc}$  versus  $V_{sc}$  data, in reverse bias and low forward bias regions, CJCP, PS, MS are extracted and optimized.

#### 2.2 DC parameters

The steps for extracting and optimizing VBIC DC model parameters of SiGe HBT are discussed as follow.

As a first step of DC parameter extraction, forward and reverse early voltages (VEF, VER) are extracted and optimized using previous junction capacitance parameters. Physically, the Early voltage accounts for the account of base-width modulation due to change in the collector-base reverse voltage. As the Early approximation to avoid problems in the SGP model was known to have inaccuracies in Early effect modeling, junction depletion charge was introduced in the VBIC model. Forward and reverse early voltages (VEF, VER) for low bias condition are obtained using the following equations [6].

$$\begin{pmatrix} f & f & f \\ q_{j,bc} - f & f \\ g_0 & V_{ef} \end{pmatrix} \cdot \begin{matrix} \uparrow & f & \uparrow \\ +q_{j,be} \cdot \begin{matrix} \uparrow \\ V_{er} \end{matrix} = -1$$

$$q'_{j,bc} \cdot \begin{matrix} \uparrow \\ \downarrow \\ V_{ef} \end{matrix} + \begin{pmatrix} f & f \\ q'_{j,be} - f \\ 0 & V_{er} \end{matrix} \cdot \begin{matrix} \uparrow \\ V_{er} \end{matrix} = -1$$

$$(1)$$

Here, superscripts f and r denote forward and reverse modes, respectively, and  $g_0$  is the output conductance which can be determined from the

forward and reverse output characteristics at fixed low-bias  $V_{bc}$  and  $V_{bc}$  since the Early effect model was developed under low injection condition. In equation (1),  $q_j$  is the junction charge and  $c_j$  is the junction capacitance which is calculated from the junction capacitance-voltage measurement.

As a second step, low voltage parameters of Gummel plot are extracted and optimized. From the forward Gummel plot, IS, NF, IBEI, NEI, IBEN, and NEN parameters are extracted and optimized. Next, from the reverse Gummmel plot, NR, IBCI, NCI, IBCN, NCN, ISP, WSP, NSF, IBEIP, and IBENP are extracted and optimized. Note that the parameters extracted include the parasitic PNP transistor current components [7].

As a third step, high voltage parameters of Gummel plot are extracted and optimized. (1) Knee current parameters (IKF, IKR) are obtained taking extrapolated intercept point low-current and high-current curves from the forward and reverse Gummel plots, respectively, and their values are optimized later together with other parameters. (2) The resistor parameters RE and RCX are obtained from the flyback measurement, respectively. The base resistances RBX and RBI are obtained from the forward Gummel plot at high voltages while the parasitic resistances RBP and RS are extracted from the reverse Gummel plot. Then, these extracted resistance parameters are optimized, together with the knee currents extracted previously. (3) The parameters associated with quasi-saturation effect can be extracted from the forward current-voltage characteristics under quasi-saturation and saturation operations. They include the series resistances RCX and RCI, and quasi-saturation parameters VO, GAMM, and HRCF. (4) Next, based on the current-voltage characteristics in breakdown region, the extraction and optimization of the parameters AVC1 and AVC2 associated with forward weak avalanche breakdown and parameters AVE1 and AVE2 associated with the reverse weak avalanche breakdown are performed.

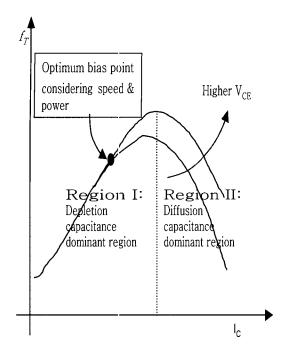

To extract AC parameters, the s-parameter measurements (in the range of 500MHz to 10GHz frequency) were carried out using a HP8510B vector network analyzer at room temperature. The parasitic components associated with the resistance, inductance, and capacitance of the probes, device pads and interconnects are de-embedded. Transit time  $\tau_F$  is commonly determined the cutoff frequency  $f_{\rm T}$ measurement. The cutoff frequency determined by extrapolating h21 parameter transformed from measured s-parameter parameters related to transit time are extracted from  $f_{\Gamma}$ -I<sub>C</sub> curve shown in fig. 3.

In this paper, the methods of AC parameter extraction and s-parameter fitting are summarized as follow. Firstly  $(f_T-I_C)$  curve fitting), since Region I of fig. 3 is dominated by depletion initial capacitance, depletion capacitance parameters optimized in section 2.1 are optimized again, in Region I, to exactly fit  $f_{T}I_{C}$  curve and s-parameters. Secondly (parameter optimization associated with transit time), AC parameters associated with transit time are extracted mainly, in Region II of  $f_T$ -I<sub>C</sub> curve of fig. 3. Finally (s-parameter fitting), as some parameters are voltage-dependent and/or current-dependent (or not linear), s-parameter fitting cannot be done satisfyingly in all bias points. Because of this reason, s-parameter fitting is performed in specific bias point, i.e. optimum bias point considering speed and power indicated fig. 3. In addition to, initial parasitic resistance parameters (RBX, RE, RCX, RBI) optimized in the previously two steps of this section are used simultaneously in s-parameter fitting step

Fig. 3. Variation of cutoff frequency with collector current.

# 2.4 Overall parameters optimization

At this step, all the extracted DC and AC parameters are optimized simultaneously carefully to get the most accurate DC and AC prediction and finally, all the SiGe HBT VBIC DC/AC parameters extracted previously are tuned again with circuit simulator, ADS (version 2001).

#### III. Results and Discussion

Fig. 4 compares the DC measurement data and simulation results of the current-voltage characteristics, Gummel plot, current gain under forward operation of SiGe HBT. Fig. 5 and fig. 6 show small-signal s-parameters, S11, S21, S12, S22 traces under  $V_{CE}$ =1.0V,  $I_{C}$ =1mA and  $V_{CE}$ =2.0V,  $I_{C}$ =1mA for SiGe HBT, respectively.

For DC optimization, average error between measurement and modeled results was below 15 % and for AC s-parameter optimization, average error between measurement and modeled results was below 5 %. As a result

Fig. 4. Comparison of measured and simulated DC results under forward operation of SiGe HBT. (a) Current-voltage characteristics, (b) Gummel plot, (c) current gain. (line: measured, dot: simulated)

of these, the simulation results were in very good agreement with the measurement data and, we can conclude that the extraction and optimization methodology of this paper is very adequate for SiGe HBT modeling using the VBIC model.

### **IV.** Conclusions

The VBIC model includes the improved Early quasi-saturation, substrate parasitic, effect, avalanche multiplication, and self-heating which are not available in the conventional SGP model. In this paper, we have applied the bipolar junction transistor model, VBIC model for SiGe HBT device and presented an accurate and efficient methodology to extract and optimize all the DC and AC parameters of the VBIC model for SiGe HBT at room temperature. Simulated results by extracted VBIC model parameters showed very good agreement with both measured DC and s-parameters data. These results show that the VBIC model can overcome the problem that accuracy in modeling SiGe HBT using the conventional SGP model is decreased. Parameter extraction related to temperature modeling which is one of important characteristics in the VBIC model is yet not performed, but we intend to develop methodology in the near future.

Fig. 5. Comparison of measured and simulated s-parameters under  $V_{CE}=1V$ ,  $I_{C}=1mA$  for SiGe HBT. (a) S11, (b) S21, (c) S12, (d) S22. (circle: measured, line: simulated)

Fig. 6. Comparison of measured and simulated s-parameters under  $V_{CE}$ =2V,  $I_{C}$ =1mA for SiGe HBT. (a) S11, (b) S21, (c) S12, (d) S22. (circle: measured, line: simulated)

# Acknowledgments

This work was supported by the Ministry of Information and Communication, Korea.

#### References

- [1] S.-Y. Lee, H.-S. Kim, S.-H. Lee, K.-H. shim, J.-Y. Kang, M.-K. Song, "The behavior of Ti silicidation on Si/SiGe/Si base and its effect on base resistance and fmax in SiGe hetero-junction bipolar transistors", *Journal of Materials Science:*Materials in Electronics, 12(8), pp. 467-472, August 2001.

- [2] H.K. Gummel and H.C. Poon, "An integrated charge-control model of bipolar transistors", *Bell System Tech. J.*, 49, pp. 827-852, May 1970.

- [3] C.C. McAndrew, J.A. Seitchik, D.F. Bowers, M. Dunn, M. Foisy, I. Getru, M. McSwain, S. Moinian, J. Parker, P. van Wijnen, L.F. Wagner, "VBIC95: An improved vertical, IC bipolar transistor model," Proceedings of IEEE Bipolar/BiCMOS Circuits and Technology Meeting, pp. 170-177, 1995.

- [4] F. Najm, "VBIC95: An improved bipolar transistor model", *IEEE Circuits and Devices Magazine*, 12, pp. 11-15, March 1996.

- [5] SILVACO International, UTMOST (Universal Transistor MOdeling SofTware) [[] (SILVACO International Inc., Santa Clara, 1995).

- [6] C.C. McAndrew and L.W. Nagel, "SPICE Early modeling," Proceedings of IEEE Bipolar/BiCMOS Circuits and Technology Meeting, pp. 144-147, 1994.

- [7] X. Cao, J. McMacken, P. Layman, J.J. Liou, A. Sun, S. Moinian "Parameter extraction and optimization for new industry stand VBIC model," *International Conference on Advanced Semiconductor Devices and Microsystems*, pp. 107-115, 1998.

Sang-Heung Lee(이 상 홍) Regular Member

He received the B.S., M.S., and Ph. D. degrees in department of electronics engineering from Chungnam National University, Daejon, Korea, in 1988, 1992, and 1998, respectively. From 1998

to 1999, he held a position as a post-doctorial researcher at Electronics and Telecommunications Research Institute, Korea. Since July 1999, he has been working as a senior member of research staff at Electronics and Telecommunications Research Institute, Korea. His research interests include radio frequency integrated circuits design and high speed digital communication circuits design, semiconductor device modeling, and SPICE parameter extraction and optimization. He is a member of KICS, IEEK, and KEES.

Chan-Woo Park(박 찬 우)

He received the B.S., M.S., and Ph.D degrees in materials science and engineering from Korea Advanced Institute of Science and Technology, Daejeon, Korea, in 1994, 1996, and 2000, respectively.

Since 2000, he has been with the Electronics and Telecommunications Research Institute, Daejeon Korea, as a senior research staff. His research interests include SiGe HBT and IC technology, molecular electronics, and nano-electronic devices.

Seung-Yun Lee(이 승 윤)

He received the B.S., M.S., and Ph.D degrees in materials science and engineering from Korea Advanced Institute of Science and Technology, Daejeon, Korea, in 1994, 1996, and 1999, respectively.

Since September 1999, he has been working as a senior member of research staff at Electronics and Telecommunications Research Institute, Korea. His research interests include fabrication and characterization of SiGe devices, Cu metallization process for interconnects, deposition methods of thin films, and universal thin film phenomena.

Ja-Yol Lee(이 자 열)

He received the B.E. degree from Konkuk university, Seoul, Korea, in 1998 and the M.E. degree from Chungnam National Univerity, Daejeon, in 2000, all in electronics engineering. Since 2001, he

has been with ETRI, where he has been working as RF & Analog Circuit Designer. His research interests are RFIC and OEIC design, semiconductor device modeling, and SPICE parameter extraction and optimization. He is a member of KICS and KEES.

Jin-Yeong Kang(강 진 영)

He received the M.E. and Ph. D. degrees in Physics from Korea Advanced Institute of Science and Technology, in 1979 and 1991, respectively. He joined the Electronics and Telecommunications Research

Institute (ETRI) at Daejeon in 1979. He has been working on the development of SiGe Devices and Processes. At present, he is a director of SiGe Device Team at ETRI-Basic Research Laboratory.