## 논 문 13-5-1

# Electrical Characteristics of Metal/n-InGaAs Schottky Contacts Formed at Low Temperature

Hoong-Joo Lee \*

#### Abstract

Schottky contacts on n-In<sub>0.53</sub>Ga<sub>0.47</sub>As have been made by metal deposition on substrates cooled to a temperature of 77K. The current-voltage and capacitance-voltage characteristics showed that the Schottky diodes formed at low temperature had a much improved barrier height compared to those formed at room temperature. The Schottky barrier height,  $\phi_B$ , was found to be increased from 0.2eV to 0.6eV with Ag metal. The saturation current density of the low temperature diode was about 4 orders smaller than for the room temperature diode. A current transport mechanism dominated by thermionic emission over the barrier for the low temperature diode was found from current-voltage-temperature measurement. Deep level transient spectroscopy studies exhibited a bulk electron trap at  $E_c$  - 0.23eV. The low temperature process appears to reduce metal induced surface damage and may form an MIS (metal-insulator- semiconductor)-like structure at the interface.

Key Words: Schottky barrier, Low temperature process, InGaAs, Current transport mechanism, Metal-semiconductor interface

#### 1. Introduction

III-V compound In<sub>0.53</sub>Ga<sub>0.47</sub>As lattice matched to InP is a promising material because of its high electron mobility and For saturation velocity. this reason. n-In<sub>0.53</sub>Ga<sub>0.47</sub>As is desirable for high speed and 1.3 µm optoelectronic applications. However, Schottky barrier height of a conventional diode on n-InGaAs room prepared at temperature (RT=300K) is too low ( $\phi_B = \sim 0.2 \text{eV}$ ) to be used for realization of good Schottky devices including FET applications. Several approaches have been made to fabricate elevated barrier height diodes to n-InGaAs using chemical passivation with  $P_2S_5/(NH_4)_2S[1]$ , intentional surface oxidation in deionized water[2], ion-implantation with Be[3], a highly doped p-InGaAs interfacial interlayer[4], an excimer laser photodeposited Cd interlayer[5], and  $Pr_2O_3$  and  $In_2O_3$  interlayers in the liquid phase epitaxy[6].

Shi and Anderson have developed at low temperature (LT=77K) metal deposition to fabricated stable, high quality and high barrier height Schottky contacts to *n*-InP[7]. For evaporation with the substrate cooled to low temperature, evaporated metal films tend to be uniformly distributed on the semiconductor whereas this is often not the case at room temperature. A Pd/*n*-InP LT diode made by this

(Chungnam, Chonan, Anseo-dong, San98-20, Fax: 0417-550-5363 Email: hjtee@smuc.ac.kr) 2000년 2월 21일 접수, 2000년 4월 12일 심사완료

<sup>\*</sup> Div. of Computer-Information-Telecommunication Science, Sangmyung University

cryogenic processing in their study showed on ultrahigh barrier height of 0.96eV and excellent long term stability. Their Raman spectroscopy studies indicated that the metal-semiconductor interface of the LT diode had an amorphous nature which served as a stable insulator and enhanced the barrier[8].

In this work, the same low temperature deposition process is applied to improve Schottky height on *n*-InGaAs diodes[9]. contacts formed on n-InGaAs substrates at room temperature and low temperature are studied by current-voltage-temperature (I-V-T)capacitance-voltage-temperature (C-V-T)and estimate electrical measurements to characteristic parameters and to examine current transport mechanism in the LT diodes.

#### 2. Experiment

The Schottky diodes used in this study were fabricated on 1.0 m thick n-InGaAs epilayers with two different free-carrier concentration of 1  $\times 10^{17}$  cm<sup>-3</sup> (called S1 in this paper), and 5  $\times 10^{15}$ cm<sup>-3</sup> (S2) grown on an  $n^+$ -InP substrate by MOVPE. There exist InGaAs and InP buffer layers between the top epilayer and the substrate. The diode fabrication consisted of three steps; i.e. ohmic contact on the back of the substrate, native oxide removal from the front of the InGaAs layer by chemical etching, and Schottky contact formation on the substrate cooled to low temperature[9]. First. the samples sequentially cleaned by trichloroethylene, acetone, methanol and de-ionized water, and then blown dry with nitrogen gas. The ohmic contact was formed on an  $n^{\dagger}$ -InP substrate by evaporating Au Ge/Ni and alloying by rapid thermal annealing (RTA) at 360°C for 10s. A proximity cap was also used to protect the front surface during the annealing process. The native oxide on the front surface of the sample was then removed by wet chemical etch with diluted H2SO4 solution for 60s. After the samples were rinsed in de-ionized water and blown dry with hydrogen gas, they were quickly loaded into an evaporator. Schottky metals Au or Ag, 1000 Å thick, were deposited on the n-InGaAs layers at a substrate temperature of 77K under a high vacuum of 2 x 10<sup>-7</sup>torr. The low temperature was achieved by continuous liquid nitrogen flow into the sample holder and monitored with a chromel-alumel surface mounted thermocouple.

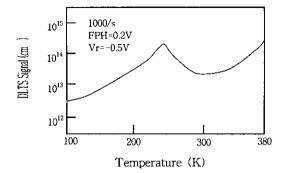

The *I-V-T* and *C-V-T* characteristics of the 0.8mm<sup>2</sup> diodes were measured from 100K and 300K in an auto data acquisition cryogenic system. The DLTS measurements were performed in a Polaron DL4600 deep level transient spectrometer system with temperature from 100K to 380K. The reverse bias was kept at -0.5V while the filling pulse was changed from 0 to 0.4V to distinguish the bulk and interface traps.

#### 3. Results and discussion

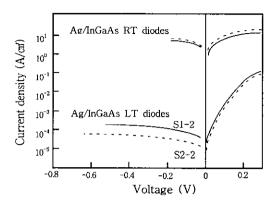

Figure 1 and Table 1 show the room temperature current-voltage (*I-V*) characteristics

| Table 1. | Electrical | characteristics | for | In Ga As | LT | diodes |

|----------|------------|-----------------|-----|----------|----|--------|

|          |            |                 |     |          |    |        |

| Sample | Metal | $N_{\mathrm{D}}(\mathrm{cm}^{-3})$ | $\phi_{\mathrm{BIV}}(\mathrm{eV})$ | Φ <sub>BCD</sub> (eV) | n    | $V_{\mathrm{BR}}(\mathrm{V})$ | $J_{\rm R}$ at $-1{ m V(Acm}^{-2})$ |

|--------|-------|------------------------------------|------------------------------------|-----------------------|------|-------------------------------|-------------------------------------|

| S1-1   | Au    | 1 x 10 <sup>17</sup>               | 0.49                               | 0.51                  | 1.66 | ~1.5                          | $4.0 \times 10^{-2}$                |

| S1-2   | Ag    | 1 x 10 <sup>17</sup>               | 0.57                               | 0.59                  | 1.32 | ~5.0                          | $2.0 \times 10^{-4}$                |

| S2-1   | Au    | 5 x 10 <sup>15</sup>               | 0.50                               | 0.52                  | 1.57 | ~3.0                          | $5.0 \times 10^{-3}$                |

| S2-2   | Ag    | 5 x 10 <sup>15</sup>               | 0.60                               | 0.61                  | 1.23 | ~6.0                          | 8.7 x 10 <sup>-5</sup>              |

It is impossible to calculate meaningful diode characteristics from RT diodes due to their near-ohmic behavior.

and processed data for Ag/InGaAs RT and LT diodes. I-V characteristics for Au/InGaAs LT diodes are also presented in the same table. The device behavior is clearly dependent on the substrate temperature during metal deposition, the choice of metal and free carrier density. For the RT diodes, the I-V characteristics look almost ohmic due to their low Schottky barrier height. For the LT diodes, however, higher barrier heights  $\Phi_B$  calculated from the following Eq. 1 were obtained:

$$J_0 = A^* T^2 \exp(-\phi_B/kT), \tag{1}$$

where  $J_0$  is the saturation current density and  $A^*$  = 5.04Acm<sup>-2</sup>K<sup>-2</sup> is the Richardson constant of n-InGaAs. The ideality factor, n, was determined from the forward current characteristics using the relation:

$$n = (q/kT)[\partial V/\partial (\ln I)]$$

(2)

For Au/n-InGaAs LT devices (S1-1),  $\phi_B$  and n were found to be 0.49eV and 1.66, respectively. For Ag/n-InGaAs devices (S1-2),  $\phi_B$  and n were 0.57eV and 1.32, respectively. Compared with the RT diode, the reverse leakage current density of the LT diode was reduced by 3 to 4 orders. The highest barrier height was obtained from Ag/n-InGaAs LT diodes fabricated on a substrate with  $N_D = 5 \times 10^{15} \text{cm}^{-3}$ . The barrier height  $\phi_B$ and an ideality factor n for S2-2 were 0.60eV and 1.23, respectively. The breakdown voltage  $V_{\rm BR}$  of S2-2 was also much improved to a value of more than 6V. A 5 order reduction of the reverse leakage current was obtained for this sample and a soft reverse current characteristic was not observed. Ni, Cr, Pd and Al were also tried as a barrier metal, but no significant improvement of barrier height was observed. It is interesting that for all LT diodes, Schottky barrier height and reverse current characteristics were better with Ag compared to Au. This relates to Ag as the only metal studied to date which shows no tendency to chemically bond to or react with GaAs[10]. Also, the surface chemistry of InGaAs is similar to that of GaAs[1]. Even at the low temperature, Ag may have less probability to cause chemical reactions with the substrate compared to Au. Thus, the

Fig. 1. Room temperature I-V characteristics for RT and LT diodes.

barrier height changes for the Ag barriers could be due to a change in the InGaAs substrate caused by low temperature processing.

The barrier heights from 1MHz capacitance-voltage (C-V) measurement were in with good agreement those from which indicates the measurement, lack frequency dependence of interface states. The effective barrier height was calculated from the expression:

$$\phi_{\rm B} = V_i + \xi + kT/q, \tag{3}$$

where  $V_i$  is the built-in potential, and  $\xi$  is the potential difference between the Fermi-level and the conduction band-edge. From Eq. 3, the Schottky barrier heights of Ag/InGaAs LT diodes S1-2 and S2-2 at 300K were determined to be 0.59 and 0.61eV, respectively. C-V-T characteristics were also measured for S1-2 and S2-2 in the temperature range of 100-300K. Good

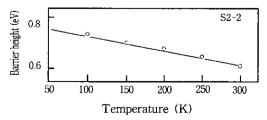

Fig. 2. Temperature dependence of zero-bias barrier heights for the Ag/InGaAs LT diode.

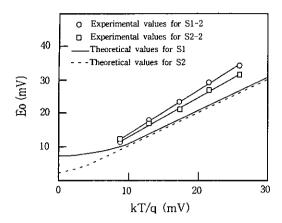

Fig. 3. Temperature dependence of E<sub>0</sub> for Ag/InGaAs LT diodes.

linearity was shown over the entire temperature range at reverse bias less than 1.5V. Temperature dependence of zero bias barrier height  $\Phi_{B0}$  is described by:

$$\phi_{B0} = \phi_0 + \beta T, \qquad (4)$$

where  $\phi_0$  is the barrier height at zero temperature and zero bias, and  $\beta$  is the temperature coefficient of zero bias barrier height. The values of  $\phi_{B0}$  vs temperature are shown in Fig. 2. The experimental values of  $\phi_{B0}$  fit well to Eq. 4 with  $\phi_0 = 0.78 \text{eV}$  and  $\beta = -6.0 \times 10^{-4} \text{eVK}^{-1}$  for S2-2.

Figure 3 shows experimental and theoretical values of  $E_0$  as a function of temperature for samples S1-2 and S2-2 under forward bias.  $E_0$  is a characteristic value dependent on the transport mechanism of carriers through the barrier[11]. Theoretically, S2-2 sample should give TE(thermionic emission) as transport mechanism in all of the temperature regions due to its low doping concentration. Tunneling can be expected for sample S1-2 in the low temperature region less than 100K due to its rather high doping concentration. Experimentally, S1-2 and a conduction showed dominated thermionic emission in a measured temperature region from 100 to 300K. But, ideality factors were a little larger than unity as a deviation from the theoretical curve. Large ideality factors observed from Ag/InGaAs LT diodes are possibly related to a thin interface layer having an

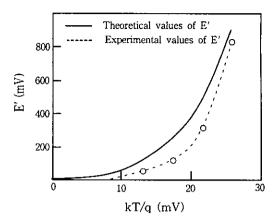

Fig. 4. Theoretical and experimental values of E' as a function of temperature for diode S1-2.

amorphous structure. This is also confirmed by a low value of measured Richardson constant[12]. The Richardson constant of  $0.37 \text{Acm}^{-2} \text{K}^{-2}$  and the activation energy of 0.51 eV for the Ag/InGaAs LT diode were found from a Richardson plot  $\ln(J_0/T^2)$  against 1000/T.

The reverse current for S1-2 with a high free carrier concentration was found to be independent of temperature with increase of bias. Its reverse current at a fixed bias was exponentially higher with a decrease of temperature compared to a S2-2. doped sample Theoretical experimental curves of E' as a function of kT/qare shown in Fig.4, where E' is a characteristic value under reverse bias[11]. The two plots do not match perfectly due to steep increase of reverse current but a similar shape is observed. Using the theoretical value for  $E_0$  at 0K for S1 and the boundary conditions from Padovani and Stratton[11]. even field emission may considered at low temperature less than ~100K with the reverse bias higher than 0.1V. Thus, this excess reverse current may be attributed to a tunneling current component due to a high barrier and high doping density.

This low temperature process also made it possible to measure deep level transient spectroscopy spectra shown in Fig. 5 since leakage current was low. One electron trap

Fig. 5. A DLTS curve for the low temperature sample.

located at  $E_{\rm c}$  -  $0.23{\rm eV}$  was identified as a bulk trap. No surface trap was found.

Several models for the metal-semiconductor interface have been proposed, relying on effective work functions, defects at the interface, reactivity between metal and semiconductor. and the inhomogeneous Schottky barrier model[12-13]. For the LT diode, a combined type with the models mentioned above should likely be considered, because metal deposition at LT has shown a low trap density. uniform metal coverage nonreactivity of Ag[9]. The fundamental mechanisms determining the Schottky barrier height for the InGaAs LT diodes are so far not well understood. Further investigation using structural analysis technique can be needed to correlate the LT film with the characteristics.

### 4. Conclusions

The LT process provides a simple way to improve the Schottky barrier height on  $n-In_{0.53}Ga_{0.47}As$  from  $\sim 0.2$  to 0.60eV with Ag metal. Compared with the RT diode, the reverse leakage current density of the LT diode is reduced by five orders. From I-V data for the Ag/InGaAs LT diodes, it is found that the forward and reverse I-V-T characteristics are dependent on the free carrier concentration of n-InGaAs layers. A relatively high free carrier concentration and the enhanced barrier height of the sample increase the tunneling component of

the reverse current and lead to a large leakage current. For the low doped LT sample, however, thermionic emission is a dominant conduction mechanism over the Schottky barrier. This low temperature process also makes it possible to measure the DLTS spectra. A bulk electron trap for LT diodes is found and its activation energy is  $\sim 0.23 \text{eV}$ . The improvement in  $\phi_B$  and reverse leakage current with LT metal deposition could be attributed to the uniform metal coverage on an InGaAs surface and the formation of an amorphous-like structure instead of an alloy layer at the metal-semiconductor interface. Thus, metal induced surface damage can be greatly reduced by LT processing and the amorphous layer could serve as an insulator to make the LT diode an MIS-like structure.

### References

- [1] K. C. Hwang, S. S. Li, C. Park and T. J. Anderson, "Schottky Barrier Height Enhancement of n-InGaAs by A Novel Chemical Passivation Technique," J. Appl. Phys., Vol. 67, pp.6571-6573, 1990.

- [2] S. Loualiche, H. L'Haridon, A LeCorre, D Lecrosnier, M. Salvi and P.N. Favennec, "Schottky And Field-Effect Transistor Fabrication on InP and GaInAs," Appl. Phys. Lett., Vol. 52, pp.540-542, 1988.

- [3] G. Fernholz, R. Westphalen, W. Lange and H. Beneking. "Enhanced Schottky Barrier Heights on n-Type GaInAs by Be Electron. Implantation," Lett., Vol. 23, pp.722-723, 1987.

- [4] P. Kordôs, M. Marso, R. Meyer and H. Lüth, "Schottky Contacts on n-InGaAs with Enhanced Barriers by Counter-Doped Interfacial Layers," IEEE Trans. Electron Devices, Vol. 39, pp.1970-1972, 1992.

- [5] T. Licata, M. Schmidt, D. Podlesnik, V. Liberman and R. Osgood, "Application of Photodeposited Cd to Schottky Barrier Diode And Transistor Fabrication on InP and InGaAs Substrates," Appl. Phys. Lett., Vol. 58, pp.845-847, 1991.

- [6] H. T. Wang, S. T. Chou, L. B. Chang, T. W. Wang, and H. C. Tang, The Enhancement of InGaAs Schottky Barrier Height by The Addition of Pr<sub>2</sub>O<sub>3</sub> And In<sub>2</sub>O<sub>3</sub> in The Liquid Phase Epitaxy," Appl. Phys. Lett., Vol. 70, pp.2571-2573, 1997.

- [7] Z. Q. Shi, R. L. Wallace and W. A. Anderson, "High-barrier Height Schottky Diodes on n-InP by Deposition on Cooled Substrates," Appl. Phys. Lett., Vol. 59, pp.446-448, 1991.

- [8] Z. Q. Shi and W. A. Anderson, "Electrical And Optical Characterization of Metal/n-InP Interfaces Formed by A Cryogenic Process in High Vacuum," J. Vac. Sci. Technol., Vol. B11, pp.985-989, 1993.

- [9] H. J. Lee, W. A. Anderson, H. Hardtdegen and H. Lüth, "Barrier Height Enhancement of Schottky Diodes on n-InGaAs by Cryogenic

- Processing," Appl. Phys. Lett., Vol. 63, pp.1939–1941, 1993.

- [10] K. Chin, S. Pan, D. Mo, P. Mahowald, N. Newman, I. Lindayu and W. E. Spicer, "Electronic Structure And Schottky Barrier Formation of Ag on n-Type GaAs(110)," Phys. Rev., Vol. B32, pp.918-922, 1985.

- [11] F. A. Padovani and R. Stratton, "Field And Thermionic-Field Emission in Schottky Barriers," Solid-State Electron., Vol. 9, pp.695-707, 1966.

- [12] E. H. Rhoderick and R. H. Williams, Metal Semiconductor Contacts, 2nd Ed., pp.130-168, Oxford Univ. Press, New York, 1988.

- [13] R. T. Tung, "Schottky Barrier Height Do We Really Understand What We Measure," J. Vac. Sci. Technol., Vol. B11, pp.1546-1552, 1991.