# 직류 전원 분할용 커페시터의 용량 변화에 따른 ZVS-HB형 고주파 공진 인버터의 특성해석

論 文 49B-5-9

# Characteristic Analysis of ZVS-HB Type High Frequency Resonant Inverter According to the Variable Capacitance of the DC Voltage Source Separation Capacitor

文 昶 琇\*・金 鍾 海\*\*・金 東 熙\*\*\*・吳 承 勳§・沈 光 烈§§、閔 丙 才§§§ (Chang-Soo Moon・Jong-Hae Kim・Dong-Hee Kim・Seung-Hoon Oh・Kwang-Yeal Sim・Byeong-Jae Min)

Abstract-This paper presents about an example of circuit design and characteristics of inverter according to the variable capacitance of the DC voltage source separation capacitor used in ZVS-HB type high frequency resonant inverter. The soft switching technology known as ZVS is used to reduce turn off loss at switching. In the event the capacitance of the DC voltage source separation capacitor is varied, the analysis of inverter circuit has generally described by using normalized parameter and operating characteristics have been evaluated in terms of switching frequency and parameters. According to the calculated characteristics value, a method of the circuit designs and operating characteristic of the inverter is also presented in this paper. In addition, this paper proves the validity of theoretical analysis through the experiment. This proposed inverter shows that it can be practically used in future as power source system for the lighting equipment of discharge lamp, DC-DC converter etc.

Keyword: ZVS, separation capacitor, Normalized parameter, Circuit design, Resonant inverter

#### 1. Introduction

In recent years, according to using a power semiconductor device which has advantageous characteristics of high speed switching and small driving power, switching frequency of power conversion system has been ranging from tens of kHz to hundreds of kHz. [1][2][3]

In driving a power switching semiconductor device to high speed switching, there are some problems such as dv/dt and di/dt stress, EMI problem, increase of switching loss due to charge dump of the switching device, the leakage inductive etc. in the circuit. So, in order to remove some problems, this paper introduced ZVS and ZCS technology to reduce turn on and off loss at switching and the main conversion circuit is composed of the resonant type circuit. Generally, the voltage-fed high frequency resonant inverter consisting of half-bridge type uses the DC voltage source separation capacitor in order to separate the DC voltage source. The DC voltage source separation capacitor, however, has some problems such

as the light weight and small size because the increase of the capacitance of the DC voltage source separation capacitor causes an increase of in-rush current. The characteristic analysis according to the capacitance ratio of the resonant capacitor and the DC voltage source separation capacitor used in ZVS-HB type high frequency resonant inverter are described in this paper. In the event the capacitance of the DC voltage source separation capacitor is varied, the analysis of inverter circuit can be generally described by using normalized parameter.

The operating characteristics have been evaluated in terms of switching frequency and parameters. According to the calculated characteristic value, a method of the circuit design and operating characteristics of the inverter is proposed.

In addition, this paper proves the validity of theoretical analysis through the experiments and use Power-MOSFET to the switching devices of inverter circuit.

## 2. Characteristics analysis

#### 2.1 Configuration of the ZVS-HB type inverter

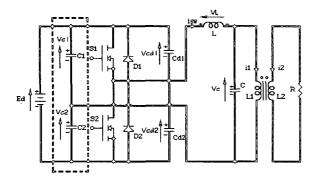

Fig. 1 shows the ZVS-HB type high frequency resonant inverter which has the variable capacitance of the DC voltage source separation capacitor(C1, C2) corresponding to dashed part of Fig. 1. The circuit scheme, as shown in Fig. 1, is composed of the resonant inverter which reduces turn on and off loss generating in the switching devices at switching using ZVS capacitors(Cd1, Cd2). The ZVS capacitors(Cd1, Cd2) are connected in parallel with the switches(S1, S2).

<sup>\*</sup> 正 會 員:嶺南大 電氣工學科 博士修了

<sup>\*\*</sup> 正 會 員:安東情報大學 電氣科 兼任教授・工博

<sup>\*\*\*</sup> 正 會 員:嶺南大 電氣電子工學部 教授・工博

<sup>&</sup>lt;sup>§</sup> 正 會 員: 東海大學 情報通信科 助教授・工博

<sup>§</sup> 正 會 員: 蔚山科學大學 電氣科 助教授・工博

接受日字: 1999年 11月 23日

Fig. 1 ZVS-HB type high frequency resonant inverter according to the variable capacitance of the DC voltage source separation capacitor

The switching devices(S1, S2) can be used in all switching devices with self-turn off function and the diodes(D1, D2) is used to by pass ineffective current flowing in the circuit that has been shown in the circuit operating characteristics.

The load of inverter can be employed by using discharge lamp like fluorescent light and also the circuit configuration of Fig. 1 consists of resonant reactor L, parallel resonant capacitor C across load, series capacitors(C1, C2) according to the variable capacitance of the DC voltage source separation capacitor and the switching devices(S1, S2), diodes(D1, D2), ZVS capacitors(Cd1, Cd2) across the switches(S1, S2), respectively. Since this ZVS operation is not generating turn off loss at switching in the event to the inductive load state which means that a phase angle of the switching current occurs later than a phase angle of the voltage across the load impedance, the disadvantage of the load resonant circuit is limited in the load region of the inductive load state.

In Fig. 1, the deciding equation of the minimum value( $t_{Dmin}$ )<sup>[6]</sup> of dead time in order to ZVS operation is as follows.

$$t_{Dmin} = \frac{2 \cdot E_d \cdot c_d}{I_{cd}} = \frac{2 \cdot E_d \cdot c_d}{I_m \sin \phi}$$

(1)

## 2.2 Circuit analysis

Table 1 Normalized parameter

|                       | Reference                                 | Normalized            |  |

|-----------------------|-------------------------------------------|-----------------------|--|

|                       | Values                                    | Values                |  |

| Voltage               | $E_d$                                     | $v^*_c(z)=v_c(t)/E_d$ |  |

| Current               | $I=E_d/Z_b$                               | $i^*(z)=i(t)/I_b$     |  |

| Time                  | $T_{sw}=1/f_{sw}$                         | $z=t/T_{sw}$          |  |

| Frequency             | $f_r = 1/2\pi\sqrt{L_bC_b}$               | $\mu = f_{sw}/f_r$    |  |

| Impedance             | $Z_b = 2\sqrt{L_b/C_b}$                   | $\lambda = R/Z_b$     |  |

| Power                 | $P_b$ = $E_d \cdot I_b$                   | $P^*(z)=P(t)/P_b$     |  |

| <remarks></remarks>   |                                           |                       |  |

| $f_{\mathrm{sw}}$ : ( | Operating Frequency of                    | of Inverter           |  |

| $T_o$ : O             | perating Period of Inv                    | verter                |  |

|                       | $C_s = C_1 = C_2$ , $C_d = C_{cd1} = C_0$ |                       |  |

$C_b = \frac{C \cdot C_s}{C + C_s}, \quad \alpha = C_s / C_s, \quad \beta = C / C_d$

The operation mode of Fig 1 divided into six mode by on off operation of the switches(S1, S2), diodes(D1, D2) and the charge and discharge of the ZVS capacitors(Cd1, Cd2) across switches(S1, S2). Also, the six mode as mentioned above can be expressed in four mode under the principle of circuit operation. In order to generalize of circuit analysis to the state equation of each mode, the circuit state equation have been introduced to normalized parameters shown in Table 1.

In the event to the capacitive load state, the switching loss at turn off is removed by zero current switching. But, the turn on switching operation has not expected to be safe operation in views of hardware side due to higher stress in the switching devices by generation of the higher switching loss and the arms short according to recovery time of diode.

The inverter operation of Fig. 1 can be expressed by the state equation (2), also can be illustrated by four mode like Eq(3)(4) and Eq(5)(6) according to on off state of the switches(S1, S2), diodes(D1, D2).

$$\frac{dX^*}{dz^*} = A^* \cdot X^* + B^* \cdot U$$

$$Y^* = C \cdot X^* \tag{2}$$

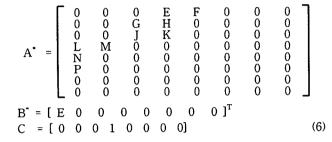

Where  $X^*=[i_{sw}^*(z), i_{1}^*(z), i_{2}^*(z), v_{c}^*(z), v_{cl}^*(z), v_{c2}^*(z), v_{cdl}^*(z), v_{cdl}^*(z)]$  U=[ 1 0 0 0 0 0 0], A\*, B\*, C of each mode is as follows.

The marks concerning  $A^{\bullet}$ ,  $B^{\bullet}$ , C of each mode is as follows:

$$\begin{split} E &= -\frac{4\pi}{\mu}, \, F = \frac{4\pi}{\mu}, \, G = -\frac{4\pi\lambda d}{\mu}, \\ H &= -\frac{4\pi b d}{\mu c}, \, J = \frac{4\pi\lambda a d}{\mu c}, \quad K = \frac{4\pi d}{\mu} \\ L &= (-\frac{\alpha}{\alpha+1})\frac{\pi}{\mu}, \quad M = -(-\frac{\alpha}{\alpha+1})\frac{\pi}{\mu}, \\ N &= -(\frac{1}{\alpha+1})\frac{\pi}{2\mu}, \qquad \qquad P = (\frac{1}{\alpha+1})\frac{\pi}{2\mu}, \\ Q &= (-\frac{\alpha}{\alpha+1})\frac{\pi\beta}{2\mu}, \, R = -(-\frac{\alpha}{\alpha+1})\frac{\pi\beta}{2\mu} \end{split}$$

## MODE 1

$$\mathbf{A}^{\star} = \begin{bmatrix} 0 & 0 & 0 & \mathbf{E} & \mathbf{F} & 0 & 0 & \mathbf{F} \\ 0 & 0 & \mathbf{G} & \mathbf{H} & 0 & 0 & 0 & 0 \\ 0 & 0 & \mathbf{J} & \mathbf{K} & 0 & 0 & 0 & 0 \\ \mathbf{L} & \mathbf{M} & 0 & 0 & 0 & 0 & 0 & 0 \\ \mathbf{N} & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \mathbf{P} & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \mathbf{Q} & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \mathbf{R} & 0 & 0 & 0 & 0 & 0 & 0 & 0 \end{bmatrix}^{\mathsf{T}}$$

$$\mathbf{C} = \begin{bmatrix} \mathbf{E} & 0 & 0 & 0 & 0 & 0 & 0 \end{bmatrix}^{\mathsf{T}} \tag{3}$$

## MODE 2

#### MODE 3

$$\mathbf{A}^{\star} = \begin{bmatrix} 0 & 0 & 0 & \mathbf{E} & 0 & \mathbf{E} & \mathbf{E} & 0 \\ 0 & 0 & \mathbf{G} & \mathbf{H} & 0 & 0 & 0 & 0 \\ 0 & 0 & \mathbf{J} & \mathbf{K} & 0 & 0 & 0 & 0 \\ \mathbf{L} & \mathbf{M} & 0 & 0 & 0 & 0 & 0 & 0 \\ \mathbf{N} & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \mathbf{P} & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \mathbf{Q} & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ \mathbf{R} & 0 & 0 & 0 & 0 & 0 & 0 & 0 \end{bmatrix}^{\mathsf{T}}$$

$$\mathbf{C} = \begin{bmatrix} \mathbf{F} & 0 & 0 & 0 & 0 & 0 & 0 \end{bmatrix}^{\mathsf{T}} \tag{5}$$

## MODE 4

#### 3. Characteristic estimation

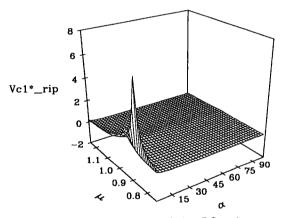

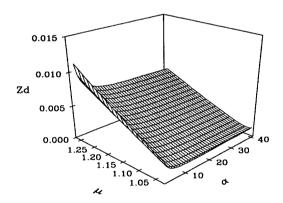

Fig. 2 The ripple Characteristics of the DC voltage source separation capacitor

Fig. 2 shows the ripple characteristics of the DC voltage source separation capacitor voltage( $v_{cl}^*_{ripple}$ ) according to the variation of ( $\mu$ ,  $\alpha$ ) with  $\lambda$ =7,  $\beta$ =40.

The ripple factor of the DC voltage source separation capacitor voltage is defined as follows.

$$RF = \frac{Vac}{Vdc} = \sqrt{\frac{V^2_{rms} - V^2_{dc}}{V^2_{dc}}} \times 100[\%]$$

(7)

In the event  $\alpha$  is small, as shown in Fig. 2, when we see from the DC voltage source to load side, Cs is not seen as the DC voltage source separation capacitor but the resonant capacitor

But, when  $\alpha$  is large, Cs is seen as the DC voltage source separation capacitor which have more dc components than ac components.

Accordingly, since the ripple factor is less than 0.1(%) with

$\alpha$ >30, Cs can be regard as the DC voltage source separation capacitor with the DC voltage of Ed/2.

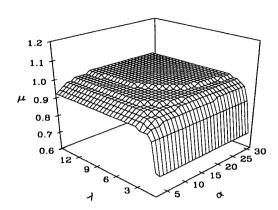

Fig. 3 The safety operating zone of ZVS-HB type inverter

Fig. 3 shows the safety operating zone of ZVS-HB type inverter with  $\alpha$ ,  $\mu$  and  $\lambda$  as parameters.

The safety operating zone of this paper can be achieved the inductive load state corresponding to ZVS operation condition which have enough charge discharge time in order to remove turn off loss at switching.

The space below the 3 dimension graph is unstable operating zone. But, the space above the 3 dimension graph indicates stable operating zone.

The safety operating zone of the proposed inverter, as shown in Fig. 3, is subjected to a lot of effect according to value of the normalized parameter  $\mu$ . Also, even though  $\alpha$  and  $\lambda$  is largely varied, the inverter stable operation in the value of less than  $\mu$ =0.7 can not be realized.

Fig. 4 Characteristics of Zd

Fig. 4 shows the charge and discharge time characteristics of ZVS capacitor(Zd) according to the variation of  $(\mu, \alpha)$  with  $\lambda$ =7 and  $\beta$ =40.

The characteristic values of Zd, as shown in Fig. 4, is decreased with  $\alpha$ .

Since the switching current is decreased with the increase of  $\alpha$  because the load impedance is increase.

When  $\alpha$  is more than 30, the value of Zd shows nearly constant value. The value of Zd is also increased with  $\mu$ .

Moreover, as long as  $\mu$  goes to the inductive load state, the value of Zd is increased with the decrease of switching current.

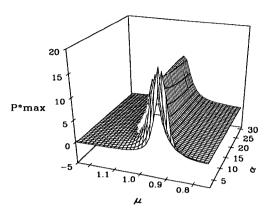

Fig. 5 Characteristics of the output power

Fig. 5 shows the output power according to the variation of  $(\mu, \alpha)$  with  $\lambda=7$  and  $\beta=40$ , As  $\alpha$  is decreased, as shown in Fig. 5, the output power is increased even up to the optimum operating point

According as  $\alpha$  is smaller, the switching current is increased because the load impedance is decreased as mentioned above. Also, according as  $\alpha$  is smaller, the ZVS operating zone and the safety operating zone of the proposed inverter is extended because the resonant frequency is increased by  $\alpha$ .

Moreover, in proportion as  $\alpha$  is increased, the optimum output power( $P_{max}^{\bullet}$ ) is found at around  $\mu = 1.0$ .

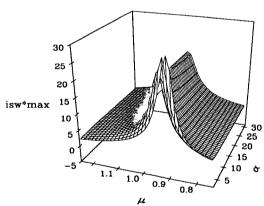

Fig. 6 Characteristics of the peak switch current

Fig. 6 shows the peak characteristics of the switching current( $i_{Su}$  max) according to the variation of ( $\mu$ ,  $\alpha$ ) with  $\beta$ =40 and  $\lambda$ =7. As  $\alpha$  is increased, as shown in Fig. 6, the peak value of the switching current is decreased. Also, the switching current and the resonant frequency of the proposed inverter is increased with the decrease of  $\alpha$  because the load impedance is decreased by  $\alpha$ .

Accordingly, we can understand that the safety operating zone with the inductive load state of ZVS-HB type inverter is extended. When  $\alpha$  is less than 30, the optimum operating point is found at  $\mu$ <1.0. When  $\alpha$  is more than 30, the optimum operating point is found at around  $\mu$ =1.0.

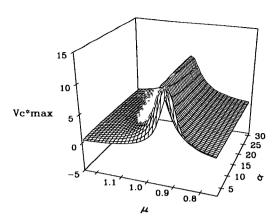

Fig. 7 Characteristics of the peak capacitor voltage

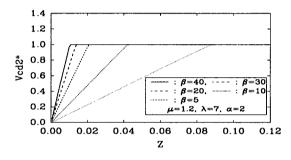

Fig. 8 The voltage across switch according to  $\beta$

Fig. 7 shows the peak characteristics of the capacitor voltage( $v_{c,max}^*$ ) according to the variation of ( $\mu$ ,  $\alpha$ ) with  $\beta$ =40 and  $\lambda$ =7.

The peak voltage of the resonant capacitor is decided by the integrated value of current flowing through the switching device. The characteristic values of Fig. 7 is used as the important data which decides the resisting voltage of the resonant capacitor in course of design.

Fig. 8 shows the voltage across the switch devices according to the variation of  $\beta$  with  $\beta$ =40 ,  $\lambda$ =7 and  $\alpha$ =2.

According as  $\beta$  is smaller, as shown in Fig. 8, we can understand that the slope of ZVS capacitor voltage across the switch is smoothed.

According as  $\beta$  is smaller, the charging and discharging time of the ZVS capacitor is long.

So, if the charging and discharging time of the ZVS capacitor is practically lengthened, it is important to select  $\beta$  with a proper slope because the switching loss is increased.

## 4. Circuit design

Based on the characteristic values obtained by the characteristic estimation through the circuit analysis, the design specification of the input voltage  $E_d(V)$ , the output power P(W) and the switching frequency  $f_{sw}(kHz)$  is established.

A method of the circuit design and operating characteristics of the inverter is as follows.

Step 1 Decision of  $(\lambda, \mu, \alpha, \beta, P^*_{max})$ : Reference to Fig. 5 and Fig. 8.

Step 2 Calculation of basic impedance

$$P^*(z) = \frac{P(t)}{P_b} = \frac{P(t)}{E_d^2/Z_b}, C_b = \frac{C \cdot C_s}{C + C_s}$$

$$Z_b = \frac{E_d^2 \cdot P^*(z)}{P(t)} = 2\sqrt{\frac{L_b}{C_b}}, \ \alpha = \frac{C_s}{C}, \ \beta = \frac{C}{C_d}$$

Step 3 Calculation of the circuit inherent frequency f<sub>1</sub>(kHz)

$$f_r = \frac{f_{sw}}{\mu} = \frac{1}{2\pi\sqrt{L_b C_b}}$$

Step 4 Calculation of  $L_b$ ,  $C_b$ ,  $C_s$  ( $C_1 = C_2$ ),  $C_d$  ( $C_{dJ} = C_{d2}$ )

Step 5 Calculation of the switch current and capacitor voltage

$i_{sumax}$ : Reference to Fig. 6.  $v_{cmax}$ : Reference to Fig. 7.

<The example of the circuit design>

Design specification :  $E_d$ =50(v) , P=500(W),  $f_{su}$ =35.5(kHz)

Step 1 In the characteristic curves of Fig. 5 and Fig. 8, Decision to  $\lambda = 7$ ,  $\mu = 0.964$   $\alpha = 2$ ,  $\beta = 40$ ,  $P^*_{max} = 7.862$

Step 2

$$Z_b = \frac{50^2 \times 7.862}{500} = 39.31$$

Step 3

$$f_r = \frac{35.5}{0.964} = 36.8, \sqrt{L_b C_b} = 4.324 \times 10^{-6}$$

Step 4 From the course of Step 2 ~ Step 3, Calculation of  $L_6$ =85( $\mu$ H), C=0.33( $\mu$ F),  $C_s$ =0.66( $\mu$ F)  $C_d$ =8.125(nF)

Table 2 Circuit parameters

| Circuit Parameter                               | Rating   | Circuit Parameter | Rating    |  |

|-------------------------------------------------|----------|-------------------|-----------|--|

| Input Voltage                                   | 50(V)    | Resonant          | 330(nF)   |  |

|                                                 |          | Capacitor(C)      | 640(V)    |  |

| Power-MOSFET                                    | 400(V)   | Resonant          | 85( µH)   |  |

| (IRFP 360)                                      | 28(A)    | Reactor(L)        |           |  |

| ZVS Capacitor(C <sub>d</sub> )                  | 8.25(nF) | Resonant          | 36.8(Khz) |  |

|                                                 | 900(V)   | Frequency         |           |  |

| DC voltage source 0.66<br>separate capacitor 90 | 0.66(μF) | iswmax            | 26(A)     |  |

|                                                 | 900(V)   | Vemax             | 375(V)    |  |

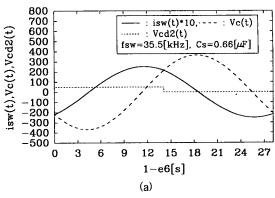

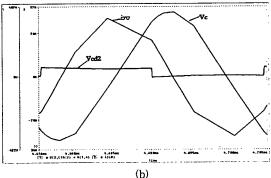

In the event to exercising simulation through the numerical analysis using the Runge-Kutta with the design values as mentioned above, under the steady state of the inverter, the Pspice and theoretical waveforms of the switch current(isw), the capacitor voltage(Vc) and the voltage across the switch(Vcd2) are shown in Fig. 9(a), (b) respectively.

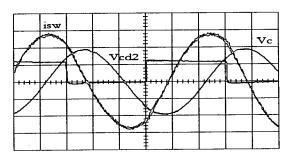

Fig. 10 shows the experimental waveforms of the switch current(isw), the capacitor voltage(Vc) and the voltage across the switch(Vcd2) through the experimental test in order to prove the validity of the theoretical analysis.

As shown in Fig. 9(a), (b) and Fig. 10, the result of the theoretical, Pspice and experimental waveforms are in a good agreement. Table 2. shows the circuit parameters of Fig. 1.

Fig. 9 Theoretical and Pspice waveforms

(Voltage(Vcd2): 40(V)/div, Voltage(Vc): 200(V)/div, Current: 10((A)/div)

Fig. 10 Experimental waveforms

#### 5. Conclusion

This paper presents the ZVS-HB type high frequency resonant inverter which has generally described by using normalized parameter in terms of characteristics according to the variable capacitance of the DC voltage source separation capacitor.

In the event the ratio( $\alpha$ ) of the DC voltage source separation capacitor and the resonant capacitor is varied, the optimum operating point is found at  $\mu$ <1.0 when  $\alpha$  is less than 30. The optimum operating point is found at around  $\mu$ =1.0 when  $\alpha$  is more than 30. Also, when  $\alpha$  is more than 30, since the ripple factor is less than 0.1(%), Cs can be seen as the DC voltage source separation capacitor with the DC voltage of Ed/2.

According as  $\alpha$  is smaller, the capacitance of the DC voltage source separation capacitor can be realized as the light weight and small size one.

In addition, according to the calculated characteristic values, a method of the circuit design and operating characteristics of the inverter is proposed.

Moreover, by result through experimental test using Power-MOSFET, we can conclude that the theoretical, Pspice and experimental waveforms are in a good agreement.

This proposed inverter shows that it can be practically used in future as power source system for the lighting equipment of discharge lamp, DC-DC converter etc

#### Reference

- [1] W. E. Frank et. al: "New Induction heating transformer", IEEE. vol. MAG18. No. 6. pp. 1752~1755, 1982.

- [2] T. F. Wu et. al: "Single-State Dimmer Eletronic Ballast with Unity Power Factor", IAS'96, vOL. 4. pp. 2141~2148, 1996.

- [3] T.Haneyoshi, A. Kawamura and R. G. Hoft, "Waveform compensation of PWM inverter with cyclic fluctuating loads," in the Proceedings the 1986 PESC Record, pp. 744~751.

- [4] A. Takeuchi et. al : "Zero-Voltage-Switching Controlled High Power-Factor Converter", PESC'96, Vol. 1, pp. 1859~1864, 1996.

- [5] Jong-Hae Kim, Dong-Hee Kim and Chae-Gyan Ro etc, "A study on the ZVS-SEPP type high frequency resonant inverter with induction heating jar(I)", Trans. KIEE. Vol. 48B, No. 2, pp. 69~74, FEB, 1999.

- [6] Byeong-Jae Min, Chae-Gyan Ro, Dong-Hee Kim, Jong-Hae Kim and Chang-Soo Moon, "Characteristic analysis and design of high frequency resonant inverter(SEPP type) using ZVS", Trans. KIPE. Vol. 2, No. 4, pp. 19~27, 12, 1997.

# 제 자 소 개

## 문 창 수 (文 昶 琇)

1964년 7월 9일생. 1990년 영남대 공대 전기공학과 졸업 1993년 영남대 공대 전기 공학과 졸업(석사). 영남대 공대 전기공학 과 박사수료, 현재 IR KOREA 과장

## 김 종 해 (金 鍾 海)

1968년 3월 11일생. 1944년 경일대 전기 공학과 졸업. 1966년 영남대 공대 전기공 학과 졸업(석사). 1996년~현재 영남대 전 기공학과 박사과정 수료. 경일대, 안동정 보대학 강사

Tel: 053-810-2488

E-mail: kjhassk@hanmail.net

## 오 승 훈 (吳 昇 勳)

1962년 10월 1일 생. 1989년 경일대 전기 공학과 졸업. 1991년 영남대 공대 전기공 학과 졸업(석사). 1997년 동 대학원 전기 공학과 졸업(공박). 1994년~현재 동해대 학 정보통신과 조교수

## 심 광 열 (沈 光 烈)

1961년 5월 27일생. 1983년 경남대 공대전기공학과 졸업. 1985년 영남대 대학원전기공학과 졸업(석사). 1990년 현대중공업(주)중전기연구소 선임연구원. 현재 울산과학대학 전기과 조교수

### 김 동 희 (金 東 熙)

1950년 11월 20일생. 1973년 영남대 공대 전기공학과 졸업. 1975년 동 대학원 전기 공학과 졸업(석사). 1987년 Kobe 대학 졸 업(공박). 1987~1989년 한국전기연구소 전력전자 연구부장. 현재 영남대 공대 전 기전자공학부 교수

Tel: 053-810-2488

E-mail: dohkim@ynucc.yeungnam.ac.kr

#### 민 병 재 (閔 丙 才)

1953년 8월 24일생. 1979년 영남대 공대 전기공학과 졸업. 1982년 동 대학원 전기 공학과 졸업(석사). 1997년 동 대학원 전 기공학과 졸업(공박). 1994년~현재 안동 정보대학 전기과 조교수