## 병목현상 제거를 위한 디지틀 신호처리에 관한 연구

# A Study on the Digital Signal Processing for Removing the Bottle-neck Effect

고 영 욱\*, 김 성 곤\*\*, 김 환 용\*

(Young Oog Ko\*, Sung Gon Kim\*\*, Hwan Yong Kim\*)

※이 논문은 1997년도 원광대학교 교내연구비 지원에 의해 연구되었음.

요 약

본 논문에서는 HDTV 비디오 신호를 처리함에 있어 신호의 병목현상을 없애주고 신호의 원활한 처리를 위해 새로운 알고리듬을 적용하여 54MHz의 동작 주파수를 갖는 패커를 제안하고 설계하였다. 또한 제안된 패커의 성능을 검증하기 위해 조합논리를 이용한 ROM 테이블 구조를 갖는 DCT 계수 부호화부를 함께 설계하므로써 DCT 계수 부호화부의 출력을 제안된 패커의 입력 데이타로 사용하였다. 본 논문의 회로는 VHDL 코드를 이용하였고 SYNOPSYS tool의 0.65 μm 공정을 이용한 모델링과 시뮬레이션을 수행하였다.

#### **ABSTRACT**

In this thesis, a packer is proposed and designed for removing the bottle-neck effect and easy signal processing using a new algorithm with the operation frequency of 54MHz. To verify the performance of the proposed packer, DCT coefficient encoding block with ROM table using a combinational logic is designed and its output data are used the input data of the packer. Circuits in this thesis are designed by using VHDL code and its modeling and simulation are performed by SYNOPSYS tool using  $0.65 \,\mu$ m rule.

#### I. 서 론

차세대 TV라 불라는 HDTV(High Definition TV:고선명 TV)의 경우 비디오 데이타는 국제 표준인 MPEG-II의 비디오 스트림 산택스를 채용했으며 오디오 데이타는 디지를 오디오 압축(AC-3)을 표준으로 채택하여 현장감있는 화면과 서라운드 음향을 가정까지 전달할 수 있다. 디지를 HDTV 신호의 수평, 수직 해상도는 NTSC(National Television System Committee) 신호의 약 2배가 되며 이 신호의 전송이나 저장을 위해서는 디지를 NTSC 선호의 전송를 보다 최소한 다섯 배가 요구된다<sup>II)</sup>. 이처럼 디지를 HDTV의 경우 데이타량이 매우 방대하므로 신호를 패킷(packet)으로 전송하는데 신호의 패킹(packing)시 신호의 병목현상(bottle-neck effect)과 오류 발생이 빈번히 발생되어 현재이러한 문제점을 해결하기 위해 다방면의 연구가 진행되고 있다.

따라서 본 논문에서는 HDTV 신호 중 비디오 신호를 처

리함에 있어 패킷(packet) 전송시 신호의 병목현상을 없애 주고 전송전 신호의 에러를 방지하므로써 신호의 원활한 처리를 돕기 위해 신호의 패킹에 관한 새로운 알고리듬을 제 안하고 또한 이를 적용한 엔트로피(entropy) 부호화 모듈의 패커(packer)를 제안한다. 기존의 패커는 가변길이 코드를 32비트의 고정길이로 패킹(packing)하며 배릴 쉬프터(barrel shifter)를 두 개 사용하는 기본적인 구조를 갖고 있 다. 본 논문에서 제안하는 패커는 54MHz의 동작 주파수 를 갖도록 하였으며 이러한 동작 주파수에서 배럴 쉬프 터를 하나만 사용하므로써 제어 신호와 데이타 신호에서 발생할 수 있는 에러의 확률이 자숭배로 늘어나는 단점 을 보완하고자 하였으며 이물 위해 기존의 32비트를 24 비트로 패킹하도록 포맷시켰다. 54MHz의 패커를 27MHz 의 MPEG-Ⅱ의 스트림 신택스를 채용하고 있는 HDTV 시스템에서 사용하기 위해서는 27MHz를 서로 exclusive-OR하므로써 54MHz의 클릭 주파수를 얻을 수 있으므로 별도의 클릭 주파수를 사용하지 않아도 된다.

또한 본 논문에서 설계한 패커의 성능을 검증하기 위해 기존의 PROM을 이용한 DCT 계수 부호화부 대신 조합논리(combinational logic)를 사용한 ROM 구조의 DCT

<sup>\*</sup> 원광대학교 전자공학과

<sup>\*\*</sup> 고창기능대학 정보통신학과 접수일자: 1998년 9월 17일

계수 부호화부를 설계한다. DCT 계수 부호화부의 가변길이 부호화는 허프만 코딩을 이용하며, 양자화된 후 엔트로피 부호화모듈로 입력되는 AC 계수와 DC 계수를 24 비트의 가변길이 코드로 출력하도록 하므로써 이 출력을 패커의 입력 데이타로 사용할 수 있도록 하였다.

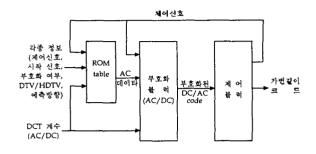

#### II. HDTV 인코더와 엔트로피 부호화모듈

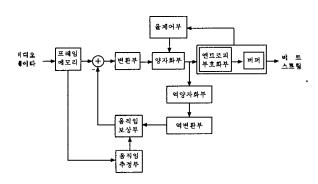

HDTV 시스템은 비디오 데이타, 오디오 데이타 그리고 부수적인 데이타를 입력으로 받아 코딩과 압축을 행한 후 각 데이타를 하나의 데이타 스트림 패킷으로 다중화시켜 채널 코딩과 변조 과정을 통해 수신기에 전송하는 구조로 되어있다<sup>12,34</sup>. 그림 1의 비디오 인코더는 비디오 데이타를 입력으로 받아 코딩과 압축을 행한 후 엔트로피 부호화를 거쳐 비트 스트림으로 전송시키는 기능을 수행한다.

프레임 메모리에서는 비디오 데이타를 프레임별로 저 장하고, 변환부에서는 데이타를 움직임 보상부에서 제공 되는 기준 영상 데이타와 비교하여 차이 값을 계산하여 DCT 변환을 수행한다. DCT 변환된 결과는 양자화부에 서 변환된 신호의 통계적 성질과 시각의 특성을 이용하 여 양자화되고 양자화된 데이타는 역양자화부에서 역양 자화를 행한 후 역변환부에서 역DCT(inverse DCT) 변환 을 거쳐 움직임 보상부로 전달된다. 움직임 추정부는 매 크로 불럭 단위로 프레임간 움직임 벡터를 추정하여 움 직임 보상부로 전달하고, 움직임 보상부는 프레임간 차분 부호화를 위해 필요한 기준 프레임 데이타를 제공한다. 엔트로피 부호화모듈에서 양자화된 데이타를 가변길아 부호화하여 그 결과를 버퍼에 저장한 후 비트 스트림으 로 출력한다. 그리고 율제어부는 출력 버퍼의 넘침이나 모자람이 발생하지 않고 영상 부호화 출력 비트율을 일 정하게 유지할 수 있도록 양자화 파라미터를 제어한다<sup>[4]</sup>.

그림 1. 비디오 인코더 블럭도 Fig. 1. Video encoder block diagram.

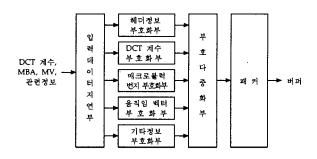

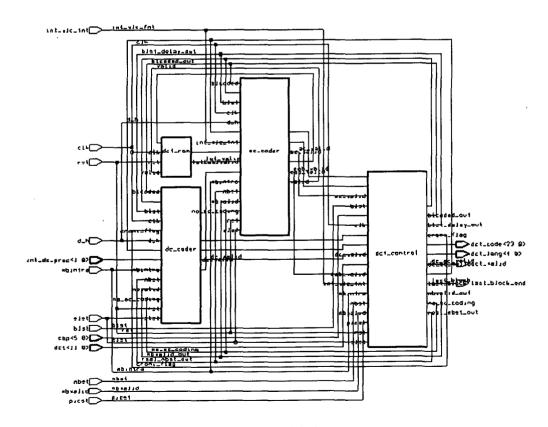

그림 1의 디지를 비디오 인코더 중 엔트로피 부호화모들의 블럭도는 그림 2와 같다. 엔트로피 부호화모들은 매크로 블럭 번지, 움직임 벡터, DCT 계수 등을 각 하위 블럭에서 가변길이 부호화하여 MPEG-II 비디오 비트 스트림 신택스의 계층 구조대로 나열한 다음 고정길이로 바

꾼다<sup>[5,6]</sup>. 부호화를 수행하는 하위 불력액는 해더 정보 부호화부, DCT 계수 부호화부, 매크로 불력 번지 부호화부, 움직임 벡터 부호화부에서 출력되는 코드들은 좌측정렬(left align)되어 있다. 그리고 입력 데이타 지연부에서는 서로 다른 매크로 불력에 해당하는 매크로 불력 주소, 움직임 벡터, 양자화 계수를 같은 매크로 불력 시점에서 출력되도록 한다. 부호 다중화부는 헤더 청보 부호화부, DCT 계수부호화부, 매크로 불력 주소 부호화부 그리고 기타 정보부호화부에서 공통적으로 출력되는 부호, 부호의 유효 비트길이, 부호의 유효 시간구간 정보들을 신택스의 구조애 맞도록 재배열한다. 그리고 패커는 부호 다중화부에서 출력되는 가변길이 코드를 고정길이 데이타로 바꾸어 쓰기클릭과 함께 버퍼로 전달하는 기능을 수행한다<sup>[5]</sup>.

그림 2. 엔트로피 부호화모듈 블럭도

Fig. 2. Entropy encoding module block diagram.

#### III. 새로운 알고리듬을 적용한 패커

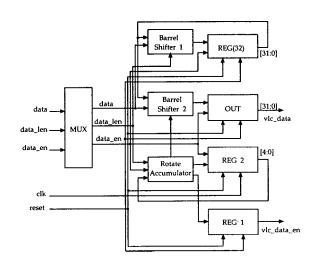

기존의 패커는 그림 3과 같이 MUX, Accumulator, 배럴 쉬프터 2개 그리고 레지스터들로 구성이 되어 있고 출력 은 부호화된 고정길이의 32비트이다.

그램 3. 기존의 패커 블럭도

Fig. 3. Conventional packer block diagram.

MUX에서는 입력으로 받아들인 데이타, 데이타의 유효 길이, 테이타의 유효신호를 muxing해 주는 역할을 하는 부분으로 유효 신호가 '1'인 동안 해당 데이타와 데이타 의 길이 그리고 각각의 레지스터들을 로드하기위한 enable 신호를 출력해준다. rotate accumulator는 32비트의 데이타 로 패킹되기 위해 서로 붙여지는데 데이타들의 누적된 길 이를 계산하는 부분으로 쉬프트한 횟수를 배럴 쉬프터에 전달하므로써 데이타의 유효 길이를 알 수 있도록 한다. 레 지스터는 이전에 입력된 데이타와 현재 입력된 데이타를 32비트 단위로 패킹하기 위해 LSB 쪽으로 쉬프트된 이 전 데이타를 저장하고 이 값을 다시 배럴 쉬프터의 입력 으로 전달한다. 그 밖의 레지스터는 출력될 데이타를 임 시로 저장하거나 출력되는 데이타가 유효한지의 여부를 저장하는 역할율 한다. 두 개의 배럴 쉬프터는 입력된 데 이타를 32비트 단위로 패킹하기 위해 이전에 입력된 데이 타와 현재 입력된 데이타를 붙여주는 역할을 하는 부분으 로 다량의 데이타를 처리해야하는 디지를 HDTV 시스템에 서 입력된 데이타를 두 개의 배럴 쉬프터에서 서로 나눠 병렬로 패킹함으로 인해 하나의 배털 쉬프터를 사용하였을 경우보다 데이타의 병목 현상 및 오류가 발생할 확률이 자숭배로 늘어난다. 이러한 기존의 단점을 보완하고자 본 논문에서는 54MHz의 동작 주파수를 갖으며 배럴 쉬프터

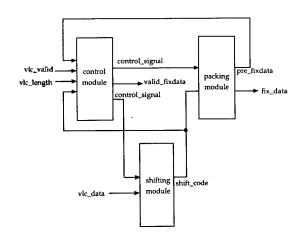

를 하나만 사용하므로써 제어 신호와 데이타 신호에서 발생할 수 있는 에러의 확률을 반으로 줄였으며 이를 위 해 기존의 32비트를 24비트로 패킹하도록 포맷시켰다. 그 림 4는 control, packing, shifting 모듈 등 세 개의 모듈로 구성된 본 논문에서 제안한 패커의 블록도이다.

그림 4. 제안된 패커 블럭도 Fig. 4. Proposed packer block diagram.

그림 5. 패커 회로 Fig. 5. Packer circuit.

그림 5는 설계된 패커와 회로이다. 그림 4의 패커 불리도와 같이 control 모듈, packing 모듈, barrel\_shifting 모듈 등 세 개의 모듈로 구성되었다. 입력으로는 코드의 스타트 플래그, 부호화된 가변길이 코드, 가변길이 코드의 유효 길이를 받아 패킹된 고정길이 코드, 고정길이 코드에 대한 유효신호를 최종 출력한다.

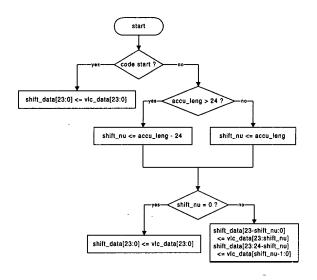

설계된 패커는 control 모듈, barrel\_shifting 모듈, packing 모듈 등 세 개의 모듈로 구성되어 있다. control 모듈에서는 필요한 쉬프트 횟수가 얼마인지를 계산하여 barrel\_shifting 모듈로 보내주고 비트 접합에 필요한 제어 신호를 packing 모듈로 보내준다. 또한 유효길이를 누적하여 24가 되면 코드를 출력할 것을 알리며 패커 관련 재어 신호를 생성한다. barrel\_shifting 모듈에서는 비트 접합을 위하여 입력되는 유효신호를 배럴 쉬프트시킨다. 입력되는 가변길이 코드를 vic\_data, 쉬프트된 데이타를 shift\_data, 쉬프트 횟수를 shift\_nu, 누적된 길이 수를 accu\_leng, 출력되는 고정길이 코드를 fix\_data라 할 때 barrel\_shifting 모듈에서 알고리듬의 흐름도는 그림 6과 같다.

그림 6. barrel\_shifting 모듈의 알고라돔 호름도 Fig. 6. Algorithm flow chart of barrel\_shifting module.

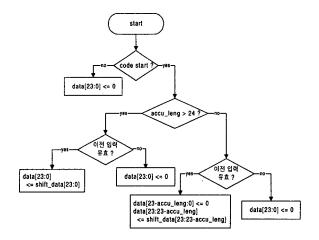

packing 모듈에서는 쉬프트된 코드를 패킹하여 고정길이의 24비트 코드를 최종 출력한다. packing 모듈은 pack\_1과 pack\_2 등 두 개의 프로새서로 구성된다. pack\_1 프로세서에서는 pack\_2 프로세서에서 최종 접합에 필요한 각종 제어 플래그를 생성하며 pack\_2 프로세서는 pack\_1 프로세서에서 생성된 제어 신호를 이용하여 가변길이 코드를 최종 접합하여 24 비트의 고정길이 코드로 출력한다. 고정길이 코드로 접합하기 이전의 임시 데이타를 data, 접합할 값을 contact라 할 때 pack\_1과 pack\_2 프로세서의 알고리듬 흐름도는 그림 7과 그림 8에 나타나 있다.

그림 7, pack\_1 프로세서의 알고리듬 호름도 Fig, 7, Algorithm flow chart of pack\_1 processor.

그림 8. pack\_2 프로세서의 알고리듬 흐름도 Fig. 8. Algorithm flow chart of pack\_2 processor.

#### IV. 성능 검증을 위한 DCT 계수 부호화부의 설계

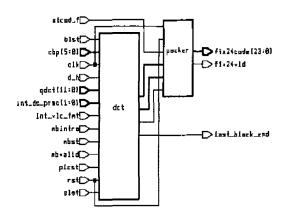

Ⅲ장에서 설계한 패커의 성능 검증 즉, 패커의 입력으로 사용할 데이타를 위해 DCT 계수 부호화부를 설계하였다. DCT 계수 부호화부에서는 양자화된 AC와 DC 계수를 입력으로 받아 가변길이로 부호화하여 출력하므로써 이 출력 데이타를 패커의 입력 데이타로 사용한다. DCT 계수 부호화부의 불력도는 그림 9와 같다.

DCT 계수는 해당 매크로 블럭이 intra 블럭인지 또는 non-intra 블럭인지에 따라 DC 코드와 AC 코드로 구분되어 부호화되고 블럭의 맨 마지막 계수의 부호 뒤에는 EOB 코드가 뒤따른다. intra 매크로 블럭은 DC 계수와 AC 계수 부호로 구성되고 non-intra 매크로 블럭은 AC 계수 부호로만 구성된다<sup>78</sup>. DC 계수는 intra-dc-precision에

따라 8, 9, 10, 11 비트 중 하나의 비트 수를 사용하여 표 현할 수 있고 다음 식(1)에 의해 차분 값을 구한다<sup>19</sup>.

그림 9. DCT 계수 부호화부 블럭도 Fig. 9. DCT coefficient encoding block diagram.

$$DIFF = DC_i - DC_{i-1} \tag{1}$$

여기에서 DIFF는 차분 값이고 DC;는 현재 매크로 블럭의 DC 계수 값이며 DC;—1는 이전 매크로 블럭의 DC 계수 값은 나타낸다. 구해진 DC 차분 값을 부호화하는 방법은 먼저 DIFF 값에 따라 앤트로피 코드에 차분 크기 범주를 구하여 가변길이 부호화한다. 차분 크기 범주가 구해지면 해당 범주를 나타내는 수만큼의 비트를 이용하여 실제 차분 크기를 앤트로피 코드에 의해 고정

길이 부호화한다. 이 고정길이 부호를 부가 코드(additional code)라 한다. 차분 크기 범주를 나타내는 가변길이 부호 (size code)가 DC 부호의 상위 비트를 구성하고 실제 차분 크기를 나타내는 고정길이 부호(additional code)는 DC 부호의 하위 비트를 구성한다<sup>(10)</sup>. AC 제수는 한 블릭 내에서의 AC 계수 값을 (run, level)의 조합으로 나타낸 후 AC 계수에 대한 엔트로피 코드에 의해 부호화한다<sup>(9)</sup>.

설계된 DCT 계수 부호화부는 dct\_control, dct\_rom, ac\_coder, dc\_coder 모듈 등 네 개의 모듈로 구성하였다. dct\_control 모듈은 DCT 계수 부호화부 전체의 제어 신호를 발생시키고 최종 DCT 코드물 출력하며 여섯 개의 프로세서로 구성된다. dct\_rom 모듈은 ac\_coder 모듈로부터 테이블을 참고하기 위해 address와 valid 신호를 주면해당 address 값에 따라 ROM 테이블에 저장된 데이타를 출력한다. ac\_coding 모듈은 각 불력의 AC 계수 값을 받아 AC 코딩을 하며 세 개의 프로세서로 구성된다. dc\_coder 모듈은 DC 코딩 할 각 불력의 첫 번째 값을 받아 DC 코딩을 하며 두 개의 프로세서로 구성이 된다.

그림 10은 설계된 DCT 계수 부호화부의 회로이다. 그 림 9의 DCT 계수 부호화부의 불력도와 비교하면 ROM 태이불은 dct\_rom에, 제어 불력은 dct\_control에 해당하며 부호화 불력은 ac\_coder와 dc\_coder로 나누어 설계하였다.

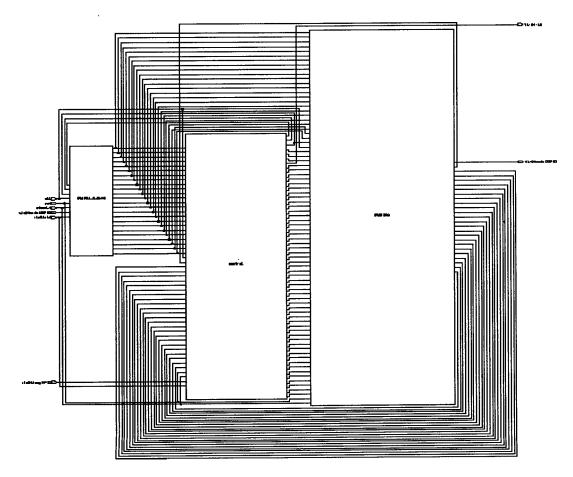

본 논문에서 설계한 패커와 DCT 계수 부호화부의 전체 회로는 그림 11과 같다. DCT 계수 부호화부에서는 스타트 신호인 block\_start, mblock\_start, picture\_start 신

그림 10. DCT 걔수 부호화부 회로

Fig. 10. DCT coefficient encoding block circuit.

그림 11. DCT 계수 부호화부와 패커 회로

Fig. 11, DCT coefficient encoding block and packer circuit.

호와 함께 앙자화된 AC 계수와 DC 계수를 quant\_dct[11:0]을 통해 업력으로 받아 가변길이 부호화를 시켜 24비트의 가변길이 코드를 출력한다. 패커는 DCT 계수 부호화부에서 출력된 24비트의 가변길이 코드를 패커에서 업력데이타로 받아 고정길이의 24비트 코드로 변환된 fix24code [23:0]과 이에 대한 유효산호인 fix24vld를 출력한다.

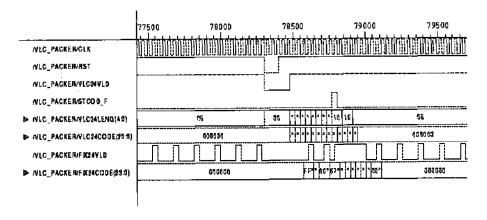

#### V. 모의실험 및 검증

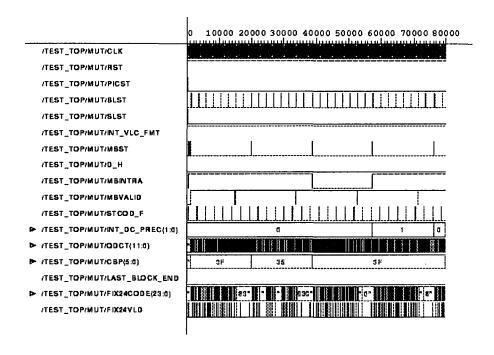

패커에 대한 모의실험 결과는 그림 12와 같다. vlc\_code [23:0], vlc\_length[4:0], vlc\_valid는 DCT 계수 부호화부에서 최종 부호화된 출력이며 이러한 신호들을 코드의 시작신호인 start\_code\_flag 신호와 함께 입력으로 받아 고정 길이의 fix24code[23:0]과 fix24vld의 유효신호를 출력한다.

그림 12. 패커의 모의실험 Fig. 12. Simulation of packer.

그림 13. DCT 계수 부호화무의 모의실험 Fig. 13. Simulation of DCT coefficient encoding block.

그림 13은 DCT 계수 부호화부에 대한 모의실험 결과 이다. 각종 스타트 신호, 매크로 블럭의 intra 여부, 매크 로 블럭의 유효 신호, AC와 DC 계수에 대한 양자화된 DCT 계수, intra DC 계수의 예측, 부호화된 블럭 패턴을 입력으로 받아 DCT 계수가 유효한지의 여부, AC와 DC 계수의 부호화된 코드와 이에 대한 코드의 유효 길이를 표현하는 코드 길이의 최종 출력을 확인할 수 있었다.

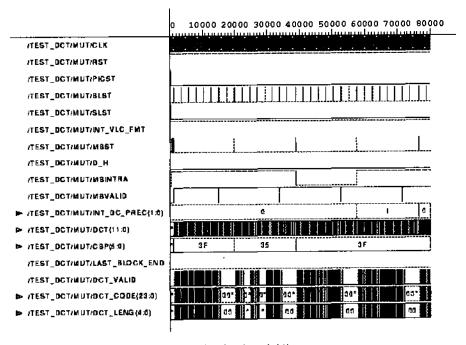

그림 14는 설계된 DCT 계수 부호화부와 패커에 대한 전체 회로를 80,000ms까지 모의실험한 결과이다. DCT 계 수 부호화부는 block\_start, mblock\_start, picture\_start,

그림 14, DCT 계수 부호화부와 패커 회로의 모의살힘 Fig. 14, Simulation of DCT coefficient encoding block and packer circuit.

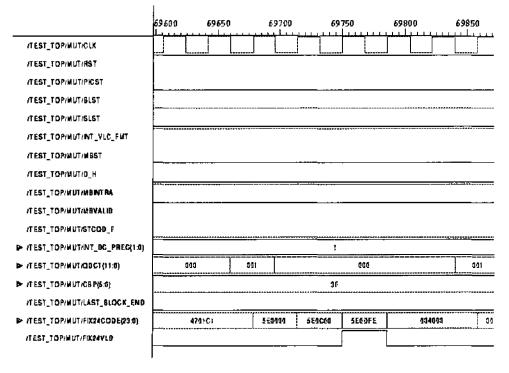

그림 15, DCT 계수 부호화부와 패커 최로의 자세한 모의실험 Fig. 15, Detail simulation of DCT coefficient encoding block and packer circuit.

slice\_start 등의 스타트 신호, 매크로 블릭의 유효 신호 (valid\_mblock), 부호화된 블릭의 패턴(coded\_block\_pattern [5:0]) 등의 제어신호와 intra 블릭 DC 제수의 예측(int\_dc\_prediction[1:0]), 매크로 블릭의 intra 여부(mblock\_intra), intra 블릭의 포맷(int\_vlc\_format), DCT 변환 후 양자화된 DCT 계수(quant\_dct[11:0]) 등을 입력으로 받아 AC와 DC 계수를 가변길이로 부호화하여 부호화된 코드와 이에 대한 유효 길이를 출력하므로써 이 출력을 패커의 입력으로 사용하도록 하였다. 패커에서는 AC 계수와 DC 계수에 대해 가변길이로 부호화된 24비트를 제어신호와 함께 24비트의 고정길이로 패킹하여 fix24code[23:0]과 이에 대한 유효 신호인 fix24vld를 출력한다.

그림 15는 그림 14의 전체 회로에 대한 모의실험 중 69,600ns에서 69,870ns까지의 자세한 결과를 보여준다.

#### VI. 결 론

본 논문에서는 HDTV 비디오 신호를 처리함에 있어 신 호의 병목현상을 없애기 위해 패커의 동작 주파수를 54 MHz로 하였으며, 54MHz의 동작 주파수에서 기존의 구 조를 갖는 배럴 쉬프터를 사용함에 있어서의 문제점 즉, 2개의 배럴 쉬프터를 사용하므로써 발생할 수 있는 제어 및 데이타 신호의 에러 확률이 자숭배로 중가하는 단점 을 보완하기 위해 한 개의 배럴 쉬프터를 사용하고 데이 타를 24비트로 포맷시키는 새로운 알고리듬을 적용한 패 커를 제안하였다. 패커에 해당하는 54MHz를 얻기 위해 HDTV 시스템의 주클럭인 27MHz를 EX-OR함으로써 서 로 다른 클럭 두 개를 사용하지 않아도 될 것이다. 또한 제안된 패커의 성능을 검증하기 위해 조합논리를 이용한 ROM 테이블 구조를 갖는 DCT 계수 부호화부를 설계하 여 앤트로피 부호화모듈로 입력되는 AC 계수와 DC 계 수를 24비트의 가변길이 코드로 출력하도록 하므로써 이 출력을 패커의 입력 데이타로 사용하였다. 본 논문에서 설계한 패커와 DCT 계수 부호화부는 VHDL 코드를 이용 하였고 SYNOPSYS tool의 0.65 μm 공정을 이용한 모델 링과 시뮬레이션을 수행하여 DCT 계수 부호화부로 입력 되는 양자화된 AC 계수와 DC 계수를 가변길이 코드로 엔트로피 부호화한 후 패커에서 고정길이 코드로 효율적 인 패킹을 확인하였다.

### 참고문헌

- Erigid Gavin, "Digital terrestrial high-definition television -What's good for America in good Europe", Telecommunication Journal, Vol. 60-VI, 1993.

- ISO-IEC JTC/SC2.WG11, "Generic Coding of Moving Pictures and Associated Audio ISO/IEC 13818-1 MPEG-2 Video International Standard", Mar., 1995.

- ISO-IEC JTC/SC2.WG11, "Generic Coding of Moving Pictures and Associated Audio ISO/IEC 13818-2 MPEG-2 Video International Standard", Mar., 1995.

- 4. 공종필의 2인, "MPEG DCT 계수의 특장을 이용한 효율적인 VLC/VLD의 VLSI 설계", 대한전자공학회 논문집, Vol. 33, B면, No. 1, pp. 79-86, 1996.

- Shaw-Min Lei et al., "An entropy coding system for digital HDTV application", IEEE Trans. on Circuits and Systems for Video Technology, Vol. 1, No. 1, pp. 147-155, Mar., 1991.

- "Video codec for audio visual services at px64Kbits/s", CCITT Recommendation H.261, 1990.

- K. R. Rao, J. J. Hwang, "Techniques & Standards for Image Video & Audio Coding", Prentice Hall 1996.

- Louis Torres, Murat Kunt, "Video Coding: The second generation approach", Kluwer Academy Publishers, 1996.

- P. Pancha, M. E. Zarki, "MPEG coding for variable bit rate video Transmission", IEEE Comm. Magazine, pp. 54-66, 1994.

- Byeung Jeon, Juha Park, Jechang Jeong, "Application of Dynamic Huffman Coding to Image Sequence Compression", SPIE Vol. 2308, pp. 1636-1647, Aug., 1994.

▲고 영 욱(Young Oog Ko) 1968년 2월 4일생

1996년 2월:원광대학교 전자공학과

(공학사)

1998년 2월:원광대학교 전자공학과

(공학석사)

1998년 3월~현재:원광대학교 전자

공학과 박사과정 재학중

※주관심분야:이동통신용 회로 설계,

VLSI 설계, DSP

E-mail: ko@gaebyok.wonkwang.ac.kr

▲김 성 곤(Sung Gon Kim) 1968년 7월 5일생

1991년 2월: 원광대학교 전자공학과 (공학사)

1996년 2월: 원광대학교 전자공학과 (공학석사)

1996년 3월~현재;원광대학교 전자

공학과 박사과정 재학중

1996년 3월~현재:고창기능대학 정

보통신학과 전임강사

※주관심분야: DSP, VLSI 설계, 디지틀 통신

E-mail: ksg@kochang.ac.kr

▲김 환 용(Hwan Yong Kim) 한국음향학회지 제17권 5호 참조

E-mail: hykim@wonnms.wonkwang.ac.kr