# CMOS Microcontroller IC와 고밀도 원형모양SOI 마이크로센서의 단일집적

## A Monolithic Integration with A High Density Circular-Shape SOI Microsensor and CMOS Microcontroller IC

李明玉\*,文良浩\*\*

(Mike Myung-Ok Lee and Yang-Ho Moon)

#### Abstract

It is well-known that rectangular bulk-Si sensors prepared by etch or epi etch-stop micromachining technology are already in practical use today, but the conventional bulk-Si sensor shows some drawbacks such as large chip size and limited applications as silicon sensor device is to be miniaturized. We consider a circular-shape SOI(Silicon-On-Insulator) micro-cavity technology to facilitate multiple sensors on very small chip, to make device easier to package than conventional sensor like pressure sensor and to provide very high over-pressure capability. This paper demonstrates the cross-functional results for stress analyses(targeting 5µm deflection and 100Mh stress as maximum at various applicable pressure ranges), for finding permissible diaphragm dimension by output sensitivity, and piezoresistive sensor theory from two-type SOI structures where the double SOI structure shows the most feasible deflection and small stress at various ambient pressures. Those results can be compared with the ones of circular-shape bulk-Si based sensor<sup>[17]</sup>. The SOI micro-cavity formed the sensors is promising to integrate with calibration, gain stage and controller unit plus high current/high voltage CMOS drivers onto monolithic chip. Key Words: iSOC, Circular SOI Sensor, Micro-cavity technology. IC compatible MCU, Residual stress, Transducer, Piezoresistance, Smart Sensor.

## I. Introduction

As communication era comes in reality, SOC(System On Chip) in microelectronics is not only

an emerging issue for multiple applications, but iMEMS, the combination of sensor and the SOC, has attracted many researchers for several years, iSOC(integrated SOC) in  $\mu$ -electronics with CMOS logics and embedded memory where CMOS logic is leading the technology against memory technology is quickly evolving from ASICs(Application Specific Integrated Circuits) as various applications are required, and the combination of the iSOC and non-electronic systems, iMEMS, has attracted university and industrial

(Dept. of Information & Communication, Dongshin Univ.)

\*\* 三星電氣株式會社

(Samsung Electro-Mechanics Co.)

接受日:1997年7月3日,修正完了日:1997년11月10日

<sup>\*</sup> 東新大學校 情報通信工學科

researchers for many years. These interfaces, rapidly observed using integrated bulk-Si sensors microactuators, are growing in more higher value added sophistication, Multimedia, portable communications and automotive/industrial markets can benefit from the integration of macros functions of diverse multi-purpose sensor on a chip due to the power and cost reductions[1]. Many companies are involved in producing IC compatible sensors based on standard sensor processes such as a timed cavity etch or Direct (DWB) Wafer Bonding oxide-etch electrochemical EPI etch stop, but those processes are difficult to produce thin diaphragm and to handle and process through diffusion/photo steps and they need very aggressive etch. And then IC-compatible cavity-last etch stop processes look promising, but limits initial cost, chip size capability and high over-pressure. Lately bulk-Si micro-cavity technology micromachining technologies is promising for small chip size capability<sup>[23]</sup> since it facilitates multiple sensors on one chip for absolute plus differential pressure, makes device easier to package than conventional sensor like pressure sensor<sup>[4,5]</sup> and also makes diaphragm be any shape such as circular to save chip space. In this paper, current trends on micromachining technologies such as the micro-cavity process, application areas of intelligent pressure sensors and IC-compatible smart sensors chips will be briefly mentioned, and some advantages of SOI-based sensors are simulated for fundamental stress analysis along with the residual stresses as a function of the temperature for varying cavity pressure where radius, depth, and membrane of the cavity dimensions are 400, 0.1/10/0.1, and  $10\mu m$  as the target<sup>[12,16]</sup>, respectively. Those structures for micro-cavity technology of bulk-Si and SOI structures are shown in Fig. 1.

## II. Semiconductor Integration and Technology Migration

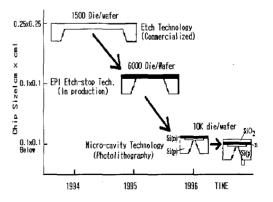

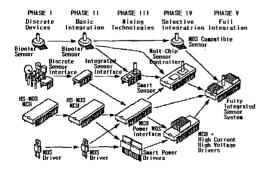

Trends on the micromachining technology and

main process sequences of recent micro-cavity technology are shown in Fig. 1(a) and (b). respectively. It is essential to determine a target sensing position and IC interface<sup>[6-8]</sup> from sensing elements such as piezoresistor, transducer and/or pulse after constructing proper diaphragm. Starting with the piezoresistor's physics, piezoresistance in silicon is changed by conductivity of a material in response to an applied stress. When silicon is stressed, the mobility of the majority carrier(holes) decreases due to increased scattering of carriers. This situation is quite similar to normal silicon implantation or injection into silicon substrate. It is important to understand mechanical properties such as Young's modulus and residual stress for the pure bulk-Si or SOI structure<sup>[9-11]</sup> because piezoresistive sensors can be fabricated using two types: one by pure bulk-Si structure and the other by SOI structure which consists of various thin films such as Si. SiO<sub>2</sub>. Si<sub>3</sub>N<sub>4</sub> and Al<sub>2</sub>O<sub>3</sub> Unlike standard sensor process sequences, the micro-cavity technology usually executes the cavity as the last etch after passivation formation for single-side polished 4" epi wafer. It is well-known that device characteristics such as sensitivity and resonance frequency, which strongly depend on thin film mechanical properties<sup>[13-15]</sup>, are important. In the MEMs world, it would

(a)

Fig. 1. (a) Trend on bulk-Si micromachining technology.

(b) Process for bulk-Si micro- cavity technology.

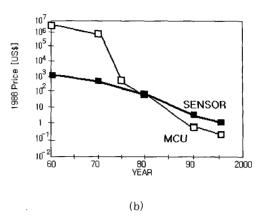

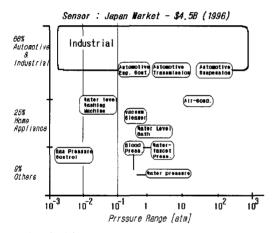

be ideal to establish a technology platform for future smart sensors with fully integrated sensor system in long term, while to develop high density Si-substrate micro-cavity technology and integrate a pressure sensor for future chemical or/and acceleration sensor sensor an intelligence/integration with MCU<sup>[11]</sup> onto a single chip on the Si-substrate in short term. Some of these short term goals already indicated that over 60 million units have been shipped and within last 3-year almost 40% is automobile purpose and most of the shipped sensors in production silicon-based micromachined pressure sensors. The world sensor market is fast growing business as indicated in Fig. 2(a) and Fig. 2(b). There are a variety of silicon sensors under development which are available to measure acceleration, temperature, pressure, chemicals, stress and light, While these sensors may be constructed in silicon, all the manufacturing processes for these sensors are not with other or with other compatible each semiconductor devices or systems. Traditional methods of manufacturing larger electromechanical

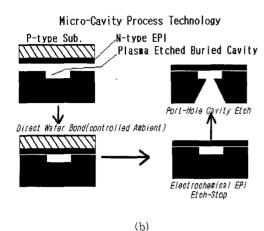

Fig. 2. (a) Total sensor market by overall region.

(b) Automotive sensor market by region where EU stands for Europe, ROW for rest of world.

sensors and providing a housing for the signal processing have been proven effective in applications where size, cost, or power consumption have a small impact. There is in fact some desirability for a large and robust mechanism in many applications. But many other applications are emerging that require smaller, lower cost, lower power solutions than traditional methods can address. It is these applications that not only require a silicon based solution, but also require future migration paths that may combine the sensor, signal conditioning and output drivers all on the same silicon wafer. In this

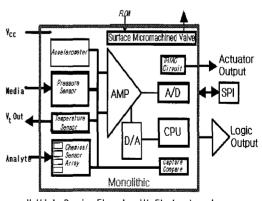

case, incompatible processes must be eliminated if they are not compatible with the mainstream MOS ones used in making microcontrollers (MCU)<sup>[12]</sup>. Why target compatibility with microcontrollers? The flexibility and rapid time to market offered by microcontroller solutions with their programmability and wide variety of peripheral options are quite attractive from a design standpoint. In addition, the low cost, high quality and excellent reliability associated with the high volume production of MOS microcontrollers are serious manufacturing consideration. Many popular sensor technologies have several characteristics that make them difficult to use with microcontrollers. These include low-level signals, nonlinearities, temperature sensitivity, and production variation in offset and/or sensitivity. A discrete device approach is the first level in the development of low cost, dedicated sensor systems<sup>[3]</sup> as shown in Fig. 3(a). variations and effects can be compensated by a variety of signal conditioning techniques using external components and then interfacing them to the microcontroller using standard MCU digital I/O(input/output) or A/D(analog-digital) microcontroller using standard components external to the MCU. Additional discrete drivers are typically used in cases where the sensor system must directly drive heavy loads. This multiple device approach may be flexible, but it can have cost or size disadvantages against more advanced

(a)

Fig. 3. (a) Future sensor technology migration.

(b) Cost comparison of sensor and IC-MCU chip.

of systems integration. The ultimate Level V concept contains a sensor of approximately  $0.2 \times 0.2 [\mu m^2]$ , which represents about 9% of area. For this type of integration, the total chip is possible but is currently not lower in cost than processing the MCU and sensor separately. To take this concept into production will require one or more significant volume customers to provide specific product definition and minimum target volume which would therefore fuel the production learning curve in a reasonable timeframe. accelerometer can be used to show how compatibility of the CMOS process with surface micromachining will allow further integration at Level IV by combining the accelerometer interface with the MCU or even allow the possibility of a full Level V combination of an MCU with embedded accelerometer. It must be pointed out that this is a likely integration path and its timing mainly depends on achieving projected costs at intermediate levels. But, by nature, micromachining and other special chemical depositions create more defects than high-volume MCU processes. Therefore, full integration at Level V is more of a business issue than a technology issue. If an extremely small form factor is required, full integration may be required, The actual point at which a Level V total solution can be placed into mass production depends on the

process complexity and defectivity of the MCU and the sensor processes as estimated as shown in Fig. 3(b). Likewise bulk-Si  $\mu$ -machining technology, SOI  $\mu$ -machining technology would attract high sensing and diverse applications since SOI technology in  $\mu$ -electronics has demonstrated ultra-high speed and ultra-low power performance by many researchers. This research presents some significant results to find permissible diaphragm dimension by piezoresistive sensor theory from the high density circular-shape SOI structure on the Si-substrate for future smart sensor chip. Further, this paper also proposes a way of integrating the current smart sensor macros with MCU as a monolithic chip solution.

## III. Design and Technology for IC EMS

This section describes the fundamental transducer operation and its stress analysis and sensitivity parameters for the transducer or sensing element. The smart sensor design with micro-controller integration and the intelligent pressure sensor will be presented.

## III-1. Target Design of High Density SOI Sensor

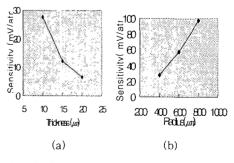

Based on transducer analysis, the sensitivity parameters for the X-ducer's output voltage and their limiting factors are concisely drawn in Table 1 where  $\pi_{ijkl}$ : piezocoefficient,  $\tau_{kl}$ : stress,  $N_A$ : concentration and xi: junction depth of a transducer or a sensing element. It is found out, based on the optimization technique as mentioned previously, that thin  $(t=10\mu m)$  and relatively large  $(r=400\mu m)$ , high supply voltage, lower impurity concentration and lowering junction depth for sensing elements such as X-ducer or piezoresistor or pulse provide an excellent sensitivity on the circular shape diaphragm. From Fig. 4, it is observed that larger radius(800 mm) indicates a good sensitivity of 94(mV/atm), however it shows more shear stress, which can not endure high pressure.

Table 1. Sensitivity parameters and limiting factor.

| Parameters                                                                                                                                            | Limiting factors                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Diaphragm thickness & radius: down/up $V_{OUT} \propto (r/t)^2$                                                                                       | <ul><li>Wafer shaping tech.</li><li>Output Voltage</li><li>Linearity</li></ul>                   |

| Supply Voltage : up $V_{OUT} \propto (W/L)V_{ss} \pi_{44} \tau_{12}$                                                                                  | · n-well pinch-off · High voltage CMOS tech.                                                     |

| W/L Ratio : up $V_{OUT} \propto (W/L)V_{ss} \pi_{44} \tau_{12}$                                                                                       | <ul><li>Micro fabrication process tech.</li><li>Potential pulling by edge effect</li></ul>       |

| X-ducer impurity Concentration : down $\pi_{44} = \pi_{44}(N_A)$                                                                                      | <ul> <li>n-well pinch-off/CMOS process compatibility</li> <li>Temperature coefficient</li> </ul> |

| X-ducer Junction Depth: down $V_{\text{OlT}} \propto (\text{W/L}) V_{\text{ss}} \pi_{\text{H}} (\frac{1}{x_{j}})$ $\int_{0}^{x_{j}} \tau_{12}(x)  dx$ | · CMOS S/D process compatibility                                                                 |

More importantly, the output voltage sensitivity of the sensing element(e.g., X-ducer) in mV/atm shows less than 100(mV/atm) = 1(mV/kPa) under the assumption of fixed thickness of  $10\mu\text{m}$ , the ratio of 0.5 in Width/Length of the transducer and supply voltage of 5V of which ranges are very close to current pressure sensor products at supply voltage of 5V. The output voltage sensitivity of the X-ducer in mV/atm shows less than 30(mV/atm) = 0.3(mV/kPa) under the same assumption of the radius whose ranges are very close to current pressure sensor products at supply voltage of 5V. It is observed that smaller thickness  $(10\mu\text{m})$  indicates a good sensitivity of 27.6(mV/atm) at fixed

Fig. 4. Output voltage sensitivity for a sensing element in (a)radius- (b)thickness-variation.

radius of  $10\mu\text{m}$ . Both sensitivities by the radius and the thickness demonstrate a good linearity according to the pressure as shown in Fig. 4, which facilitates the accuracy of the measurement in reality.

For diverse application of the sensors, permissible target dimensions for the maximum stress and deflection must be first determined, i.e., the maximum deflections and stresses for the designed SOI structures satisfy the desired target range(less than 5 µm max, deflection and 120 µm max, stress for current pressure sensor products) at around 0.1-10 atm pressure range and thereby merges multiple modules on the same silicon material with small dimensions of length and thickness of our designed SOI diaphragm to the final IC-compatible monolithic chip on the same wafer.

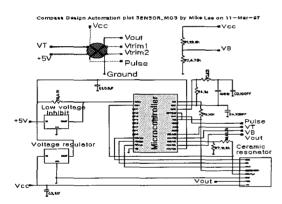

Fig. 5. A proposed MEMS smart senor with IC compatible micro-controller unit.

It is well-known that maximum stresses and deflections are increasing as the pressure increases, regardless of the top or cavity portion(bottom as shown in Fig. 1(b)) of the designed diaphragm. It is found that the SOI structure indicates safe deflection and small stresses, compared with the bulk-Si structure as expected<sup>[17]</sup>. A target position of the sensing element also predicts a product direction for any applicable high sensing micro-cavity sensor in the high technology world. It is also pointed out that the effect of the piezoresistance due to the residual stress must be corrected since the residual stress and the stress by the pressure is directly linked to the piezoresistance effect of the piezoresistor(or transducer) of sensing element.

### III-2. IC-Compatibility with Sensors

From the industrial standpoint for the product, there has been an argument that there are significant technology and cost challenges associated with DRAM and logic integration, analog and digital integration, and integration of photons and MEMS with CMOS circuits. The cost of separate chips and yield loss for the MEMS with ICs may never allow some of the merged solutions to be competitive and may also limit the usefulness of Moving a typically higher defectivity sensor process onto another chip becomes increasingly more costly as the die size increases. In all cases, adding a sensor to another silicon device will cost more due to the increased silicon area for a fixed batch size(wafer diameter). The cost penalty of adding a sensor on chip can decrease if the defectivity of the sensor process decreases or the size of the wafers increases. As these improvements occur, the added cost can be traded off against packaging and assembly costs for two-chip(Sensor Chip +MCU Chip) approach, Table 2 shows the implications of different process defectivities on the net cost of a combined solution, CMOS plus sensor, in the goal of the research. From Table 2, to demonstrate the costs of combining a sensor with an MCU, consider a small size 0.13×0.13cm MCU processed at 0.8 defects/cm and a 100×100 mil sensor processed at 4.0 defects/cml

Table 2. Theoretical relative die costs.

| Assumes                                                       | Defects per square centimeter          |                                        |                                        |                                        |

|---------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

| 6'' wafer                                                     | Best<br>in<br>Class                    | Typical<br>MOS<br>Industry             | Sensor<br>Development<br>Assumptions   |                                        |

| Die-Size<br>(cm×cm)                                           | 0.2                                    | 0.8                                    | 2.0                                    | 4.0                                    |

| 0.13×0.13<br>0.25×0.25<br>0.33×0.33<br>0.75×0.75<br>0.80×0.80 | 0.25<br>1.01<br>1.70<br>10.85<br>11.31 | 0.25<br>1.05<br>1.81<br>15.15<br>16.17 | 0.26<br>1.14<br>2.05<br>27.69<br>30.89 | 0.27<br>1.29<br>2.50<br>65.11<br>75.28 |

|                                                               |                                        | MCU                                    | Sensor                                 | MEMS                                   |

the example MCU will have a relative cost of 1,05 versus a  $0.13\times0.13$ cm device processed with zero defects: and the sensor will have a relative cost of about 1,29, which gives a combined two chip relative cost of 2,34. If they were combined on a single die using a sensor process that creates 4.0 defects/cm, the resulting die would be about  $0.25\times0.25$ cm and have a relative cost of 2,50 since  $2.34\times1.07$  results in 2,50. This cost increase of only 1,07 times the combined die cost may be less significant than the added assembly and test costs of two separate devices. The cost penalty of adding a sensor on chip can

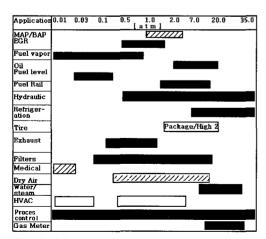

Fig. 6. (a) Application areas and technology gaps for future sensor based on the pressure ranges.

Fig. 6. (b) Technology gaps for future intelligent pressure sensor based on the pressure range.

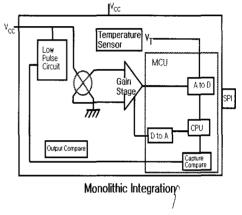

decrease if the defectivity of chip sensor process decreases or the size of the wafers increases. As these improvements occur, the added cost can be traded off against packaging and assembly costs for the two-chip approach. So our designed small size sensor using micro-cavity technology with IC compatible MCU as shown in Fig. 5.

## III-3. Trends and Expectation for Smart Sensor

The monolithic one-chip will be widely applied to automotive engine control, intelligent sensor for gas meter control and semiconductor process control, and medical sensor in the future as listed in Fig. 6(a) and Fig. 6(b) where hatched boxes of MAP, medical and dry air are currently active and potential for increased participation: open boxes of tire, water level, and HVAC are not currently participating though technical and market capabilities exist: filled boxes are not participating since major technology gap exists. Note that technology remedy for MEMS chip development on silicon CMOS as a function of supply voltage should be considered as Table 4. Also MOS design and technology innovation for high voltage

Multiple Sensing Elements with Electronic and Mechanical Controlstructure ON-Chip

Fig. 7. Multiple sensing MEMS control structure on-chip solution.

circuit are technical challenges as multi-chipmodules with separate die for sensor and the MCU interface as indicated in Table 5. Our proposal is to develop the MEMS chip on 5V CMOS technology since there is no high voltage technology required for high volume, cost sensitive applications such as sensing in automotive control systems. So IC integrated microcontroller compatible sensor are to use of the area where intelligent sensing is really needed in the future. Future sensor technology migration for fully integrated sensor is the final objective of this research as milestoned in Fig. 3. Practical application using the smart sensor as listed in Table 3 is intelligent safety gas meter or IHVAC as industrial use where the MCU<sup>[12]</sup> and other sensors can be implemented as two-chip or three-chip solution and/or multiple sensing MEMS control system as shown in Fig. 7. So it is to combine the sensor into current important available 5V or 3.3V CMOS technology for a monolithic chip like Fig. 8 with MEMS design and high voltage MOS technology as shown in Table 4 and Table 5 where pressure ranges are from 0.01[atm] to high 10[atm]. It is, therefore, necessary

Table 3. Future market for smart sensor.

| Market<br>Segment | Required<br>Media           | Current<br>Solution    | Competition | Possible Applications                                              |

|-------------------|-----------------------------|------------------------|-------------|--------------------------------------------------------------------|

| Auto-<br>motive   | ●Gas ●Oil<br>●Water<br>●Air | Mechanical     Semicon | High        | ●Air-bag●Fuel control ●Engine control ●Ride control                |

| Consume<br>r      | ●Water<br>●Air              | Mechanical Semicon     | Moderate    | ●Washer & Dryer<br>●Refrigerator/Air-con<br>d.<br>●Vacuum cleaner  |

| Industrial        | ●Gas ●Oil<br>●Water<br>●Air | Mechanical     Semicon | High        | ●HVAC ●Smart<br>Bldg.<br>●Earth-Quake detect<br>●Industrial Meters |

| Compute<br>r      | ●Air                        |                        | Low         | ●Disc Drive<br>protection<br>●End of Tape<br>Readers               |

| Tele-<br>Comm     | ●Water<br>●Air              | ●Semicon               | Low         | Below surface     tubing     Security                              |

| Bio-<br>Medical   | ●Air<br>●Fluids             | ●Semicon               | Moderate    | ●B/P & Heart Monitor  ●Saline Pumps  ●Respiratory systems          |

to overcome the combination of high voltage CMOS design for wide range of pressure and to improve the sensitivity of the designed sensor macros. Economical reality for the cost of total micro-cavity substrate is estimated about \$163.24/Wafer for a 6" bonded wafer, including back port opening of the cavity process.

Fig. 8. Monolithic integrated MEMS for automotive and medical applications.

## IV. Conclusion

This paper presents the cross-functional results for stress analyses (targeting  $5\mu$ m deflection and 100 Mh stress as maximum at various applicable pressure ranges) of IC-compatible intelligent circular-shape SOI sensor for finding permissible diaphragm dimension by output sensitivity and the temperature drift from the SOI structures. The double SOI structure shows the most feasible deflection and small stress at various ambient pressure. The SOI micro-cavity formed the sensors is promising to integrate with calibration, gain stage and controller unit plus high current/high voltage CMOS drivers onto monolithic chip on the same silicon wafer, proposing a way of developing it on unified  $5\nu$  CMOS technology for future smart sensor.

Table 4. Power supply voltage vs. MEMS chip development on silicon CMOS technology.

| ~~~~           |                                  |     |                        |                   |                                                                                                                                                                                                                                                                                  |  |

|----------------|----------------------------------|-----|------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Line           | internal Operation<br>Voltage[V] |     | Technology             |                   | D. I                                                                                                                                                                                                                                                                             |  |

| Voltage<br>[V] | X-ducer<br>& drive               | MPU | Voltage<br>regulator   | X-ducer<br>driver | Remarks                                                                                                                                                                                                                                                                          |  |

| 24             | 24                               | 5   | 24V CMOS<br>(24 to 5)  | 24V<br>CMOS       | Same specification with commercial<br>product: Better acceptability by<br>the customers.     High Voltage(H.V.) CMOS technology<br>required.                                                                                                                                     |  |

| 24             | 5                                | 5   | 24V CMOS<br>(24V to 5) | 5V<br>CMOS        | Same specification with current products:<br>Higher acceptability by the customers.     Relying primarily upon improvement of X-ducer sensitivity and/or CA/OS amplifier gain.     Sull H.V. CA/OS technology is required for the internal regulator.                            |  |

| 5              | 12                               | 5   | (External)             | 12V<br>CMOS       | V power line required.     Charge pump with four external capacitors required.     12V CMOS technology required.                                                                                                                                                                 |  |

| 5              | 5                                | 5   | (External)             | 5V<br>CMOS        | <ul> <li>improvement of X-ducer sensitivity and/or<br/>CMOS amplifier gain required.</li> <li>No H.V. CMOS technology required.</li> <li>External voltage regulator required<br/>for HVAC application.</li> <li>should Target higher pressure range<br/>applications.</li> </ul> |  |

Table 5. Applications and technology challenges.

| Pressure               | Moderate                                                                                                                                                                                                                  | High                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Range                  | 0.1 ~ 0.01 atm                                                                                                                                                                                                            | > 0.1 atm                                            |

| Application            | HVAC<br>Water Level Sensing<br>(Washer)<br>Gas Pressure Control                                                                                                                                                           | Blood<br>Pressure<br>Vacuum<br>Cleaner<br>Automotive |

| Technical<br>Challenge | Choice 1: V = 24V Design and MOS Technology Innovation for High Voltage Circuit  Choice 1: V ≤ 12V Sensor element innovation for improved sensitivity Design and MOS Technology Innovation for High Performance Amplifier | V ≤ 5V                                               |

### Acknowledgement

Authors acknowledge reviewers' valuable comments and suggestions,

#### References

- [1] K. Wise, "Microelectromechanical Systems: Interfacing Electronics to a Non-Electronic World," *IEEE IEDM'96*, p.10, Dec., 1996,

- [2] H.H. Lee, et al., "Fabrication of Surface Micromachined Polysilicon Actuators Using Dry Release Process of HF Gas-Phase Etching," IEEE IEDM'96, s30.1, Dec., 1996.

- [3] R. Frank and Joe Staller. Proc. of 3rd Int. Forum on ASIC and Xducer Tech., Alberta, Canada, May, 1990.

- [4] R. Okojie, A. Ned and A. Kurtz, "α (6H)-Si Pressure Sensor at 350°C", IEEE IEDM'96, s20.2, Dec., 1996.

- [5] F. Paoletti, M.-A. Gretillat and N.F. de Rooji, Proc. IEEE MEMS Workshop, CA, p.162, 1996.

- [6] M. Shinogi, et al., IEEE IEDM'96, s30.3, Dec., 1996.

- [7] H. Baltes, et al., "IC MEMs Microtransducers", IEEE IEDM'96, s20.1, Dec., 1996.

- [8] C. Lee, et al., IEEE IEDM'96, s20.7, Dec., 1996.

- [9] Y. Yamaguchi et al., "A High-speed 0.6-μm 16K CMOS gate array on a thin SIMOX film," IEEE Trans. Electron Devices, vol.40, p. 179, Jan. 1993

- [10] A. Auberton-Herve, "SOI: Materials and Systems," *IEEE IEDM'96*, p. 1, Dec., 1996.

- [11] T. Fuse, et al., "0.5V SOI CMOS pass-gate logic", IEEE ISSCC, p. 88, 1996.

- [12] M. Lee, "Mastery over Low Power Silcon ICs: Process technologies to System architectures", The 4th Korean Conf. on Semiconductor, Feb., Kyungiu, 1997.

- [13] N.P. Bansal and R.H. Doremus, "Handbook of glass properties", Academic Press, 1986.

- [14] J. Fraden, "Handbook of MODERN SENSORS", AIP press, N.Y., 2nd Ed., 1997.

- [15] J.J. Wortman and R.A. Evans, "Young's Modulus, Shear Modulus, and Poisson's Ratio in Silicon and Germanium", Journal of Applied Physics,

## Journal of IEEE Korea Council Vol. 1, No. 1

Vol. 36, No. 1, pp. 153-156, 1963.

[16] I-DEAS FEM<sup>TM</sup> User's Guide, MODEL SOLUTION<sup>TM</sup> Verification Reference Guide, SDRC, 1995

[17] M. Lee and Y.H. Moon, "A High Density IC

Compatible Multi-purposae Circular-Shape Sensor on Micro-Cavity SOI Technology", 1997 대한전기학회 MEMS 연구회 학술발표회 논문집, pp. 49-58, 고려대학교, 4월, 1997

## - 저 자 소 개 -

## 李明玉(正會員)

1981년 전북대학교 기계정밀공학과 B.S. 1983년12월 Arizona State Univ.(ASU) B.S. 1987년 12월 Arizona State Univ. Computer Math, M.N.S. Arizona State Univ. Computer Math., Ph.D. 1994년 4

월 日本東京大學校 電子工學科 Post-Ph.D. 1988SUS 12 월-1989년 8월 Motorola, Inc. 美 Mesa 연구소 상임연구 원. 1989년 8월-1995년 2월 Motorola, Inc. 일본 동경지점 상임기술연구원. 1992년 4월-1994년 4월 Motorola 東京 大學 과견 연구원. 1995년 3월-현재 東京大學校 研究教 投.

## 文 良 浩(正會員)

1991년 2월 한양대학교 정밀기계공학과 학사. 1993년 2월 한국 과학기술원 정밀공학과 석사. 1993년 1월-1997년 10월 아시아자동차 기술연구소 연구원. 1997년 10월-현재 삼성전기주식회사 종합연수소 주임연구원.