論 文

6-1-2

# Silane과 Disilane을 사용하여 저압 화학 기상 증착법으로 제작한 다결정 실리콘의 미세구조

## Microstructure of Polysilicon Prepared by Low Pressure Chemical Vapor Deposition Using Silane and Disilane

이은구', 라사균'', 노채성'' (Eun-Gu Lee, Sa-Kyun Rha, Jae-Sung Roh)

#### 요 약

Silane과 Disilane을 사용하여 화학증착법으로 제작한 다결정 실리콘의 미세구조를 증착온도의 변화에 따라 조사하였다. Silane과 Disilane의 증착온도는 각각 550에서 640℃와 485에서 620℃로 변화시켰다. Disilane은 silane에 비해 반응성이 크고 비정질에서 결정으로 변하는 전이온도는 약 20℃정도 높았다. 전이온도에서 증착한 시편은 실리콘 source에 관계 없이 (311)조직의 거친 표면으로 되어있었다. 900℃에서 열처리하는 동안 비정질로 부터는 (111)쌍정립계를 갖는 수지상의 결정성장을 하였다. 반면에 다결정 상태로 증착한 시편은 열치리하는 동안 구조가 거의 변하지 않았고 매우 작은 결정립으로 이루어진 주상구조를 하였다.

#### Abstract

The microstructure of polysilicon films deposited using silane and disilane as a silicon source have been studied as a function of deposition temperature. The deposition temperature was varied from 550 to 640°C for silane and from 485 to 620°C for disilane, respectively. Disilane is more reactive and its amorphous to crystalline transition temperature is around 20°C higher than silane. The film deposited at the transition temperature has an uneven surface with small(311) texture regardless of silicon source. A dendritic grain growth with (111) twin boundaries from amorphous state is observed during subsequent annealing at 900°C. However, the film deposited in polycrystalline state consists of a small grain with columnar structure and seems to be almost unchanged upon annealing.

\* : 조선대학교 재료공학과

\*\*: 금성일렉트론 주식회사 8연구실

#### 1. Introduction

Polycrystalline silicon (polysilicon) films formed by low pressure chemical vapor deposition (LPCVD) of silane (SiH<sub>4</sub>) are widely used in integrated circuits

for various applications as MOS gates, interconnects, resistors, and emitter contact. Other applications include photovoltaic conversion, thermal and mechanical sensors, and thin film transistor(TFT) for large area liquid crystal displays(LCDs). The electrical resisti-

vity of polysiticon is, in general, larger than that of single-crystal silicon due to the existence of grain boundaries The electrical performance of the polysilicon is strongly determined by its microstructure, which depends on deposition parameters(1-4). Electrical properties for as-deposited polycrystalline or as-deposited amorphous silicon have been investigated by a number of authors(5,6). It was suggested that deposition temperature should be as low as possible to obtain high conductivity and carrier mobility. Disilane (Si<sub>2</sub>H<sub>6</sub>) has been used as an alternative to silane for growing amorphous silicon and insitu doped silicon(7-9). In this paper we present the effects of deposition temperature on the microstructure of the film deposited using silane and disilane as a silicon source.

#### 2. Experimental

Silicon dioxide (SiO<sub>2</sub>) layers of 1000 Å were formed by thermal oxidation at 900  $^{\circ}$ C using a  $H_2/O_2$  atmosphere on p-type (100) wafers. Polysilicon films with a thickness of 0.25  $\mu$ m were deposited on the oxide layers in a commercial induction heated hot wall horizontal and vertical reactor for silane and disilane. respectively Undiluted silane gas was supplied with flow rate of 150 sccm under 0.25Torr, while disilane gas of 280 sccm and N<sub>2</sub> gas of 1500sccm were supplied under 0.64Torr. The deposition temperature was varied from 550 to 640℃ for disilane and from 485 to 620℃ for disilane, respectively, All the specimens were annealed at 900°C for 30min in nitrogen.

The thickness of the LPCVD silicon layers was measured using an ellipsometer. The microstructure and surface morphology of the films were analyzed using x-ray diffraction patterns(XRD), and a scanning electron microscope(SEM). To estimate the average grain size of the films, transmission electron microscopy(TEM) was used. Thermal wave(TW) technique

was performed to evaluate a degree of crystallization after annealing. TW signals of samples were measured with a Therma-Probe Model 200 system.

#### 3. Result and Discussion

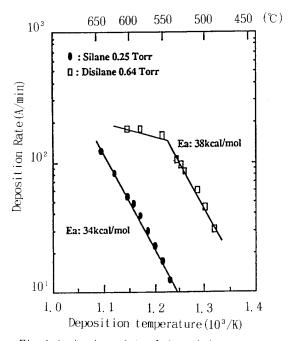

The growth rates for silane and disilane as a function of reciprocal temperature are shown in Fig.1. The silane growth is controlled by surface reaction and has an apparent activation energy of 34 Kcal/mol up to 640°C. The disilane

Fig. 1. Arrhenius plot of deposition rates for silane and disilane.

data show two growth regimes with different activation energy above and below 540°C. Disilane growth has an apparent activation energy of 38 Kcal/mol at low temperature. The growth rates obtained by using disilane are faster than those obtained with silane at the low temperature. In case of disilane, a rapid homogeneous gas phase decomposition which generates a high concentration of highly reactive silylene (SiH<sub>2</sub>) resulted in a high growth rate at low temperature.

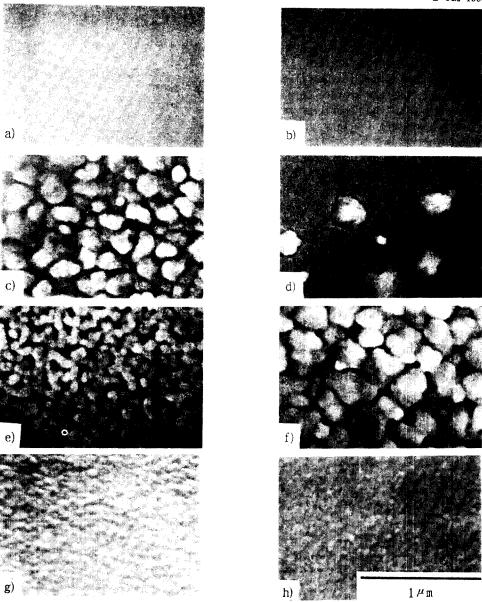

Fig. 2, SEM photographs of films deposited using silane (a, c, e, g) and disilane (b, d, f, h) at  $560\,^\circ$ C (a, b),  $580\,^\circ$ C (c, d)  $600\,^\circ$ C (e, f), and  $620\,^\circ$ C (g, h).

Surface morphology of as-deposited film as a function of deposition temperature and silicon source is shown in Fig. 2. In case of silane, the film deposited at  $560^{\circ}$ C (a) has a smooth surface and at  $580^{\circ}$ C (c) has a large grains and at  $620^{\circ}$ C (g) has rough surface. In case of disilane, the film deposited at  $560^{\circ}$ C (b) has a smooth surface and at  $580^{\circ}$ C (d) has some

nuclei, which start to grow. The film deposited at 600°C (f) has large grains and almost the same morphology as (c) and at 620°C (h) has a typical polysilicon surface morphology. Comparing with deposition rate and surface morphology of the film deposited using silane and disilane, it can be said that lowering the deposition rate lowers the transition temperature. It is found that the

#### Silane과 Disilane을 사용하여 저압화학 기상 중착법으로 제작한 다결정 실리콘의 미세구조

film deposited using silane has around 20% lower transition temperature than the film deposited using disilane. These results suggest that the surface morphology is related to the deposition rate and silicon atom migration rate at the deposition temperature.

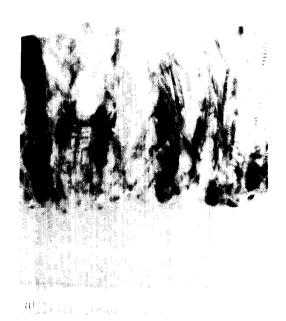

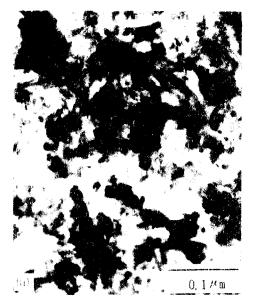

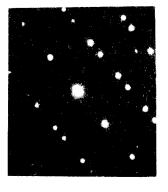

In order to examine the grain growth during annealing, TEM works were taken, Figure 3 shows cross-sectional TEM (X-TEM) micrographs of 900°C annealed films deposited at 504°C for disilane, 560°C and 625°C for silane. It is observed that the film deposited at 625°C (a) consists of a columnar grain structure and seems to be almost unchanged upon annealing at 900°C. However, the annealed film deposited at amorphous state (b, c) has a large grain with (111) twin boundaries shown in selected area diffraction (SAD) pattern. For disilane (c), the grain size is much larger than film thickness,

Fig. 3. X-TEM photographs of the films deposited using silane (a, b) and disilane (c) at 625% (a), 560% (b) and 504% (c).

Figure 4 shows the plane TEM photographs of the annealed films. It is seen

that the average grain sizes of the poly silicon films deposited at amorphous

### 電氣電子材料學會 論文誌 6卷 1號 1993年 1月

state are much larger than those of the films deposited at polycrystalline state after annealing. The grain size of the annealed film deposited at 625°C is approximately 200-300Å, while as-deposi-

ted amorphous films followed by the 900 °C anneal have elliptical grain growth with many(111) twin boundaries. Each elliptical grain consists of many twin boundaries along the major and minor

axis. The major axis of each ellipse is several times larger than minor axis. Comparing with Fig. 4-b) and c), it can be said that the grain size increases with decreasing the deposition temperature

Fig. 4. Plane TEM photographs of the films deposited using silane(a, b) and disilane(c) at 625°C (a), 560°C (b), and 504°C (c). The corresponding selected area diffraction (SAD) pattern is shown.

resulting from few nuclei density during solid phase crystallization of amorphous Si.

Crystal structures of the films were analyzed using XRD. Three crystalline

Silane과 Disilane을 사용하여 저압화학 기상 증착법으로 제작한 다결정 실리콘의 미세구조

components(111), (110) and (311) were detected for the sample deposited above  $570^{\circ}$ C for silane and  $580^{\circ}$ C for disilane, respectively. The microstructure and x-ray texture are summarized in Table 1.

It is observed that the (311) component dominates for the films deposited in the transition temperature. Comparing XRD data with film morphology, the undoped film deposited at the transition temperature has a rugged surface with small(311) texture regardless of the silicon source. It is found that no appreciable difference in the surface morphology and X-ray texture and TEM structure between undoped films deposited using silane and disilane except for the amorphous to crystalline transition temperature.

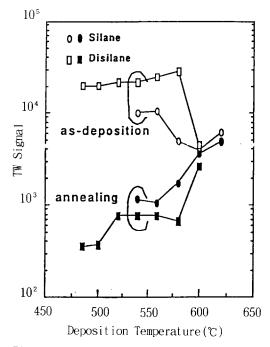

In order to study the degree of crystallization during annealing, TW signals are measured and the results are shown in Fig. 5. Thermal wave technique is used in monitoring the Si device process such as a damage and defect created by implanation and dry-etching. It has been reported(10) that TW signal shows a high sensitivity to grain boundary density of polysilicon film. It is observed that TW signals of the films are much higher than that observed from single crystalline Si wafers(less than 100). For as-deposited film, the TW signal slightly increases with the deposition temperature up to 560℃ for silane and 580℃ for disilane, respectively and then dramatically decreases with further increase in the deposition temperature. Comparing with the surface morphology, XRD data and TW signals of as-deposited film, it can be said that the amorphous to polysilicon transition temperature is around 560°C for silane and 580℃ for disilane, respectively. The high transition temperature of disilane is probably due to the high growth rate shown in Fig. 1. It is noted that TW signal of annealed film decreases with decreasing the deposition temperature. This result suggests that lower-

Fig. 5. Variation of TW signal as a function of deposition temperature.

Table 1. TEM structure and X-ray texture as a function of silicon source and deposition temperature  $(T_d)$ .

| $L^{q}(\mathbb{C})$ | Silane        | Disilane       |

|---------------------|---------------|----------------|

| 560                 | a-Si          | a-Si           |

| 570                 | a-Si/Poly     | a-Si           |

| 580                 | HSG (311)     | a-Si/Poly      |

| 590                 | Columnar(311) | HSG (311)      |

| 600                 | Columnar(311) | HSG (311)      |

| 620                 | Columnar(110) | Columnar (110) |

a-Si: amorphous Silicon

HSG : Hemispherical grained poly-

silicon

ing the deposition temperature is required to obtain highly ordered large grain structure.

#### 4. Conclusion

Microstructure of polysilicon films deposited using silane and disilane as a silicon source have been studied as a function of deposition temperature. It is observed that disilane is more reactive and its amorphous to polycrystalline transition temperature is around 20℃ higher than silane. Undoped film deposited at the transition temperature has a rugged surface with (311) texture regardless of silicon source. It is found that no appreciable difference in the surface morphology and X-ray texture and TEM structure between undoped films deposited using silane and disilane. TW data imply that lowering the deposition temperature is required to obtain highly ordered structure. Disilane is suitable for Si source gas to prepare amorphous Si at low deposition temperature with high growth rate.

#### Reference

- T. I. Kamins, M. M. Mandurah and K. C. Saraswat, "Structure and Stability of Low Pressure Chemically Vapor-Deposited Silicon Films", J. Electrochem. Soc. . 125 (1978) 927

- Y. Wada and S. Nishimatsu, "Grain Growth Mechanism of Heavily Phosphorus Implanted Polycrystalline Silicon" J. Electrochem. Soc., 125 (1978) 1499

- T. I. Kamins, "Structure and Properties of LPCVD Silicon Films", J. Electrochem Soc., 127 (1980) 686

이은구

1957년 1월 1일생. 1979년 서울대 공대 요업공학과 졸업, 1981년 한국과학기술원 재료공학과졸업(석사), 1991년 한국과학기술원 재료공학과 졸업(박사). 1981년- 84년 한국전자통신연구

소 근무, 1984 년- 89년 급성사 중앙연구소 근무, 1989- 92년 급성 일랙트론 책 임연구원, 현재 조선대학 공대 재료공학과 전임강 사,

- G. Harbeke, L. Krausbauer, E. F. Steigmeier, A. E. Widmer, H. F. Kappert and G. Neugebauer, "Growth and physical Properties of LPCVD Polycrystalline Silicon Films", J. Electrochem, Soc., 131 (1984) 675

- 5. M. Hendriks, C. Mavero, "Phosphorus Doped Polysilicon for Double Poly Structures", J. Electrochem, Soc., 138 (1991)1466

- E. G. Lee and H. B. Im, "Effects of Microstructure and As Doping Concentration on the Electrical Properties of LPCVD Polysilicon", J. Electrochem, Soc. 138 (1991) 3465

- S. Nakayama, H. Yonezawa, and J. Murota, "Deposition of Phosphorus Doped Silicon Films by Thermal Decomposition of Disilane", Jpn. J. Appl. Phys., 23, (1984) L493

- 8. W. Ahmed and D.B. Meakin, "Uniform Deposition of institu Doped Polysilicon Films by Ultralow Pressure Chemical Vapour Deposition", Thin Solid Films, 148(1987)L63

- 9. L.D.Madsen and L.Weaver, "In Situ Doping of Silicon Films Prepared by Low Pressure Chemical Vapor Deposition Using Disilane and Phosphine", J.Electrochem. Soc. 137 (1990) 2246

- 10, S. Hahn and W. L. Smith, "Characterization of Polycrystalline Silicon Using the Thermal Wave Technique", ICVC Tech. Dig. (1989) 563

(1992년 8월 17일 접수)

라사균

1959년 6월 5일생. 1983년 성균 관 대학교 물리학과 졸업. 1985 년 서울대 물리학과 졸업(석사). 현재 규성일렉트론 반도체 공정 개발 8실 주임연구원.

노재성

1960년 11월 27일생, 1984년 연세대 요업공학과 졸업, 1988년 8월 한국과학기술원 재료공학과 졸업(박사), 현재 급성일렉트론 반도체공정개발 8실 선임연구원,

T. IEEME, Vol. 6, No. 1, 1993