# Test Patterns for Asynchronous Multiple-Access Frequency-Hopped Spread-Spectrum Systems

# (비동기 다원접속 주파수도약 확산대역 시스템을 위한 테스트 패턴)

李在弘 \* 웨인 스타크.\*\*\* 吳相縣\*\*

(Jae Hong Lee, Wayne E. Stark and Sang Hyun Oh)

#### 要約

지속시간이 가변적인 블록간섭이 있는 비동기 다원접속 저속 주파수 도약 확산대역 시스템에 맞는 가변상태 블록 간섭 채널이 제안된다. 가변상태 블록간섭 채널에서 복호기에 부가정보를 주기 위하여 인터리빙과 결합된 테스트 패턴 기법이 제안된다. 복호기는 테스트 패턴을 검사함으로써 간섭의 영향을 받은 데이타 블록의 부분을 추정하고 그 부분을 소거(erasure)로 간주한다. 테스트 패턴의 존재가데이타 전송에 쓰이는 비트 수를 감소시키므로 테스트 패턴은 다른 사용자에 의한 주파수 충돌확률이 작은 가변상태 블록간섭 채널에 대해서는 유용하지 않다. 주파수 충돌확률이 큰 가변상태 블록간섭채널에 대하여 테스트 패턴을 사용하면 채널용량이 증가함을 보인다. 또한 채널의 변수가 특정한 범위의 값을 가질 때 테스트 패턴으로부터 채널상태에 대한 거의 완전한 부가정보가 얻어짐을 보인다.

#### Abstract

A variable-state block interference channel model is presented which matches asynchronous multiple-access slow frequency-hopped spread-spectrum systems which suffer from bursts of interference of variable duration. For variable-state block interference channels test pattern techniques combined with interleaving are presented from which the decoder obtain side information about channel states. By examining test patterns the decoder estimates which parts of data blocks are affected by interference and regards the parts of blocks affected by interference as erasures. Since the presence of test patterns reduces the number of bits for data transmission, test patterns are not useful for variable-state block interference channels for small hit probability. It is shown that test patterns increase the capacities of variable-state block interference channels for large hit probability. It is also shown that test patterns provide almost full side information about channel states for certain values of parameters.

(Dept. of Elec. Eng., Seoul Nat'l Univ.)

Univ. of Michigan)

接受日字: 1988年 11月 3日

#### I. Introduction

In real communication systems a packet of data can be modeled as a block of the block interference channel [1] [2]. A block interference channel can be viewed as a discrete memoryless

<sup>\*</sup>正會員, \*\*準會員, 서울大學校 電子工學科

<sup>\*\*\*</sup>正會員, 미시간大學校 電氣工學 및 컴퓨터科學科 (Dept. of Electrical Eng., and Comp. Science,

channel (DMC). However, in designing communication systems, viewing a block interference channel as a DMC makes the coding alphabet is so large for large block length that it is quite difficult to devise practical codes using such a large alphabet [3]. To overcome the difficulty we may adopt interleaving and then use a code over a much smaller coding alphabet.

Side information is information about the state of a channel over which data is transmitted provided to the encoder or the decoder [2] [4] [5]. A channel with side information gives larger channel capacity than the same channel without side information. In [2] a technique was proposed to improve the performances of codes on block interference channels when there is no side information. The idea is to attach a fixed test pattern to a transmitted packet of data to give side information to the decoder. The test pattern is used to make a statistical decision about which of the component channels each packet was transmitted over on the basis of the received version of the test pattern. That is, by examining the test pattern, the decoder estimates whether a packet is received during a good channel state, that is, free from interference, or during a bad channel state, that is, contaminated by interference. If a packet, or a block, is estimated to be in a bad state, then the decoder erases all of the received data in that block. If a block is estimated to be in a good state, then the decoder accepts all the received data in that block. Combined with interleaving to enhance the feasibility of code design, this technique was shown to improve the performances of codes on block interference channels.

However, it was assumed in [2] that channels and interference are block-wise synchronous which means interference occurs in a whole block if it occurs, and partial block interference was not considered. However, partial block interference is more common than whole block interference practice, since signals from users are asynchronous in most multi-user systems, and jamming and fading are also asynchronous in their nature. We can imagine that erasing all data in a partially contaminated block would not be a desirable strategy for channel efficiency, since there are still some uncontaminated data in the block.

In Section II we model a spread-spectrum communication channel into a variable-state block interference channel and present a new test pattern technique for it. In Section III we calculate the capacities of interleaved variablestate block interference channels with a test pattern. In Section IV we present numerical results and show that test patterns increase the capacities of the channels. In Section V we summarize and draw general conclusions from our work,

# II. Test Patterns for A Interleaved Variable-state Block Interference Channels

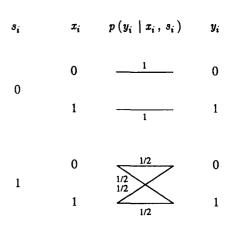

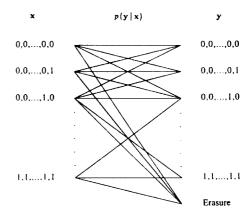

We model an asynchronous multiple-access frequency-hopped spread-spectrum channel into a variable-state block interference channel [1]. A variable-state block interference channel has channel memory of length M, binary input alphabet and binary output alphabet both of which consist of two letters (0, 1). In addition, the channel state alphabet  $\Omega_i$  is (0, 1) for all channel locations in a block, that is,  $\Omega_i=(0, 1)$ for i=1,2,...,M. A channel state random vector  $S=(S_1, S_2, ..., S_M)$  indicates the noise severities of channels;  $s_i \in (0, 1)$ ,  $s \in (0, 1)^M$  on which the probability distribution p is defined. The channel state vector for each block of M channel uses is chosen independently of the other blocks, but with the same distribution. Two component channels  $p(y_i/x_i, 0)$  and  $p(y_i/x_i, 1)$  are binary symmetric channels (BSC's) with crossover probabilities 0 and 1/2, respectively, for i=1,2,...M, as shown in Fig. 1

Fig.1. Component channels for a two-state channel.

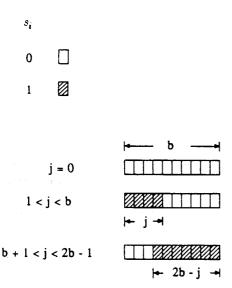

A random variable J,  $j \in (0, 1, 2, ..., 2M-1)$ , determines the channel state. Specifically, if J=0 then  $S=0^M$ , if J=j and  $1 \le j \le M$  then  $S=1^j 0^{M-j}$  and if J=j and  $M+1 \le j 2M-1$  then  $S=0^{j-M} 1^{2M-j}$  where  $0^j$  means 0 repeated j times and  $1^j$  means 1 repeated j times. J is one-to-one mapping of S. We depict how interference affects the states of channels in a block and how a random variable J determies channel states in Fig. 2. Since the channel state vector S for each block of M channel uses is independent and identically distributed, the random variable J for each M channel uses is independent and identically distributed. We let J have the probability distribution

$$P\{J=j\} = \begin{cases} 1-p_h, & j=0; \\ \frac{p_h}{2M-1}, & j=1,2,\dots,2M-1 \end{cases}$$

(1)

where  $P_h$  is the probability that a block is hit by interference. This distribution matches asynchronous multiple-access interference.

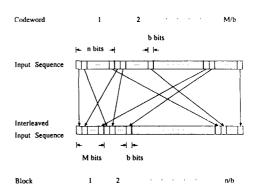

We design test patterns for variable-state block interference channels which are combined with interleaving. We discuss interleaving/deinterleaving technique first and then test patterns. First, we consider interleaving and deinterleaving for block interference channels. In an interleaved coding strategy, a finite state device called an interleaver is inserted between the encoder and the channel as shown in Fig.3. Let b be an integer that divides M and n. We interleave M/b codewords each of whose length is n bits in the following fashion. The data transmitted during the first block consists of the first b-bit segments from each of the M/b codewords. The data transmitted during the second block consists of the second b-bit segments from each of the M/b codewords as shown in Fig.4. Doing this we get a sequence of n/b blocks each of whose length is M bits. We call this interleaving to depth M/b. Also we call the b-bit segment a sub-block. Let  $X_i = (X_{i,1}, X_{i,2}, ..., X_{i,n})$  denote the ith codeword. Subdivided into b-bit sub-blocks, the *i*th codeword  $X_i$  is rewritten as

$$\mathbf{X}_{i} = (\mathbf{X}_{i,1}^{(b)}, \, \mathbf{X}_{i,2}^{(b)}, \, \cdots, \, \mathbf{X}_{i,n \geq b}^{(b)}) \tag{2}$$

where

$$X_{i,1}^{(b)} = (X_{i,1}, X_{i,2}, \cdots X_{i,b}),$$

$$X_{i,2}^{(b)} = (X_{i,b+1}, X_{i,b+2}, \dots, X_{i,2b}), \dots,$$

and

$$X_{i,n > b}^{(b)} = (X_{i,n-b+1}, X_{i,n-b+2}, \dots, X_{i,n}).$$

Taking the sequence of M/b codewords,  $X_1$ ,  $X_2$ , ...,  $X_{M/b}$ , from the encoder, the interleaver rearrange to obtain the sequence of  $X_{1,1}^{(b)}$ ,  $X_{2,1}^{(b)}$ , ...,  $X_{M/b,1}^{(b)}$ ,  $X_{1,2}^{(b)}$ ,  $X_{2,2}^{(b)}$ , ...,  $X_{M/b,2}^{(b)}$ , ...,  $X_{1,n/b}^{(b)}$ ,  $X_{2,n/b}^{(b)}$ , ...,  $X_{M/b,n/b}^{(b)}$ .

Let  $Y_i$  and  $Y_{i,j}^{(b)}$  denote the output corresponding to an input codeword  $X_i$  and the output corresponding to a sub-block input  $X_{i,j}^{(b)}$  respectively. Then, the output from the channel is the sequence of  $Y_{1,1}^{(b)}$ ,  $Y_{2,1}^{(b)}$ , ...,  $Y_{M/b,1}^{(b)}$ ,  $Y_{1,2}^{(b)}$ ,  $Y_{2,2,2}^{(b)}$ , ...,  $Y_{M/b,2}^{(b)}$ , ...,  $Y_{I,n/b}^{(b)}$ ,  $Y_{2,n/b}^{(b)}$ , ...,  $Y_{M/b,n/b}^{(b)}$ . At the receiving end, there is a deinterleaver between the channel and the decoder. The deinterleaver inverts what the interleaver did and gives the decoder the noisy versions of the codewords in the same order as they were generated by the encoder. That is, taking the output sequence

Fig.2. States of a variable-state block interference channel.

Fig.3. Communication system with interleaving/ deinterleaving.

from the channel, the deinterleaver rearange it into the sequence of  $Y_{1,1}^{(b)}$ ,  $Y_{1,2}^{(b)}$ , ...,  $Y_{1,n/b}^{(b)}$ ,  $Y_{2,1}^{(b)}$ ,  $Y_{2,2}^{(b)}$ , ...,  $Y_{2,n/b}^{(b)}$ , ...,  $Y_{M/b,1}^{(b)}$ ,  $Y_{M/b,2}^{(b)}$ , ..., and  $Y_{M/b,n/b}^{(b)}$ . From (2) this sequence is rewritten as the sequence of  $Y_1$ ,  $Y_2$ , ...,  $Y_{M/h}$ .

The function of a interleaver/deinterleaver pair is to introduce long delays between successive bbit sub-blocks so that no two b-bit sub-blocks in any codeword will reside in the same M-bit transmitted block. So that we may ignore the dependence between the channel state of one block and the channel states of the other blocks in an interleaved block interference channel. Without interleaving a good coding strategy is to treat each M-bit block as one symbol in a code. However, for large M this becomes difficult to implement[3]. As the effective value of block length M is reduced to b with interleaving the effective capacity of channel is reduced.

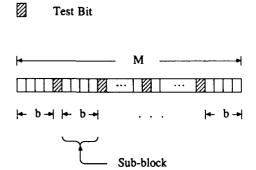

Second, we consider a test pattern technique for an interleaved variable-state block interference A test pattern aims to provide side information about the channel state to the decoder. A test pattern consists of several test bits in each M-bit block of input sequence. Let a test pattern  $X_{TP}$  consist of t test bits placed at locations  $i_1, i_2, ..., i_t$  in an input sequence X of M bits. The presence of the test pattern reduces the number of bits available for data transmission from M to M - t in a M-bit block. Therefore, the number of codewords transmitted in n/b blocks is reduced from M/b to (M-t)/b.

Test bits are set with a known pattern by the encoder and the decoder. For example, we consider all bits in the test pattern X<sub>TP</sub> set to be zeros by the encoder, that is,  $X_{TP}=(0,0, ..., 0)$ . This test pattern is appropriate for channels whose component channels are BSC's. Receiving data including the test bits, the decoder applies a maximum-likelihood estimation rule to the received test bits to estimate the block channel state random variable J. Let  $\hat{J}$  denote the estimate of the random variable J, then

$$\hat{J} = j, \text{ if } P\{J = j \mid \mathbf{X}_{TP} = (0, 0, \dots, 0), \ \mathbf{Y}_{TP} = \mathbf{y}_{TP}\}\$$

$$\geq P\{J = j' \mid \mathbf{X}_{TP} = (0, 0, \dots, 0), \ \mathbf{Y}_{TP} = \mathbf{y}_{TP}\}\$$

(3)

for all  $j' \neq j$ ,  $0 \leq j,j' \leq 2M-1$ , where  $X_{TP} = (X_{i_1}, X_{i_2}, X_{i_3}, X_{i_4}, X_{i_5}, X_$  $X_{i_2}, ..., X_{i_r}$ ) is a sequence of letters transmitted as test bits and Y<sub>TP</sub> is the corresponding output sequence. By Bayes' rule, (3) becomes

$$\hat{\mathbf{J}} = j, \text{ if}$$

$$\frac{P\{\mathbf{Y}_{TP} = \mathbf{y}_{TP} \mid \mathbf{X}_{TP} = (0, 0, \dots, 0), J = j\}}{P\{\mathbf{Y}_{TP} = \mathbf{y}_{TP} \mid \mathbf{X}_{TP} = (0, 0, \dots, 0), J = j'\}} P\{J = j'\} \ge 1$$

(4)

for all  $j' \neq j$ ,  $0 \leq j$ ,  $j' \leq 2M-1$

Fig.4. Interleaving to depth M/b.

Fig.5. A test pattern for variable-state block interference. l=1.

# III. Capacities of Interleaved Variable-state **Block Interference Channels with Test Patterns**

Let us consider the states of sub-block channels. Let a channel state random vector  $\mathbf{S}^{(b)} = (S_1^{(b)}, S_2^{(b)}, ..., S_b^{(b)})$  indicate the noise severities of channels;  $S_i^{(b)} \in \{0, 1\}, \mathbf{s}^{(b)} \in \{0, 1\}^b$ . A random variable  $J^{(b)}$ ,  $J^{(b)} \in \{0, 1, 2, ..., 2b-1\}$ , determines the channel state of a b-bit subblock. Specifically, if  $J^{(b)}=0$  then  $S^{(b)}=0^b$ , if  $J^{(b)}=j$  and  $1 \le j \le b$  then  $S^{(b)}=1^j0^{b-j}$ , and if  $J^{(b)}=j$  and  $b+1 \le j \le 2b-1$  then  $S^{(b)}=0^{j-b}1^{2b-j}$  where  $0^j$  means 0 repeated j times and  $1^j$  means 1 repeated j times.  $J^{(b)}$  is one-to-one mapping of  $S^{(b)}$ . We depict how interference affects the states of channels in a block and how a random variable  $J^{(b)}$  determines channel states in Fig. 6. After some derivation from (1), we get

$$P\{J^{b)} = j\} = \begin{cases} (1-p_h) + \frac{p_h(M-b)}{2M-1}, & j=0; \\ \frac{p_h}{2M-1}, & j=1,2,\dots,b-1; \\ \frac{p_h}{2M-1}(M-b+1), & j=b; \\ \frac{p_h}{2M-1}, & j=b+1,\dots,2b-1 \end{cases}$$

(5)

where  $P_h$  is the probability that a block is hit by interference. Notice that  $p\{J^{(b)}=j\}$  does not depend on the location of a sub-block in a block.

Now we consider the capacities of interleaved variable-state block interference channels. Channel capacity is a quantitative measure of the performance of a test pattern, since the purpose of a test pattern to increase the capacity of a block interference channel combined with interleaver/

Fig.6. Block interference and the states of a sub-block.

deinterleaver. We define the Mth-order channel capacity of an interleaved block interference channel to the depth of M/b as the average of normalized capacity of b-bit subblocks over a block.

First, we consider the Mth-order capacity C(M,b) of a block interference channel with no test pattern and no side information. Since an interleaved variable-state block interference channel behaves as if it were memoryless from subblock to sub-block in the same M-bit block, by the definition of channel capacity

$$\hat{C}(M, b) = \frac{1}{M} \max_{\rho(\mathbf{x})} I(\mathbf{X}; \mathbf{Y}, \mathbf{S})$$

$$= \frac{1}{M} \sum_{i=1}^{M \setminus b} \max_{\rho(\mathbf{x}_{k,i}^{(b)})} I(\mathbf{X}_{k,i}^{(b)}; \mathbf{Y}_{k,i}^{(b)})$$

(6)

for k=1,2, ..., M/b. Since the radom variable  $J^{(b)}$  of a b-bit sub-block is identically distributed regardless of the location of the sub-block in a block by the definition of the channel, (6) becomes

$$\hat{C}(M, b) = \frac{1}{b} \max_{\rho(\mathbf{x}_{k,t}^{(b)})} I(\mathbf{X}_{k,t}^{(b)}; \mathbf{Y}_{k,t}^{(b)})$$

$$\tag{7}$$

for any i=1,2, ..., M/b and k=1,2, ..., M/b. Viewing a sub-block of channels as a DMC, from (7) we have

$$\hat{C}(M, b) = \frac{1}{h}C(b) \tag{8}$$

where C(b) is the capacity of a DMC with input alphabet  $\{0, 1\}^b$ , output alphabet  $\{0, 1\}^b$ , and transition probability  $P(\mathbf{y}_{i,k}^{(b)} | \mathbf{x}_{i,k}^{(b)})$  for any  $i=1,2,\ldots,M/b$  and  $k=1,2,\ldots,M/b$ .

Second, we consider the Mth-order capacity  $\hat{C}_{SI}$  (M,b) of a block interference channel with no test pattern, assuming full side information is available somehow. Since an interleaved variable-state block interference channel behaves as if it were memoryless from sub-block to sub-block in the same M-bit block,

$$\hat{C}_{SI}(M, b) = \frac{1}{M} \sum_{t=1}^{M/b} \max_{\rho \in \mathbf{x}_{k,t}^{(b)}} I(\mathbf{X}_{k,t}^{(b)}; \mathbf{Y}_{k,t}^{(b)}, \mathbf{S}_{k,t}^{(b)})$$

(9)

for any k=1,2, ..., M/b. Since the random variable  $J^{(b)}$  of a b-bit sub-block is identically distributed

regardless of the location of the sub-block in a block by the definition of the channel, (9) becomes

$$\hat{C}_{SI}(M,b) = \frac{1}{b} \max_{\substack{\rho(\mathbf{X}_{k,t}^{(b)}) \\ \mathbf{k},t}} I(\mathbf{X}_{k,t}^{(b)}; \mathbf{Y}_{k,t}^{(b)}, \mathbf{S}_{k,t}^{(b)})$$

(10)

for any i=1,2, ..., M/b and k=1,2, ..., M/b. After some derivation from (5) and (10) we obtain

$$\hat{C}_{st}(M, b) = 1 - \frac{p_h M}{2M - 1} \tag{11}$$

Third, we consider the Mth-order capacity  $\hat{C}_{TP}$  (M,b,l) of a block interference channel with a test pattern which has a test bit for very l subblocks. The presence of the test pattern reduces the number of bits available for data transmission from M to M-t in an M-bit block where t is the number of test bits in a block which is

$$t = \frac{M+1}{l \ b+1} - 1 \tag{12}$$

Therefore, the number of codewords transmitted in n/b blocks is reduced from M/b to (M-t)/b when b divides M-t. A b-bit sub-block channel in an interleaved variable-state block interference channel with a test pattern is a symmetric crasure channel, as shown in Fig 7. Since an interleaved variable-state block interference channel behaves as if it were memoryless from sub-block to sub-block in the same M-bit block, the capacity  $\hat{C}_{TP}(M,b,l)$  is given by

$$\hat{C}_{TP}(M, b, l) = \frac{1}{M} \sum_{a}^{(M-l) < b} b \hat{C}^{(b)}(i)$$

(13)

where  $\hat{C}^{(b)}$  (i) is the normalized capacity of the ith b-bit sub-block channel in the block. Since the amount of information provided to the decoder is lower and upper bounded by the capacity of channel without side information and the capacity of channel with full side information, respectively, the Mth order channel capacity with the test pattern  $\hat{C}_{TP}(M,b)$  is bounded by

$$\left(1 - \frac{t}{M}\right) \hat{C}(M, b) \leq \hat{C}_{TP}(M, b, l)$$

$$\leq \left(1 - \frac{t}{M}\right) \hat{C}_{SI}(M, b) \quad (14)$$

where t is the number of test bits in a block.

Fig.7. Model for a sub-block channel with a test pattern.

#### IV. Numerical Results

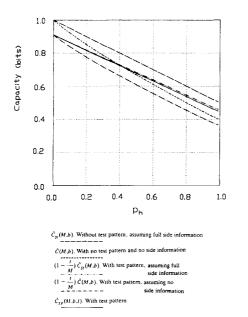

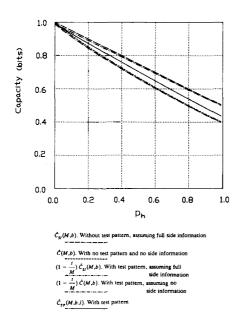

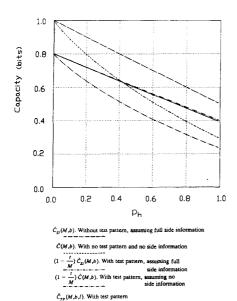

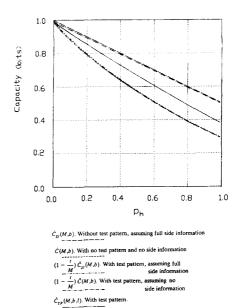

To examine how much the capacity is increased or decreased by the presence of a test pattern, we compute and compare Mth-order channel capacity  $\hat{C}_{TP}(M,b,l)$  with other Mth-order channel capacities:  $\hat{C}(M,b)$ ,  $\hat{C}_{SI}(M,b)$ ,  $(1-\frac{t}{M})$   $\hat{C}(M,b)$ , and  $(1-\frac{t}{M})$   $\hat{C}_{SI}(M,b)$  where  $\hat{C}(M,b)$  is the capacity of a block interference channel with no test pattern and no side information, and  $\hat{C}_{SI}(M,b)$  is the capacity of a block interference channel with no test pattern, assuming full side information is available somehow. Note that  $(1-\frac{t}{M})$   $\hat{C}(M,b)$  and  $(1-\frac{t}{M})$   $\hat{C}_{SI}(M,b)$  serve as a lower bound and a upper bound respectively for  $\hat{C}_{TP}(M,b,l)$ , since the capacity of each sub-block is larger than  $\hat{C}(M,b)$  and smaller than  $\hat{C}_{SI}(M,b)$ .

We plot channel capacities  $\hat{C}_{TP}(M,b,l)$ ,  $\hat{C}(M,b)$ ,  $\hat{C}_{SI}(M,b)$ ,  $(1-\frac{t}{M})$   $\hat{C}_{CM}(M,b)$ , and  $(1-\frac{t}{M})$   $\hat{C}_{SI}(M,b)$  for M=1,000, b=10, t=90 and l=1 in Fig. 8. and for M=1,000, b=10, t=10, and l=9 in Fig. 9. It is seen in Fig. 8. that  $\hat{C}_{TP}(1000,10,1)$  is closer to the upper bound  $(1-\frac{90}{1000})$   $\hat{C}_{SI}(1000,10)$  than to the lower bound  $(1-\frac{90}{1000})$   $\hat{C}(1000,10)$ . This implies that the test pattern increases channel capacity close to the point where almost full side information is available. Also it is seen that  $\hat{C}_{TP}(1000,10,1)$  is larger than  $\hat{C}(1000,10)$ , when  $P_h$  is larger than about 0.41. This implies that the test pattern with l=1 is useful for systems which suffer from severe jamming (interference) or systems which have so many users that the probability of hit is larger than 0.41. It is seen in

Fig. 9 that  $\hat{C}_{TP}(1000,10,9)$  is about middle of the upper bound  $(1-\frac{10}{1000})\,\hat{C}_{SI}(1000,10)$  and

Fig.8. Capacity of a interleaved variable-state block interference channel with a test pattern. M=1,000, b=10, t=90, l=1.

Fig.9. Capacity of a interleaved variable-state block interference channel with a test pattern. M=1,000, b=10, t=10, l=9.

the lower bound  $(1-\frac{10}{1000})$   $\hat{C}(1000,10)$ . This implies that the test pattern provides limited amount of side information to the decoder. Also it is seen that  $\hat{C}_{TP}(1000,10,9)$  is larger than  $\hat{C}(1000,10)$ , when  $p_h$  is larger than about 0.02. This implies that the test pattern with l=9 is useful for systems with both light and heavy interference.

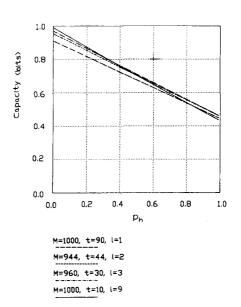

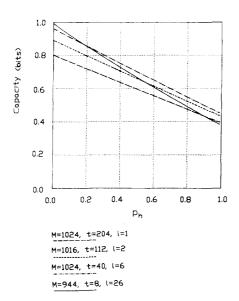

We plot channel capacities  $\hat{C}_{TP}(1000,10,1)$ ,  $\hat{C}_{TP}(944,10,2)$ ,  $\hat{C}_{TP}(960,10,3)$ , and  $\hat{C}_{TP}(1000,10,9)$  in Fig. 10. Block length M is selected such that t divides (M-t). Although block lengths are not selected to be same for various sub-block lengths, it is seen how the channel capacity is affected by the number of sub-blocks between adjacent test bits from the figure. We show the number of sub-blocks between test bits which gives the largest channel capacity for the selected values of  $P_h$  and b=10 in Table 1. It is seen that the number of sub-blocks between test bits to achieve the largest capacity decreases, that is, the number of test bits to achieve the largest capacity increases, as hit probability  $P_h$  increases.

We plot channel capacities  $\hat{C}_{TP}(M,b,l)$ ,  $\hat{C}(M,b)$ ,  $\hat{C}_{SI}(M,b)$ ,  $(1-\frac{t}{M})$   $\hat{C}(M,b)$ , and  $(1-\frac{t}{M})$   $\hat{C}_{SI}(M,b)$  for M=1,024, b=4, t=204, and l=1 in Fig. 11,

Fig.10. Capacities of interleaved variable-state block interference channel with various test patterns. b=10.

| Table 1. | Number of sub-blocks <i>l</i> between     |  |  |

|----------|-------------------------------------------|--|--|

|          | adjacent test bits to achieve the largest |  |  |

|          | channel capacity.                         |  |  |

| P <sub>h</sub> | ı      | М    |

|----------------|--------|------|

| 0. 1           |        | 1052 |

| 0. 15          | 8      |      |

| 0. 2           |        |      |

| 0. 25          |        |      |

| 0. 3           | 6 1036 |      |

| 0. 35          |        | 1036 |

| 0.4            |        |      |

| 0. 45          |        |      |

| 0.5            | 4      | 942  |

| 0. 55          |        |      |

| 0.6            |        |      |

| 0. 65          |        |      |

| 0.7            |        |      |

| 0. 75          | 3      | 960  |

| 0.8            |        |      |

| 0.85           |        |      |

| 0.9            |        |      |

| 0. 95          |        |      |

| 0. 99          |        |      |

Fig.11. Capacity of a interleaved variable-state block interference channel with a test M=1,024, b=4, t=204, l=1. pattern.

Fig.12. Capacity of a interleaved variable-state block interference channel with a test pattern. M=944, b=4, t=8, l=26.

and for M=944, b=4, t=8, and l=26 in Fig 12. It is seen in Fig. 11. that  $\hat{C}_{TP}(1024,4,1)$  is much closer to the upper bound  $(1 - \frac{204}{1024})$   $\hat{C}_{SI}(1024,4)$  than to the lower bound  $(1 - \frac{204}{1024})$   $\hat{C}(1024,4)$ . This implies that the test pattern increases channel capacity to the point where almost full side information is available. This is seen clearer in Fig. 11. than in Fig. 8. Also it is seen that  $C_{TP}$  (1024,4,1) is larger than C(1024,4), when  $P_h^{-}$  is larger than about 0.41. It is seen in Fig. 12. that  $\hat{C}_{TP}(944,4,26)$  is about middle of the upper bound  $(1 - \frac{8}{944})$   $\hat{C}_{SI}(944,4)$  than to the lower bound  $(1 - \frac{8}{944})$   $\hat{C}(944,4)$ . Also it is seen that  $\hat{C}_{TP}(944,4,26)$  is larger than  $\hat{C}(944,4)$ , when  $P_h$  is larger than about 0.005. This implies that the test pattern with l=26 is useful for systems with both light and heavy interference.

We plot channel capacities  $C_{TP}(1024,4,1)$ ,  $\hat{C}_{TP}(1016,4,2), \hat{C}_{TP}(1024,4,6), \text{ and } \hat{C}_{TP}(944,4,26)$ in Fig. 13. M is selected such that t divides (M-t). Although block lengths are not selected to be same for various sub-block lengths, it is seen how the channel capacity is affected by the number of sub-blocks between adjacent test ibts from the figure. We show the number of subblocks between test bits which gives the largest channel capacity for the selected values of  $P_h$

Fig.13. Capacities of interleaved variable-state block interference channel with various test patterns, b=4.

and b=4 in Table 2. As in Table 1 it is seen that the number of sub-blocks between test bits to achieve the largest capacity decreases, that is, the number of test bits to achieve the largest capacity increases, as hit probability  $P_h$  increases.

#### V. Conclusions

In this paper we modeled a variable-state block interference channel after asynchronous multislow frequency-hopped spread-spectrum systems subject to jamming or fading which suffer from bursts of interference of variable duration. We have presented a new test pattern technique for interleaved variable-state block interference channels. We have shown that the test patern increases the capacity of a interleaved variablestate block interference channel up to the point where almost full side information is available. We have shown that a block interference channel with a test pattern has larger capacity than the channel without test pattern, when hit probability is large. Also we have shown that the number of sub-blocks between test bits to achieve the largest capacity decreases, that is, the number of test bits to achieve the largest capacity increases, as hit probability increases.

Table 2. Number of sub-blocks *l* between adjacent test bits to achieve the largest channel capacity.

| Ph    | l      | M    |

|-------|--------|------|

| 0, 1  | 18     | 1090 |

| 0. 15 | 10     |      |

| 0. 2  | 12     | 1028 |

| 0. 25 | 11     | 1034 |

| 0.3   |        |      |

| 0. 35 | 10     | 1024 |

| 0.4   |        | 1022 |

| 0. 45 |        |      |

| 0. 5  | 8      |      |

| 0. 55 |        |      |

| 0.6   | 7      | 1014 |

| 0.65  |        | 1024 |

| 0.7   | 6 1024 |      |

| 0, 75 |        |      |

| 0.8   |        |      |

| 0. 85 |        |      |

| 0. 9  |        | 1028 |

| 0. 95 | 5      |      |

| 0. 99 |        |      |

#### References

- [1] J.H. Lee, Information and Coding for Channels with Block Interference, Ph.D. thesis, University of Michigan, 1986.

- [2] R.J. McEliece and W.E. Stark, "Channels with block interference," *IEEE Trans. Inform. Theory*, vol. IT-30, pp. 44-53, Jan. 1984.

- [3] E.R. Berlekamp, "The technology of error-correcting codes," *Proc. IEEE*, vol. 68, pp. 564-593, May 1980.

- [4] C. Heegard and A.A.E. Gamal, "On the capacity of computer memory with defects," *IEEE Trans. Inform. Theory*, vol. IT-29, pp. 731-739, Sep. 1983.

- [5] A.V. Kusnetov and B. S. Tsybakov, "Coding in a memory with defective cells," translated from Prob. Peredach. Inform., vol. 10, no. 2, pp. 52-60, April-June 1974. \*

### -著 者 紹 介---

#### 李 在 弘(正會員)

1953年 12月 7日生、1976年 2月 서울대학교 전자공학과 졸업 공학 사학위 취득. 1978年 2月 서울대 학교 대학원 전자공학과 졸업 공 학석사학위 취득、1986年 8月 미 국 Univ. of Michigan 졸업 공학박

사학위 취득. 1978年~1981年 해군사관학교 전자공 학과 교관, 전임강사. 1987年 2月~현재 서울대학 교 전자공학과 조교수. 주관심분야는 채널코우딩, 디 지틀통신, 위성 및 이동통신, 음성합성 등임.

# 呉 相 縣(準會員)

1964年 9月 24日生. 1987年 2月 서울대학교 전자공학과 졸업 공학 사학위 취득, 1989年 2월 서울대 학교 대학원 전자공학과 졸업 공 학석사학위 취득. 주관심분야는 디지틀통신, 신호처리, 정보이론 둥임.

#### Wayne E. Stark (正會員)

1978年 미국 Univ. of Illinois 전기 공학과 졸업 학사학위 취득. 1979 年 동 대학교 대학원 전기공학과 졸업 석사학위 취득. 1982年 동 대학원 전기공학과 졸업 박사학위 취득. 1982年~현재 미국 Univ. of

Michigan 전기공학 및 컴퓨터 과학과 조교수, 부교 수. 주관심분야는 정보이론, 코우딩이론, 통신이론 둥임.