# A Study on the Effect of P Concentrations of PSG Interlayers on the Yield Characteristics of the NMOS Devices

# (층간 절연막으로 쓰이는 PSG막의 P농도가 NMOS소자의 수율에 미치는 영향에 관한 연구)

金 聖 弼\*\* 朴 在 勤\*\*\* 趙 丙 燮\*, 郭 桂 達\*

(Seong Pil Kim, Jae Gun Park, Byung Seob Cho, and Kae Dal Kwack)

#### 要 約

본 연구에서는  $PSG(Phosphosilicate\ Glass)$  막을 일반화된 conveyorized 상압 화학기상증착법을 이용하여  $PH_3$ 와  $SiH_4$ 를  $N_2$ 분위기에서 산화시키는 방식으로 도포시켰으며, 인 농도의 측정에는 FT-IR 방법을 사용하였다.

인 농도의 증가에 따른 flow특성 식각율의 변화를 조사하였고, 특별히 인의 함유량과 수율과의 상관관계를 구하는데 주의를 기울였다. 결론적으로, NMOS로 구성된 1.2μm수준의 metal배선 간격을 갖는 256K DRAM의 경우 flow의 경사를 45±10°정도로 유지시키는 8~10wt% 정도의 인이 포함된 경우에 상당히 양호한 수율이 얻어점을 알 수 있었으며, 아울러 불량이 발생하는 원인에 대해서도 해석을 시도하였다.

#### Abstract

In this study, phosphosilicate glass (PSG) film was deposited by the oxidation of phosphine (PH<sub>3</sub>) and silane (SiH<sub>4</sub>) in nitrogen ambient with a conventional conveyerized Atmospheric Pressure Chemical Vapor Deposition (APCVD) system and phosphorus concentration is measured by using FT-IR technique.

The flow characteristics and etch rate variations of the films, depending on phosphorus concentrations, are investigated. Special emphasis is focused on the yield variations of NMOS-based 256K DRAM with 1.2  $\mu$ m metallization spacing with increasing phosphorus concentrations. As a result, the data indicates that the fairly good yield can be obtained within the range of between 8 and 10 wt% phosphorus concentration, which result in a slope of flow within 45  $\pm$  10°. The analysis of failure mechanism is also accompanied.

(Samsung Electronics.)

接受日字: 1989年 6月 30日

#### I. Introduction

The glass, which is widely used throughout the semiconductor industry as an interlayer dielectrics and for final passivation or scratch protection, is usually deposited by means of Chemical Vapor Deposition (CVD) [1,2]. Most of the glass depos-

<sup>\*</sup>正會員, 漢陽大學校 電子工學科

<sup>(</sup>Dept. of Elec. Eng., Hanyang Univ.)

<sup>\*\*</sup>準會員、漢陽大學校 電子工學科

<sup>(</sup>Dept. of Elec. Eng., Hanyang Univ.)

<sup>\*\*\*</sup>正會員,三星電子株式會社

ition processes suffer from poor coverage [3,4]. As a result even relatively beveled steps may turn into sharp steps after the deposition. If the angle of the slope and the sharpness of the corners of the step exceed critical values, opens may occur in the subsequent metallization. Alternatively, the metal may be continuous but has a reduced cross sectional area where it passes over a step. This results in a localized increase in current density and a higher probability of electron migration failure at that point. Therefore, the presence of the sharp steps adversely affect production yield and device reliability[3].

One of the processes, which is being generally accepted, is the glass flow technique [5]. This method makes use of the fact that the softening point of the doped glass can be lowered to the temperature which is not detrimental to the devices.

PSG is one of the representative materials for this purpose. It improves the cracking resistance of the glass by reducing the intrinsic stress and also has an ability to getter alkali ions [6]. In larger concentrations, phosphorus loweres the temperature at which the glass softens and begins to flow.

As the device dimensions are miniaturized, it is necessary to achieve shallower source/drain junctions, in order to minimize short channel effects and possible punch-through contributions to the current[4].

Therefore, it is necessary to keep the heat treatment after the formation of the source/drain junctions at low temperatures and as fast as possible. In that way, significant amounts of undesirable diffusions, such as drive-in or out-diffusion, can be avoided.

In general, it has been reported that a 50°C reduction in reflow temperature can be obtained with an increase of the phosphorus content as much as 3 wt% [5]. But a substantial increase in phosphorus concentration also creates a number of problems (e.g. the corrosion of aluminium metallization, leaching-out of significant phosphorus in moist ambients, and the shifts of threshold voltage in MOS devices due to the polarization phenomena.) [7-11].

As mentioned above, the properties of the PSG films are directly related to the phosphorus concentrations. In this paper, the flow characteristics and the etch rate variations of the films depending on phosphorus concentrations are

reviewed for confirmation. And special attention is paid for the extraction of yield data which depends on the phosphorus concentrations. The range of phosphorus concentration in the PSG in interlayer, which maintains a slope of step profile within  $45 \pm 10^{\circ}$ , is also proposed for the circuits (256K DRAM) using NMOS devices.

#### II. Experiment

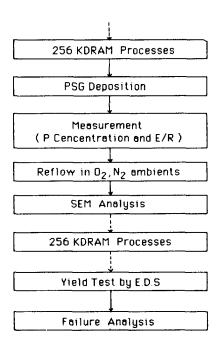

Overall experimental procedure is shown in Fig. 1. All the experiments were carried out on <100> - oriented, 6-inch, p-type boron doped silicon wafers with resistivity of 18  $\pm$  3  $\Omega$ -cm. The chemical reaction used to deposit the low temperature PSG films was the oxidation of SiH<sub>4</sub> and PH<sub>3</sub> using N<sub>2</sub> as the carrier gas. In this reaction, the flow rates for SiH<sub>4</sub>, O<sub>2</sub>, and N<sub>2</sub> were 82 (SCCM), 1.57 and 12 (SLM), respectively. The flow rate of PH<sub>3</sub> takes 4 types of 230, 280, 328 and 380 (SCCM), respectively. Using this conditions with a substrate temperature of 380°C, 6000 A-thick PSG films were deposited. Conventional conveyorized Atmospheric Pressure CVD system was used.

Fig.1. Process Sequence.

After completing deposition process, some of as-deposited test wafers were picked up to measure phosphorus concentrations. As a measuring technique, Fourier Transform Infrared of Spectroscopy (FT-IR) method, which evaluates concentrations of specific materials through the use of absorbance spectra, was used. In this case, the ratio of spectra at 1330 cm<sup>-1</sup>(P=O band) and at 825 cm<sup>-1</sup> (Si-O band) was used to evaluate phosphorus concentrations of the PSG films. And then, the wafers were exposed to the etchant, called B.O.E. (Buffered Oxide Etchant NH4F: HF = 7: 1). By measuring the film thicknesses, the etch rates of the PSG layers depending on various phosphorus concentrations were determined.

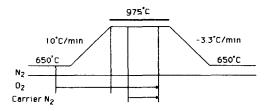

Meanwhile, RUN wafers, which have experienced deposition process, were ready to reflow. Details on this process is illustrated in Fig. 2.

Fig. 2. PSG reflow conditions.

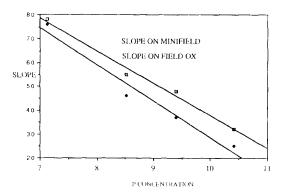

Thereafter, the flow characteristics of the PSG interlayer were investigated by SEM analysis. The slope of the step profile is also calculated from this micrographs at just above both the minifield oxide and the field oxide.

After performing the total procedure, yield test was carried out finally. Electrical Die Sort (E.D.S.) was used to estimate success or failure. If there were too many failures, the analysis of the failure mechanism was also tried.

# III. Results and Discussion

# Phosphorus Concentrations of PSG Films vs PH<sub>3</sub>

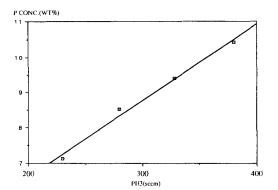

It has been reported that the phosphorus concentration in the PSG film is linearly proportional to the inlet PH<sub>3</sub> concentration [12]. This

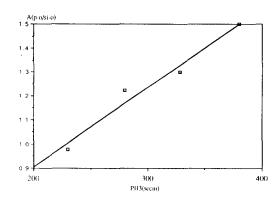

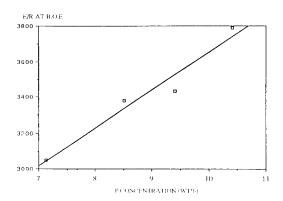

is confirmed here again. As shown in Fig.3, the data can be interpolated in an almost linear manner. The ratio of absorbance height (P=O band at 1330 cm<sup>-1</sup>/Si-O band at 825 cm<sup>-1</sup>) also shows linear relation to the phosphorus concentration of the PSG film. As shown in Fig.4, this results are in good agreements with Fig.3.

Fig.3. P concentration vs PH<sub>3</sub>.

Fig.4. Absorbance ratio vs PH<sub>3</sub>.

#### 2. Etch Rate vs Phosphorus Concentration

With increasing phosphorus concentration, the etch rate of PSG film increases also. The reason is that the increase of phosphorus content in the PSG film, most of which are inhibit in the form of  $P_2O_5$ , stimulates the reaction between HF and  $P_2O_5$  in B.O.E. and results in a linear dependence as shown in Fig.5. The results agreed well with the previous one [13].

Fig. 5. Etch rate vs P concentration.

From the physical point of view, the etch rate variation depending on various phosphorus content can be interpreted by using the concept of degradation of the film hardness, i.e., the increase of phosphorus content in the PSG film lowers the viscosity and is responsible for the increased etch rate. Details of this mechanism will be presented in the following.

# 3. Flow Profile vs Phosphorus Concentration

Glass flow, a process for the improvement of as-deposited glass film, is affected by the following factors; surface tension, which improves curvature of the surface and has a tendency to minimize surface area, as a driving force of glass flow, and viscosity, which motivates the glass flow.

In our experiment, only the effect of phosphorus concentration on the flow profile is considered and can be explained in the following manner.

Increasing the temperature reduces the viscosity of the glass structure for two reasons [14,15].: (1) There is an increased thermal energy available for the rehybridization of Si-O-Si bond, permitting an increased degree of twisting and flexing in the network without actually breaking any covalent bonds. This is the dominant contribution at lower temperatures. (2) At higher temperatures, the thermal energy is sufficient to break covalent bonds, leaving any electrostatic bonding forces. In this case the electron would be expected to remain associated with the oxygen

atom, owing to its considerably higher electronegativity:

$$\geq si - 0 - si \leq \rightarrow \geq si^{\dagger} + i \ddot{0} - si \leq$$

As the temperature increases the process of conversion from predominantly covalent to predominantly ionic bonding can be expected to continue, resulting a further reduction in the viscosity of the melt.

Dangling bonds also contribute to PSG flow. These bonds at the glass surface react with the moisture at that site, and form hydroxyl groups (OH) of the following forms.

$$\geqslant \text{Si} - 0 - \text{Si} \leqslant + \text{H}_20 \rightarrow 2 \geqslant \text{Si} - 0H$$

$$- P = + \text{H}_20 \rightarrow - P$$

The binding energy of the covalent bond is 30-100 Kcal/mol, while that of hydrogen bond is 5-12 Kcal/mol. Therefore, the softening point and viscosity of the glass film can be further improved in steam ambients than in  $O_2$  or  $N_2$  ambients.

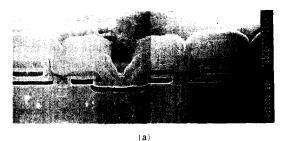

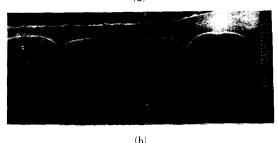

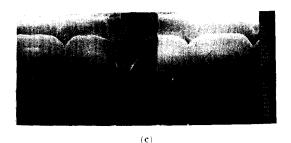

As a result, the high reflow temperature accellerates the conversion from covalent bond to ionic bond and an increase of phosphorus concentration serves as the hydroxyl group former and also increases nonbridging oxygen bonds, which reduces the viscosity and result in a smooth topography of the step. This is shown in Fig. 6. From this picture, we can observe that the flow profile of the PSG film is improved with increasing phosphorus concentration. The slope of flow profile at just above both the minifield oxide and the field oxide are plotted in Fig.7. This plot confirms the above argument.

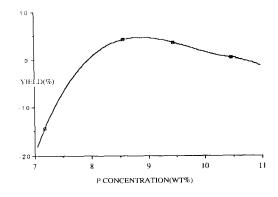

# 4. Yield vs Phosphorus Concentration

Decreasing phosphorus concentration to less than 9 wt% results in a drastical linear decrease of E.D.S. yield. This decrease is mainly due to the opening failure of metallization by the bad step coverage ascribed to the increase of the slope of flow profile by 60° or more. On the contrary, when phosphorus concentration increases over 9 wt%, E.D.S. yield also decreases linearly but

Fig.6. SEM cross-section view of PSG film after flow in N2 and O2 ambients for (a) 7 wt%, (b) 8.5 wt%, (c) 9.4 wt%, (d) 10.4 wt% P concentrations.

slowly. This is mainly because the slope profile of the PSG interlayer is too much improved and results in a partial stripping of the film, especially, in the periphery region where aspect ratio is very large (for instance, in 256K DRAM with 1.2  $\mu$ m metal line spacing), and the stripped oxide layers are exposed to the following metallization procedure. Thus, unexpected connections between

Fig.7. Flow profile vs P concentration.

the metal and the oxide layers are constructed.

In addition, further increase of phosphorus concentration is apt to cause the corrosion of the aluminium metal line as in reference[7]. Therefore, special care is needed for the control of phosphorus concentrations.

To get the maximum yield of 256 K DRAM with the metal line spacing of 1.2  $\mu$ m, the slope of flow profile within is needed to be within  $45 \pm 10^{\circ}$ . For this, we conclude that phosphorus concentration of the PSG interlayer must be controlled to stay within about 8-10 wt%. The results of yield test by E.D.S. is plotted in Fig.8.

Fig. 8. vield vs P concentration.

#### IV. Conclusion

In this study the yield dependence on the phosphorus concentration in the PSG interlayer is investigated, especially for NMOS devices (i.e. 256K DRAM). Such work is necessary to set up specifications needed by each producers.

To get maximum yield, the slope of flow profile is to be maintained within  $45 \pm 10^{\circ}$  for NMOS 256K DRAM with 1.2  $\mu$ m metal line spacing. Our results indicate that the phosphorus concentration between 8-10 wt% is desirable for this condition.

The study on the yield characteristics depending on the temperature,  $O_2$ ,  $N_2$  and  $SiH_4$  flow rates, must be followed in the near future, too.

#### Reference

- [1] W. Kern, "Thin film technology for advanced semiconductors/Part 2b-dielectrics," Semicon. International, pp. 121-129, July 1985.

- [2] L.W. Winkle and C.W. Nelson, "Improved atmospheric-pressure chemical-vapor-deposition system for depositing silica and phosphosilicate glass thin films," Solid State Technol., pp. 123-128, Oct. 1981.

- [3] J.L. Vossen et al., "Processes for multilevel metallization," J. Vac. Sci. Technol., vol. 11, no. 1, pp. 60-70, Jan./Feb. 1974.

- [4] R.M. Levin and K.E. Lutterodt, "The step coverage of undoped and phosphorus-doped SiO<sub>2</sub> Glass Films," J. Vac. Sci. Technol. B, vol. 1, no. 1, pp. 54-61, Jan.-Mar. 1983.

- [5] A.C. Adams and C.D. Capio, "Planariation of phosphorus-doped silicon dioxide," J. "Electrochem. Soc., vol. 128, no. 2, pp. 423-429, Feb. 1981.

- [6] J.M. Eldridge and D.R. Kerr, "Sodium ion drift through phosphosilicate glass-SiO<sub>2</sub>

- Films," J. Electrochem. Soc., vol. 118, no. 6, pp. 986-991, June 1971.

- [7] R.B. Comizzoli, "Aluminium corrosion in the presence of phosphosilicate glass and moisture," RCA Rev., pp. 483-490, April 1976.

- [8] N. Nagasima et al., "Interaction between phosphosilicate glass films and water," J. Electrochem Soc., vol. 121, no. 3, pp. 434-438, March 1974,

- [9] R.M. Levin, "Water absorption and densification of phosphosilicate glass films," J. Electrochem. Soc., vol. 129, no. 8, pp. 1765-1770, Aug. 1982.

- [10] P. Balk and J.M. Eldridge, "Phosphosilicate glass stabilization of FET devices," *Proc. of IEEE*, vol. 57, no. 9, pp. 1558-1563, Sept. 1969.

- [11] E.H. Snow and B.E. Deal, "Polarization phenomena and other properties of phosphosilicate glass films on silicon," J. Electrochem. Soc., vol. 113, no. 3, pp. 263-269, March 1966.

- [12] M. Shibata and K. Sugawara, "Deposition rate and phosphorus concentration of phosphosilicate glass films in relation to PH<sub>3</sub>/SiH<sub>4</sub> + PH<sub>3</sub> Mole Fraction," J. Electrochem. Soc. vol., no. 1, pp. 157-158, Jan. 1975.

- [13] W.A. Pliskin and G.P. Gnall, "Evidence for oxidation growth at the oxide-silicon interface from controlled etch studies," *J. Electrochem. Soc.*, vol. 111, no. 2, pp. 872-873, July 1964.

- [14] L.D. Pye, "Introduction to glass science," Plenum Press., pp. 31-59, 1972.

- [15] 홍성련, "BPSG 막의 Flow 특성에 관한 연구", 인하대학교 석사학위 청구 논문, 1987.

#### 金 聖 弼(準會員)

1966年 2月 28日生. 1988年 2 月 한양대학교 전자공학과 졸업. 공학사 학위 취득. 1988年 3月~현 재 한양대학교 전자공학과 석사과 정. 1989年 3月~현재 국립공업시 험원 연구생. 주관심분야는 반도

체 공정 및 화합물 반도체 소자 분야임.

# 朴 在 勤(正會員)

1959年 7月 27日生. 1985年 2月 동아대학교 전자공학과 졸업 공학사 학위 취득. 1988年 8月 한양대학교 산업대학원 전자공학과 졸업 공학석사 학위취득. 1985年 1月~현재 삼성전자 반도체 사업부 근무. 주관심 분야는 웨이퍼 material 분석 및 특성개선 D-RAM소자의 공정 개선등임.

# 趙 丙 燮(正會員)

1952年 3月 8日生. 1984年 2 月 한양대학교 전자공학과 졸업. 공학사 학위 취득. 1989年 3月~ 현재 동대학원 재학중. 주관심분 야 Power 디바이스 및 반도체 공 정분야.

# 郭 桂 達(正會員)

1950年 2月 13日生. 1981年 ~ 현재 한양대학교 전자공학과 부 교수. 주관심분야는 GaAs SRAM 의 설계와 이와 관련된 circuit extractor의 개발, submicron device의 특성해석을 위한 2-D및

3-D simulator 개발, high-speed 및 power용 반도체 소자의 개발등임.