# 대역 확산 통신방식에서 고속 주파수 호핑 시스템에 사용될 주파수 합성기의 실현에 관한 연구

A Styudy on the Implementation of Frequency Synthesizer for the Fast Frequency Hopping Spread Spectrum Communication system

\*金 元 厚(Kim, W. H.)

# 요 약

고속 주파수 호핑 시스템을 구성하기 위해서는 무엇보다 천이 시간이 매우 짧은 주파수 합성기가 필요하다. 본 논문에서는 천이 시간이 수 nS 정도로 극히 짧은 직접 디지를 주파수 합성기를 실현하고 그 특성을 실험하였다. 또한 호핑 특성을 검토함으로써 본 논문에서 구성한 주파수 합성기가 고속 주파수 호핑 시스템에 적합함을 확인하였다. 다. 마지막으로 현재의 기술수준으로 신호 대 잡음비(SNR)를 획기적으로 증가시키고 아울러 시스템 구성을 간단히 할 수 있는 개선 방법을 제시하였다.

#### ABSTRACT

The frequency synthesizer that has very short transient time is the key to construct the Fast Frequency Hopping(FFH) system.

A Direct Digital Frequency Synthesizer(DDFS) whose transient time is in the nS range has been implemented and the performance of which has been examined through this paper.

And by considering the hopping characteristic it is confirmed that the DDFS is suitable for the \*한국항공대학 교수(공항박사)

#### FFH system.

Finally an improvement method which can greatly enhances the SNR with the state-of-the-art techniques and simplifies the system design is presented.

# Ⅰ. 서 론

새로운 통신 방식으로 주목받고 있는 대역확산 (SS:Spread Spectrum) 통신 방식은 다원 접속 기능과 고도의 비화성, 그리고 잡음과 간섭 및 방해 파의 제거 능력 등 다른 통선 방식에서는 찾아보기어려운 특징을 가지고 있어 세계 제2차 대전으로 추정되는 개발 초기에는 주로 군사용으로 사용되었으나 1978년 CCIR 총회에서 과밀한 주파수 대역의효율적 이용을 위해 일반에 공개된 것을 계기로 현재는 민간 통신용으로도 활발히 연구되고 있다<sup>(1)</sup>.

이러한 SS 통신 방식 중에서 주파수 호핑(FH: Frequency Hopping) 방식은 PN(Pseudo Noise)코드의 패턴에 따라 반송파 주파수를 불연속적으로 변화시키는 방식으로 주로 이동 통신이나 항공우주통신에 이용되고 있다<sup>(2), (3)</sup>.

FH 방식에서 중요한 파라미터 가운데 하나로 호핑 속도를 들 수 있는데 고속(Fast) FH 방식이 저속(Slow) FH 방식보다 방해 신호나 페이딩 등에도 우수한 통산 품질을 제공하는 것으로 알려져 있으나<sup>[4]</sup> 호핑시에 소요되는 천이시간의 문제로 FFH시스템의 실현이 어려웠다.

FH시스템에서 호핑 반송파를 얻기 위한 주파수 합성기로는 직접 방식과 간접 방식, 그리고 디지틀 방식(5)이 알려져 있는데 이 중 직접 방식은 하나또는 그 이상의 기준 주파수에 분주와 체배를 가합으로써 다수의 출력 주파수를 얻는 것으로 천이 시간이 거의 발생하지 않지만 호핑 주파수 갯수가 중가할수록 시스템 구성이 복잡해지고 부퇴가 커지는등의 단점이 있어 실용성이 떨어지고, 간접 방식인 PLL(Phase Locked Loop)주파수 합성기는 출력주

파수 대역이 넓고 비교적 우수한 SNR을 가지고 있어 현재 주파수 합성기의 주종을 이루지만 궤환 루 프의 특성상 Locking 시간의 지연<sup>(6)</sup>으로 FFH 시스 템에는 적합하지 않다.

이에 비하여 디지를 방식은 샘플링 어론과 D/A 변환 기술을 근거로 출력 파형을 합성하는 방식으로 주파수 해상도 및 안정도가 뛰어나고 발생 주파수의 변화가 연속위상을 이루므로 Coherent 통신이가능하고, 더우기 천이 시간이 nS 단위로 매우 짧아서 FFH시스템에 직합하다.

본 논문에서는 고속 주파수 호핑 시스템용 직접 디지를 주파수 합성기(DDFS:Direct Digital Frequency synthesizer)를 단일 Look-up table을 이용하여 실현하고 그 특성을 실험하였다. 또한 현재의기술 수준으로 SNR을 개선시키는 방법으로 table의 어드레스 공유 기술과 D/A 변환기 다단화 기술을 도입하고 아울러 기존의 DDFS에서 샘플치 계산에 이용되던 하드웨어적인 복소 승산 과정을 제기시킴으로써 시스템 구성을 간소화시킨 새로운 설계 방법을 제시하였다.

# 2. 디지를 주파수 합성가의 특성

#### 2~1. 기본 개념

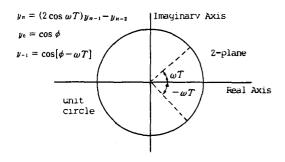

디지탈 주파수 합성기에서 정현 샘플치를 얻기 위한 방법으로는 우선 Z-변환이 단위원상에 국점을 갖는 차동 방정식을 이용한 디지를 순환 오실례이터 (recursion oscillator)를 고려하여, 여기에 적당한 초기치를 가하여 그림2-1과 같은 정현 샘플치를 얻는다.

그런데 여기에는 적어도 두가지 문제가 발생한다. 즉 출력 생플치가 완전한 정현값이 아니기 때문에 순환 횟수에 따라 잡음이 중가하고, 주파수 선택변수에 2coswT가 포함되어 다지를 연산에서 이것을 유한 길이의 비트로 나타낼 때 원하는 주파수와는 다른 주파수가 발생될 수도 있다.

그림2-1 정현 생품을 위한 극점 위치 Pole position for sinusoidal samples.

따라서 순환 오실레이터는 완벽한 해결책이 되지 못하여 이와 유사한 수치적 근사 방법으로 정현 샘 플치를 구한다. 즉, 각 샘플링 순간마다 Table 에 기록된 값에 연산을 가함으로써 정현 샘플치를 구 한다. 이 때 연산의 크기는 근사 정도와 허용할 오 차(즉 SNR)에 따라 결정된다.

다음을 생각하면

$$\cos 2 \pi f_n T = R_e \exp[j 2 \pi f_n T]$$

$$\sin 2 \pi f_n T = I_m \exp[j 2 \pi f_n T]$$

(2-1)

여기서 f=kf<sub>0</sub>, f<sub>0</sub>는 최하 주파수, n은 시간인덱스 (index), 그리고 T는 샘플치의 간격으로 최하 주파수 f<sub>0</sub>의 배수 주파수를 재산할 수 있다.

1₀=1/NT로 결정되므로 지수항은

$$\exp[j 2\pi f_n T] = \exp[j \frac{2\pi}{N} nk] \qquad (2-2)$$

로 나타낼 수 있다.

이 복소 지수 샘플치는 f=k/NT인 변수 2πfnT의 사인 및 코사인 값과 같다.

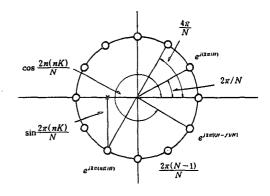

이와 같이 주파수 인덱스 k와 시간 인덱스 n을 기준으로 복소 지수 샘플치를 계산하는 것은 그림 2-2와 같은 단위원상에 동간격인 N개의 값 중에서 하나를 구하는 것과 같다.

$$\exp[j0], \exp[j\frac{2\pi}{N}], \exp[j\frac{2\pi}{N}2], \dots,$$

$\exp[j\frac{2\pi}{N}(N-1)]$

그림2-2 단위원 상의 등간격 생풀치 Equi spaced samples on the unit circle.

어떤 주파수 인덱스 k에 대하여 지수항의 변수는  $(2\pi/N)_k$  만큼씩 증가하고 모든 X에 대하여

$$\exp[i(2\pi/N)(x+N)] = \exp[i(2\pi/N)x]$$

이므로 nk는 modulo-N으로 계산된다. 따라서 복소 정현 샘플치를 발생시킬 때 k의 배수(축 N인 순간 에 nk일 때 다음 순간인 n+1에는 (n+1)k)로누 적되도록 하고 이를 이용하여 exp[j(2 $\pi$ /N)nk]를 계산한다. k를 누적시킬 때 어큐율래이터(Accumulator)의 초기치가 "O"이 아닐 경우 지수항은 exp[j(2 $\pi$ /N)(nk+c)]가 되어 출력 주파수의 위상 에 영향을 준다. exp[j (2π/N) (nk+c)] = exp[j (2π/N) Y] 몰 결정할 때, 가장 간단한 경우로 exp[j (2π O/N)] 에서 exp[j2π (N-1)/N] 까지 N개의 값을 가진 Table을 고려하면 어큐율레이터의 누적값 Y를 이용하여 복소 샘플치를 구할 수 있다. Y가 중가함에 따라 Table로 부터 정현 샘플치를 얻으며 k가 클수록정현 샘플치의 간격이 커진다.

이러한 방법은 N의 갯수가 적을 때에는 적합하지 만 다수의 출력주파수를 얻기 위해서는 N도 따라서 커져야 하므로 단일 Table Look-up 방식에서는 출 력 주파수 갯수만큼의 메모리 수가 필요하게 되어 메모리의 크기면에서 불합리하다.

N이 크고 0 ≤Y≤N-1일 때, Y를 몇 부분으로 분리시킬 수 있다. 만일 Y=q+r+s 이라면

$$\exp\left[i\frac{2\pi}{N}Y\right] = \exp\left[i\frac{2\pi}{N}(q+r+s)\right]$$

$$= \exp\left[i\frac{2\pi}{N}q\right] \cdot \exp\left[i\frac{2\pi}{N}r\right] \cdot \exp\left[i\frac{2\pi}{N}s\right] (2-3)$$

로 나타낼 수 있으므로 전체 메모리 수를 감소시킬 수 있다. 예를 들어 N이 2의 멱숭이라면 즉 N=2° 이면 0≤Y≤2°-1이고 이 때 Y는 길이가 b비트 인 2진 word로 다음과 같이 표시할 수 있다.

$$Y = a_0 2^0 + a_1 2^1 + a_2 2^2 + \dots + a_{n-1} 2^{n-1}$$

(2-4)

지수항을 b개로 나눌 때 각각은 exp[j 2 # a t 2 t / N], a t = 0. or 1로 표시된다. 따라서 Table은 2 b 개의 복소값 중에서 b 개의 복소값과 (b-1) 번의 복소승산으로서

$$\exp\left[j\frac{2\pi}{N}Y\right] = \exp\left[j\left(\frac{2\pi}{N}\right)\left(nk+c\right)\right]$$

를 구할 수

있다. 이렇게 복소 지수향을 분리시키면 메모리를 효과적으로 이용할 수 있을뿐 아니라 위상자이 작 더라도 정현 샘플치를 근사시킬 수 있어 유리하다. 일반적으로 Table을 n개로 나누고 (n-1)회의 복 소 승산으로 샘플치를 구할 때 얻어지는 최대 출력 주파수 갯수F는 다음과 같이 나타났다.

$$F = (\frac{N}{n})^{n-1}$$

(2-5)

이며 필요한 메모리 총수 S는

$$S = (n \cdot F)^{\frac{1}{n}} \tag{2-6}$$

로 주어진다.

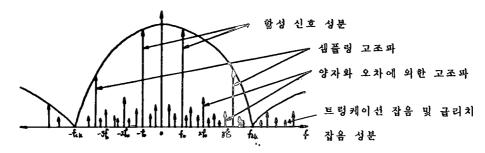

#### 2-2. 스펙트럼과 SNR

디지를 주파수 합성기는 출력 정현파의 샘플치를 미리 위상 대 진폭변환기(Phase to Amplitude Converter 또는 Look-up table)에 기록해 두고 매 클럭마다 k 값에 따른 샘플치를 구한 후 이를 다시 D/A 변환기와 저역 통과 필터(LPF)를 거쳐 출력 파형을 합성하는 방식으로 기존의 PLL(Phase Locked Loop)주파수 합성기와는 다른 스펙트럼 특성을 가지며 정현 샘플치를 Look-up table에 기록할때 필연적으로 위상 양자화 및 진폭 양자화에 따른 잡음이 수반되어 SNR을 결정짓는 주된 요인으로 작용하다.

이 밖에도 샘플치의 계산 과정에서 발생하는 트렁 케이션 잡음과 D/A 변환기에서 발생되는 글리치 (Glitch) 잡음 및 LPF를 거친 샘플링 고조파 등이 성능 열화 요인이 된다.

양자화 오차의 영향을 고려할 때 먼저 양자화 오차가 없는 이상적인 경우로 발생하려는 정현신호를 f(t)라 하고 n번째 샘플치를  $f_n$ 이라 하면 D/A 변환기를 거쳐 얻어진 합성 신호 $f_s(t)$ 는

$$f_s(t) = \sum_{n} f_n \delta(t - nT) \qquad (2 - 7)$$

로 주어지고

f(t)는  $f_s(t)$ 를 차단 주파수가  $w_m$ 인 LPF를 거쳐 얻어진다. 여기서 이상적인 LPF를 가정하면  $f_s(t)$ 와의 Convolusion 으로

$$f(t) = \sum_{n} f_n \delta(t - nT) * \frac{\sin(w_m t)}{w_m t}$$

$$= \sum_{n} f_{n} \operatorname{sinc} \left( \frac{w_{m} t}{\pi} - n \right)$$

(2-8)

그러나  $f_n$ 에는 양자화에 따른 오차가 필연적으로 포함되므로 이것을  $f_n'$ 이라 할 때 출력 정현신호f'(t)는

$$f'(t) = \sum_{n} f'_n \text{ sinc } \left( \frac{\mathbf{w}_m t}{\pi} - \mathbf{n} \right)$$

(2-9)

으로 주어진다.

따라서 오차 신호 e(t)는

$$e(t) = f(t) - f'(t)$$

$$= \sum_{\mathbf{n}} (f_{\mathbf{n}} - f'_{\mathbf{n}}) \operatorname{sinc} \left( \frac{\mathbf{w}_{\mathbf{m}} t}{\pi} - \mathbf{n} \right)$$

(2 - 10)

그런데 순시 오차 en=fn-fn 이므로

$$e(t) = \sum_{n} e_{n} \operatorname{sinc} \left( \frac{w_{m} t}{\pi} - n \right)$$

(2-11)

이 된다. 윗 식으로 부터 양자화 오차의 기본 주파 수는 발생 신호 주파수와 일치하며 오차의 스펙트 럼은 발생 주파수의 고조파로 나타남을 알 수 있다.

또한 진폭 양자화에 따른 SNR은 (7)

SNR

$$\approx \frac{3}{2} (2^{A} - 1)^{3}$$

(2-12)

이며 여기서 A는 진폭 양자화 비트수이다. 이를데 시벨로 나타내면

$$SNR \cong 6A + 1.75 \text{ (dB)}$$

(2 - 13)

가 되며 위상 양자화에 따른 SNR 은

$$SNR \cong 6.8 (2^{28})$$

(2-14)

이며 이를 데시벨로 나타내면

$$SNR_{dB} \cong 6B - 8.3 (dB)$$

(2 - 15)

여기서 B는 위상 양자화 비트 수이다. 식(2-13) 과 (2-15)를 벡터적으로 합성하면 위상 양자화와 진폭 양자화를 모두 고려한 경우로 다음 근사식을 얻는다.

$$SNR_{aB} \cong -10\log\sqrt{\frac{0.44}{2^{4A}} + \frac{46.0}{2^{4B}}}$$

(2-16)

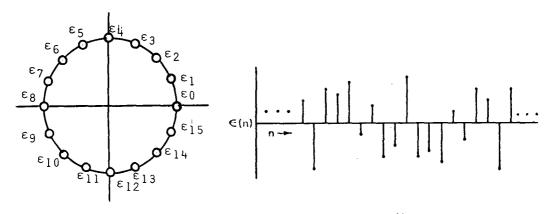

한편 임외의 주파수를 발생시킬 때 샘플값을 계산하는 과정에서 발생하는 트렁케이션잡음은 최악의 경우에 1/NT로 나타나고 따라서  $f_0=1/NT$  인주파수 간격으로 선스펙트럼이 나타난다. 그런데 출력 주파수가 2'k일 경우에 트렁케이션 잡음의 고조파는 2'k의 배수로 나타난다. 그림2-3에는 단위원 상의 샘플수 N이 16일 경우에 k를, 증가시킴에 따른 트렁케이션 잡음의 발생 관계를 나타내었다.

2의 멱승 형태인 (1), (2), (4)는 잡음 주기가 발생 주파수의 주기와 일치하고 2의 멱승이 아닌 (3),(5), (7)은 최장 주기인 16T이며 (6)에서는 우수 성분만 밤생된다.

트렁케이션 잡음의 주기는 최고 N개의 샘플수만 큼이므로 N개의 샘플치에 대한 잡음 전력은 Parseval의 관계에 따라

Frequency

Noise Period

(1) Lowest 1/16T Noise period same as generated period = 16T

(2) 1/8T Noise period same as generated period = 8T

(3) " 3/16T 0 3 6 9 12 15 2 5 8 11 14 1 4 7 10 13=16T

(4) " T/4 Noise period same as generated period = 4T

(5) " 5/16T 0 5 10 15 4 9 14 3 8 13 2 7 12 1 6 11=16T

(6) 7/16T 0 6 12 2 8 14 1 10 0 = 8T

(7) Highest 7/16T 0 7 14 5 12 3 10 1 8 15 6 13 4 11 2 9 = 16T

그림2-3 N=16일 때 트럼웨이션 잡음의 발생 Generation of truncation noise when N=16.

$$\sum_{t=0}^{N-1} |F_t|^2 = N \sum_{t=0}^{N-1} \epsilon_n^t$$

(2-17)

여기서  $\epsilon_n$ 은 샘플치에서의 오차 진폭이며  $F_i$ 는 i번 째 주파수에서의 잡음 진폭으로 다음으로 정외된다.

$$F_{i} = \sum_{t=0}^{N-1} \epsilon_{t} \exp[-i\frac{2\pi}{N} it]$$

(2-18)

€n은 양자화 구간내에서일양하게 분포된의사 랜덤 변수이므로 X비트로 양자화할 경우에 -2-\*에서2-\* 사이의 값을 갖는다. 최악의 경우로 €n이 2-\* 이라 면,

$$|F|^2 = N^2 (2^{-x})^2$$

or  $|F| = N 2^{-x}$

이고 발생 주파수의 진폭은 N이므로 잡음 진폭대 신호 진폭비는 2<sup>-\*</sup>가 되며 이를 dB로 나타내면 약 -6xdB이다.

출력 주파수를 위한 생물치를 완벽하게 얻었다고 하더라도 D/A 변환기에서 각 비트마다의 스위칭시 간 차에 의해서 출력 파형에 글리치가 발생된다. 이 글리치 성분은 D/A 변환기에 가해지는 병렬 데이터 의 변화가 심할수록 크게 나타난다. 잡음 필스폭을 △라고 하고 한 주기마다 한번씩 글리치가 발생된 다고 하면 잡음대 신호비는 △/NT의 비율로 나타 난다. 따라서 발생 주파수가 높을수록 이비율은커 진다.

D/A 변환가에 의한 글리치 잡음을 줄이기 위해서 는 천이 시간에는 D/A 변환기의 출력을 버퍼링(Bu-

그림2-4 DDFS의 출력 스펙트럼 Output spectrum of DDFS.

ffering) 할 필요가 있다. 또한 D/A변환기의 출력은 완전한 정현파가 아니라 직류 스템으로 나타나는 외사 정현파로 샘플링 시간이 T일 때 출력스펙트립에는 샘플링 고조파가 포함된다. 그러므로D/A변환기의 출력파형을 정형하고 샘플링 고조파를 제거하는 LPF의 대역은 1/4T로 하는 것이 유리하며 최대한 1/2T 이내이어야 한다.

이상에서 고려한 디지틀 주파수 합성기의 스펙트 럼 특성은 다음 그림과 같다.

#### 3. DDFS의 설계

## 3-1. 동작 원리

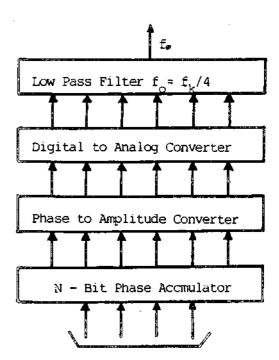

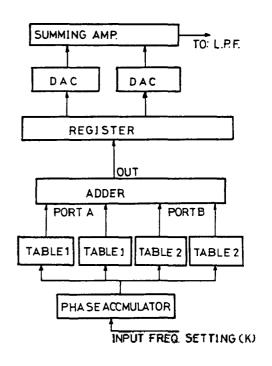

다음 그림은 DDFS의 동작 계통도를 나타낸 것이다.

첫 부분은 위상 어큐뮬레이터로 발생 주파수 범위와 해상도를 결정한다. 위상 어큐뮬레이터는 단순한 N비트 2전 어큐뮬레이터로 입력 데이터비트의 조합 K를 초기 위상각 스템으로 받아들여 매생플링 클릭마다 K를 누적시키며 새로운 위상 데이터를 발생시킨다. 이 때 위상 데이터는 0 에서 2π사이의 값에 해당되며 2π 이상이 되면 오버플로우를 발생시킨으로써 출력 파형의 한 주기를 형성하고 그 차에 해당하는 위상각을 K값과 다시 누적시켜 다음 한주기 파형을 합성한다. 이 동작은 초기위상각 스템 k가 변화될 때까지 계속 반복되며 K의

Frequency Control Number (K)

그림3-1 DDFS의 동작 계통도 Ouperation diagram of DDFS.

변화로 출력 주파수가 변화된다.

k가 (k+R)로 변화하는 순간에 위상 어큐뮬레이터가 임의의 어떤 값 C를 가지고 있다면 다음색 플링 클럭이 가해질 때 위상 어큐뮬레이터의 출력 은 k+R+C가 되어 연속위상을 이루며 (k+R)에 해당하는 재로운 주파수를 발생시킨다. 또한 새로운 주파수가 발생될 때 소요되는 천이 자간도 위상어큐뮬레이터 출력 상으로는 최대한 클럭주기에 해당하는 시간이 소요되지만 실제로는 샘플링 가해지는 순간에 새로운 위상각 스텝으로 누적되므로어큐뮬레이터의 처리 속도에 해당하는 nS 정도의 천이시간이 소요되는 셈이다.

출력 주과수 (는 시간인덱스인 클릭 주과수 fcx 와 위상 어큐뮬레이터의 길이 N, 그리고 주과수인 덱스 K의 관계에 따라 다음과 같이 결정된다.

$$f = K \cdot f_{CK} / 2^N \tag{4-1}$$

여기서 위상어큐뮬레이터의 길이가 N비트이므로 단위원 상의 등간격위상샘플치는 2<sup>™</sup>개가 된다. 또한 K는 2진 데이터에 의한 정수값이므로 f는 K와 fcx/2<sup>™</sup>의 곱으로 나타나고 fcx/2<sup>™</sup>은 주파수해상도를 나타낸다. 위상 대 진폭 변환기는 K의누적값으로 얻어지는 순시위상각에 대한 진폭차를 얻기 위한 것으로 Look-up Table (또는 이와 같은 기능을 수행하도록 프로그램된 ROM)을 이용한다.이때 저장되는 데이터는 등간격의 위상각에 따른 진폭치를 다음 식에 따라 기록한다.

D=2\* · sin

$$(2\pi K/2^{N-1})$$

$(K=1, 2, \dots, 2^{N})$  (3-2)

여기서 D는 진폭 데이터 값이고 x는 진폭 데이터 비트 수이며 $2\pi/2^{N-1}$ 은 최소 위상각 스텝이다.

D/A 변환기는 샘플링 클릭마다 Table로 얻어지는 병렬2진 진폭 데이터를 하나의 아날로그 값으로 변환시키며 LPF는 D/A 변환기 출력의 불연속 성분을 보완하고 샘플링 고조파를 제거 시킴으로써 출력 정현파를 얻도록 한다.

#### 3-2. 실험 모델 설계

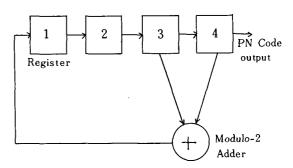

본 논문에서는 시스템 구성을 간단히 하기 위하여 단일 Table을 이용한 DDFS를 설계 제작하고 그 호핑 특성을 검토하기 위하여 4단 최장계열코드 밤생기를 구성하였다.

DDFS에서  $f_{\text{ck}}$  를  $2^{20} = 1.048576 MHz$ , 그리고 어큐뮬레이터출력(N)을 20비트로 하여 주파수 해상도를 1 Hz로 유지하였다.

N이 20비트이므로 복소 지수항 샘플값을 얻기 위한 어큐율레이터의 누적값Y는 다음으로 표시된다.

$$Y = \alpha_0 2^6 + \alpha_1 2^1 + \alpha_2 2^2 + \cdots + \alpha_{19} 2^{19}$$

이를 2개의 Table로 분리하기 위해 binary 형태로 다시 쓰면,

$$Y = 2^{9} \alpha_{0} + 2^{1} \alpha_{1} + \dots + 2^{9} \alpha_{9} + 2^{10} (\alpha_{10} + 2 \alpha_{11} + \dots + 2^{9} \alpha_{19}) = q + 2^{10} r$$

(3-3)

여기서

$$q = 2^{\circ} \alpha_0 + 2^{1} \alpha_1 + \dots + 2^{\circ} \alpha_{\bullet}$$

$r = \alpha_{10} + 2 \alpha_{11} + \dots + 2^{\circ} \alpha_{19}$

이다.

따라서 Y는 다음과 같이 분리된다.

$$e^{J(2\pi/N)\Upsilon} = e^{J(2\pi/2^{20})\cdot(Q+2^{10}\Gamma)}$$

$$= |e^{J(2\pi/2^{20})\cdot q}| \cdot |e^{J(2\pi/2^{10})\Gamma}| \qquad (3-4)$$

이제 샘플치의 연산에는 e<sup>/2n/2mq</sup>와 e<sup>/4n/2mr</sup>인 2개의 Table과 한 번의 복소 중산이 필요하다. 인덱스 r은 어큐뮬레이터의 상의 10비트로 구성되고 q는 하위 10비트로 구성된다.

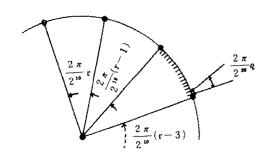

어는 단위 원 상의 (2π/N)Υ개 중의 한 값을 계 산한다는 면에서 볼 때, 그림 3-2와 같이 r 값은 단위원을 210 개로 분할한 값에 해당하며 q 값은 r 에 더해질 210 개의 사이값에 해당한다. 위상각 보정 즉 q 값의 가산은 복소 승산으로 이루어지며, 두 개의 Table을 이용하여 계산할 때 다음과 같은 삼 각함수 식으로 처리되도록 하였다.

그림3-2 위상각 보정 Phase angle compensation.

$\sin(q+r) = \sin q \cos r + \cos q \sin r$  (3-5)

DDFS 구성에서는 시스템을 간단히 하기 위해 q 툴 충분히 작은 값으로 고려하였다. 즉.

축,  $\cos q \neq 1$   $\sin q \neq 0$ 로 근사시킴으로써  $\sin r$ 에 해당하는 단일 Table을 사용하였고, 출력 정현 과가 0와  $\pi$  그리고  $\pi/2$ 와  $3\pi/2$ 에서 각각 대칭인 성질을 이용하여 Table에 기록할 데이터 수를 1/4로 더욱 감소시켜  $2^{n}=256$ 개의 데이터만으로 시스템을 구성하였다.

구성한 시스템의 최대 출력 주파수 갯수F는 N=2<sup>10</sup> 개이므로 식(2~5) 애 따라 2<sup>10</sup>=524,288 개까지 얻을 수 있으나 샘플링 고조파와 LPF특성을 고려하여 출력주파수 대역을 256.143KHz로 하였다. 또한 필요한 메모리 총수S는 식(2-6) 에서 (2.2<sup>10</sup>)<sup>1/2</sup>=1024개 어지만 보수회로를 사용하여 시스템을 구성한 점을 고려하면 설제 단위원 상의 데이터수는 1,024개로 식(2-6) 의 결과와 일치한다.

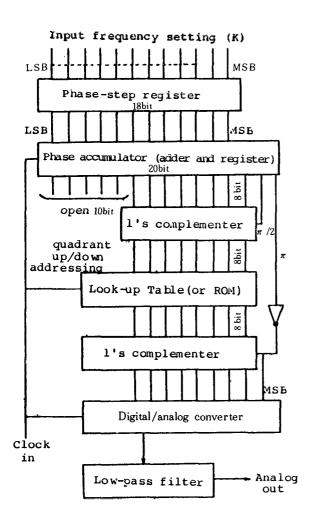

한편 SNR은 위상 양자화 비트를 10비트, 전폭양 자화 비트를 8비트로 하여 양자화 오차에 따른 SNR이 약~49dB가 되도록 하였다. 그림3-3에는 본 논문에서 실현한 DDFS의 구성도를 나타내었다. 위상 어큐뮬레이터는 74LS83 전 가산기와 74LS 74 D-플립플롭으로 구성하였고 출력의 최상위 두

위상 어큐뮬레이터는 74L583 전 가산기와 74LS

74 D-플립플톱으로 구성하였고 출력의 최상위 두 비트를 보수 회로의 제어 비트로 이용하였다. Table 앞단의 1의 보수 화로는 74LS86 EX-OR 제이 트로 구성하여 2 상한과 4 상한에서 위상 어큐뮬레이터 출력이 반진되도록 하였고 table에는 처리 시간이 350nS 인 27320 EPROM을 이용하여  $\pi/2$ 까지의 정현과 진목치를 8 비트로 기록하였다. Table을 력은 다시 1의 보수 회로를 거쳐 주기를 보상한다. D/A 변환기 앞단에는 74LS74 D-플립플룹으로 구성된 버퍼 레지스터를 두어 D/A변환기에서 발생하는 글리키 잡음을 출이도록 하였다.

D/A변환기는 세틀링 타임이 500mS인 DAC1020-LCN을 사용하였고 그 전류원 출력을 OP AmpLF 351을 이용하여 전압원 출력으로 변환하였다. 최종 단의 LPF는 차단 특성이 60dB/Oct가 되도록 10차 Butterworth LC LPF를 구성하였다.

한편 호광특성을 검토하기 위한 PN코드는 그림 3 - 4과 같이 4단의 레지스터와 modulo - 2 가산기로 구성되는 코드길이 15인 최장 계열 코드를 이용하였다.

# 4. 실험 및 고찰4 - 1、DDFS 및 호핑 육성

DDFS와 PN코드 발생기는 각자 그림 3-3및 그림 3-4에 따라 제작하였다.

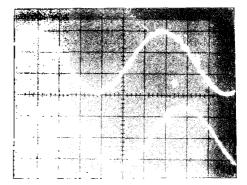

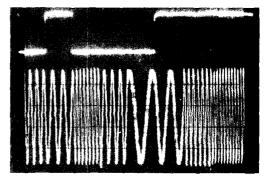

그림 4 ~ 2에는 위상값의 선형적인 누적으로 나타난 0°에서 90°까지의 위상 어큐뮬레이터 출력과 두번째 MSB 과형을 나타내었고 그림4 ~ 3는 이때의 table 출력으로 얻어지는 90°까지의 정현화를 나타낸 것이다.

그림 4 - 4에는 두번째 MSB를 이용하여 90° 반전시킨 180°까지의 출력 파형을 나타내었고 그림 4 - 4에는 두 MSB를 보수 회로에 연결함으로써 정현과가 얻어짐을 보였다.

그림 4-5의 (상)에 보인 D/A변환기 출력 화형에는 굴리치 잡음이 포함되어 있으나 필터를 거친 화형(하)에서는 글리치 잡음과 불연속 성분이 정형되어 깨끗한 정현과가 얻어진다.

그림 3 - 3 DDFS의 구성도 Block diagram of DDFS.

그림 3-4 4단 최장 제열 코드 발생기의 구성도 Block Diagram of 4 stage Maximal Code Generator.

그림 4-1 성능 개선을 위한 시스템 구성도 Block Diagram of advanced system.

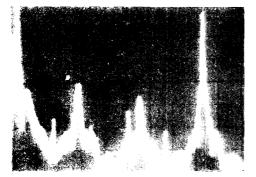

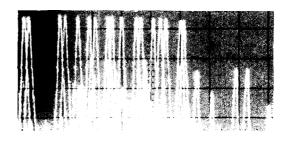

그림 4-6은 발생 주파수가 10KHz일 때의 D/A 변환기 출력 스펙트럼으로 양자화 오차에 따른 고조과, 성분 이외에도 기타 글리치 잡음등이 나타

나고 있다. 이 때의 SNR은 약 50dB 로 설계값보다 우수하지만 발생 주파수가 82KHz일 때안 그림 4 ~ 7의 SNR은 약 30dB 정도로 설계치보다 약 18d B 정도 낮은 값으로, 이는 출력 주파수가 높을수록 귤리치 잡음이 크게 발생하고 그림 4 ~ 8에 나타낸 것처럼 MSB파형의 펄스폭이 수기적으로 변화됨으로써 D/A 변환기 출력 파형에도 주기적인 왜꼭이 나타나기 때문인 것으로 관측되었다.

그림 4-2 위상어큐뮬레이터의 출력파형

Output woveform of phase accumulator(below)

and 2 nd MSB(above)

Vert.: 3 V/Div., Hor.: 1 mS/Div,

그림 4-3 2ndMSB의 파형

Output waveform of 2nd MSB(above)

and Table(below)

Vert.: 3 V/Div., Hor.: 1.5 mS/Div.

그림4-4 ist MSB의 화형 Output waveform of ist MSB(above) and Table(blow)

Vert, : 1 V/Div., Hor, : 1 mS/Div.

그림 4-5 2nd MSB와 DAC의 출력파형 Output woveform of 2nd MSB and D/A converter. Vert.: 1 V/Div., Hor.: 1 mS/Div.

그림 4-6 DAC와 필터출력 과형

Output waveform of D/A converter(above)

and filter(below)

Vert.: 1 V/Div., Hor.: 0.5mS/Div.

그림 4 - 7 10KHz때의 스펙트럼분포 Output spectrum distribution when = 10KHz Hor.: 5KHz/Div., Vert.: 10dB/Div.

그림 4-7 82KHz때의스펙트럼 분포

Output spectrum distribution

when f = 82KHz

Hor.: 10KHz/Div., Ver.: 10dB/Div.

고함 4-8 DAC와 2nd MSB의 예곡상태 D/A converter and 2nd MSB waveform when periodic distorion occurs Hor.: 0.2mS/Div., Vert.: 1 V/Div.

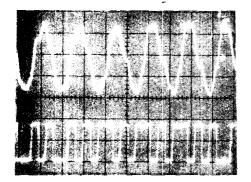

그림 4-9 PN코드와 호핑파형

PN code(above) and hopping

waveform.

Hor. 10.5mS/Div., Vert. 13 V/Div.

그림 4-10 DDFS의 호핑스펙트럼 Hopping spectrum of DDFS Hor.: 50KHz/Div., Vert.: 10dB/Div.

그림 4 - 9는 PN코드에 따른 호핑 파형으로 발생되는 호핑 주파수의 위상이 연속 위상을 이루며, 호핑시에 소요되는 천이 시간도 클릭 주파수의 입상 시간(rising time)으로 나타나고 있다. 실험 모델의 클릭 주파수가 1.048576MHz 임을 감안할 때 nS정도이고 따라서 DDFS가 FFH 시스템에 매우접합함을 알수 있다. 그러나 그림 4 - 10의 호핑스펙트럼에는 그림 4 - 8 파 같은 이유로 SNR 면에서 설계치보다 약 20dB 정도 낮은 값으로나타났다. 이러한 성능 열화를 극복하기 위해서는 근본적으로 글리치 성분을 억제하고 양자화 비트를 증가시키는 방법이 필요하다.

#### 4 - 2. 성능 개선 방향

본 논문에서 제시하는 성능 개선 방법은 위상 양자화 비트를 증가시키며 메모리 수를 감소시키기위해 Table을 분리시키고, 또한 진폭 양자화를 증가시키기 위해 D/A 변환기를 다단화하고 Table의 어드레스 공유 기술을 이용함으로써 진폭 데이터 비트를 증가시킨다.

즉 정현파 출력을 얻기위해 석(3-5)에서 cosr ≒ 1 모 근사하여

$$\sin(q+r) = \sin q + \cos q \cdot \sin r \qquad (4-1)$$

Table 1에는 sing 값을 기록하고 Table 2에는 cos q·sin r 를 기록한 뒤, Table 1,2의 출력을 가산하여 샘플치를 계산한다. 이렇게 하면 기존의 Table분리방식에서의 승산 부분을 제거할수 있어 구성이 간단해지고, 위상 양자화 면에서는 단 일 Table 방식보다 위상 양자화가 2배로 증가된다. 진폭 양자화 비트를 증가시키기 위해서는 Table 의 출력 데이터 비트와 D/A 변환기의 비트를 동시에 중가시켜야 한다. 그런데 비트수가 큰 D/A 변환기 일수록 세틀링 타임이 늦고 이것이 늦을수록 DDF S의 발생 주파수 대역이 줄어든다. 따라서 세틀릿 타임을 그대로 유지하면서 처리 비트만 증가시킬수 있는 방법이 필요하다. 이를 위하여 Table의 어드 레스를 공유함으로써 진폭 데이터를 배가시키고 확 장된 데이터 비트를 2개의 D/A 변환기에 분리 인 가한다. 이 때 하위 비트측의 D/A 변환기 출력 swing이 상위 비트축 D/A 변환기의 양자화 레벨에 해당하도록 출력을 감소시켜 summing 하면 처리 비 트가 증가하더라도 세틀링 타임은 그대로 유지된다. 그림 4 - 1에는 이상에서 논의한 방법으로 시스템 율 구성할 경우의 불록 다이어 그램을 나타내었다.

이와같은 방법을 이용하면 양자화에 따른 SNR을 개선할 수 있으며 8비트 D/A 변환기 3개를 다단 화 할 경우 현재의 소자 기술 수준으로도 140dB 정 도의 높은 SNR 특성을 얻을 수 있다.

### Ⅴ. 결 론

본 연구에서는 고속 주파수 호핑 시스템용 직접 디지를 주파수 합성기를 발생 범위가 262, 143KHz, 주파수 해상도가 IHz, 그리고 양자화 오차에 따른 SNR이 40dB가 되도록 설계계작하고 그 특성을 분 석하였다.

시험 결과, DDFS가 고속주파수 호핑시스템에 적합함을 확인하였고 고속 주파수 호핑에는 주파수 합성기의 클럭 주파수가 PN코드 발생기 클럭 주파수보다 빨라야 하며 발생 주파수 대역에 크게 영향을 주는 요소는 ROM의 처리속도 임을 알 수 있었다. 이를 개선하기 위해서는 반도체 제조기술 향상이 바탕이 되어야하나 현용 소자로도 약200MHz 대의 호핑 대역으로 실현 가능하며 SNR은 -20dB~-40dB의 스펙트럼 특성을 얻었으나 제시된 개선 방법을 적용시키면 보다 높은 SNR을 얻을 수 있을 것으로 본다.

이 연구는 1987년도 문교부 학술 연구조성비 지원금에 의하여 이루어 졌읍니다.

### 참 고 문 헌

- Draft, "Consideration of Interference from Spread-Spectrum systems to Conventional Communication Systems," CCIR 14th Plenary Assembly, Dod. 1/1008-E Report 1/20721, March 1978.

- D. Verhulst, M. Marley, J. Szpirglas. "Slow Frequency Hopping Multiple Access for Digital Cellular Radio Telephone," IEEE Journal on Selected Areas in Commun., vol.SAC-2, no.4, pp.563-574, July 1984.

- Simon, Omura, Scholtz, Levitt, "Soread Spectrum Communication: volumel." Computer Science Press, Inc., pp.167-247, 1985.

- R.E. Ziemer, R.L. Peterson, "Digital Communications and spread Spectrum Systems," New York:

M Millian Publishing Co., pp.327-361, 1985.

- 5. J. Tiemey, C.M. Radar, B. God. "A Digital Fre-

- quency Synthesizer," IEEE Trans. Audio Electro-acoust. AU-19, pp.43-57, March 1971.

- J. Gorski-Popiel, "Frequency Synthesis: Techniques and Applications." IEEE Press, pp.96-119, 1975.

- 7. L. Stein and Jones, "Modern Communication Principles," McGraw-Hill, pp.207-209, 1967.

▲김 원 후 6권 1호 참조