# A Two Dimensional Analysis of the Low Level Currents in Buried Channel MOS Trasistors (Buried Channel MOS Transistor에서의 미소 전류

에 대한 2차원적 해석)

金 忠 基\*, 慶 宗 旻\*\*, (Kim, Choong ki and Kyung, Chong Min)

要 約

Buried Channel MOS 트랜지스터에서의 미소전류(Subthreshold Current)를 2차원 평면에서 Poisson 방정식과 연속 방정식을 Interactive 하게 적용함으로써 계산하였다. 계산 결과를 실험 결과와 비교하 였고 미소 전류 영역에서는 두 결과가 비교적 잘 일치하고 있음을 보였다.

#### Abstract

Low level currents in a buried channel MOS transistor have been computed numerically by solving the Poisson's equation and continuity equation in a two-dimensional space. The results are compared with experimental measurements in terms of the drain current. Reasonable agreement has been found in the subthreshold region where the drain current depends on the gate-to-source voltage exponentially.

## Introduction

With the advancement of the buried channel charge coupled device (CCD)1,2,3) technology, interests on the buried channel MOS transistor or Junction and Insulated Gate Field-Effect Transistor (IIGFET)4) have grown considerably recently. This is mostly due to the fact that a buried channel MOS transistor is a natural MOS transistor to be fabricated on the same chip with a buried channel CCD using an identical processing sequence. Besides the processing compatibility, the buried channel MOS transistor has higher transconductance, better linearity, and lower noise when compared with a conventional surface channel MOS transistor40 The low noise property of the buried channel MOS utilized in the charge transistor is often

detection scheme of a CCD such as floating gate amplifier (FGA)<sup>5)</sup>, and distributed floating gate amplifier (DFGA)<sup>6)</sup>. Theoretical analysis of DFGA noise<sup>7)</sup> shows that the signal-to-noise ratio of the amplifier has the maximum value when the buried channel MOS transistor is biased near the boundary of the subthreshold region.

Although the buried channel MOS transistor is widely used in practice for the charge detection scheme in a buried channel CCD, theoretical analysis of the transistor in and near the subthreshold region has not been carried out in sufficient detail. Barron<sup>8)</sup> has given analytic expressions of the subthreshold current for the conventional MOS transistors. This model, however, is not adequate for a burried channel MOS transistor where the drain current is confined in a region which is always kept away from the silicon/silicon dioxide interface.

Masuhara and Etoh<sup>9)</sup> calculated the surface electron density in the subthreshold region of implanted MOS transistors, but could not attain

接受日字:1978年 8月 16日

<sup>\*</sup>正會員,韓國科學院 電氣 및 電子工學科

<sup>\*\*</sup>準會員, 韓國科學院 電氣 및 電子工學科 (Dept. of Electrical Science, KAIS)

drain current characteristics therefrom. This is due to the fact that, with some drain-to-source bias voltage applied, there exists a great asymmetry in the electron concentration and potential distribution along the channel, which necessitates the use of a two-dimensional analysis.

This paper reports the results of a two-dimensional calculation of the drain current of a buried channel MOS transistor. Both the subthreshold region and the normal operating region are treated in a unified manner without resorting to curve fitting methods. The numerical method developed for JFET<sup>10)</sup> has been used with appropriate modifications.

## Device Model and Results

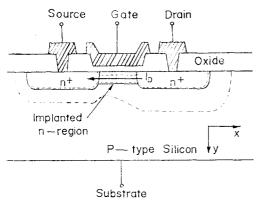

The cross-sectional view of the buried-channel MOS transistor is shown in Fig.1. The n-region underneath the gate oxide is formed by ion-implantation resulting in a Gaussian impurity profile. In the normal operating bias range, there

Fig.1. Cross-sectional view of a buried channel MOS transistor.

exists depletion regions both at the silicon/silicon-dioxide interface and n/p junction formed by the implanted region and the substrate. The drain current, therefore, is confined within the implanted n-region and is alway kept away from the interface. Since the drain current is flowing inside the bulk region, the bulk mobility determines the current rather than the surface mobility, thereby giving higher transconductance. The 1/f noise of conventional MOS transistor is also

suppressed because the electrons for the drain current is not interacting with the surface states. In the subthreshold region, the number of electrons in the conductive channel between the source and drain decreases, and the drain current is determined by the electro static potential and electron distribution near the source region. (10)

In general, the drain current is obtained by

$$I_D = Z \int q \mu_n \ n \frac{\partial \varphi_n}{\partial x} \ dy$$

.....Equ.1

where Z is the channel width perpendicular to the figure,  $\mu_{\pi}$  is the bulk mobility and  $\varphi_{\pi}$  is the quasi-Fermi level for electrons. Since the electron density, n, is related to the electro-static potential,  $\phi$ , as

$$x = n_i \exp\left[\frac{-q(\phi - \varphi_n)}{kT}\right]$$

.....Equ.2

one can compute the drain current from  $\psi(x,y)$  and  $\varphi_n(x,y)$ . The electrostatic potential and the quasi-Fermi level for electrons are obtained by solving the Poisson's equation and the continuity equation simultaneously. These are

$$\Gamma^{2}\phi = \frac{-q}{\epsilon_{s}\epsilon_{0}} (N_{D} - N_{A} - n + p) \cdots \text{Equ. 3}$$

$$\Gamma \cdot J_{n} = -\Gamma \cdot (q\mu_{n} \cdot n \cdot \Gamma \phi_{n}) = 0 \text{ } \cdots \text{Equ. 4}$$

Note that the net rate of recombination has been taken to be zero in Equ.4. This is a reasonable approximation for the device since most of the drain current is due to the majority carriers, i.e., electrons inside the channel.

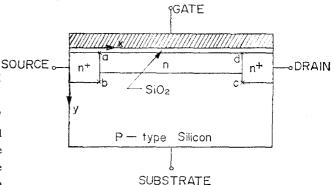

Fig.2. Device model for the two-dimensional numerical calcultion.

Both Equ. 3 and 4 have been solved for a simplified device model shown in Fig.2, by using

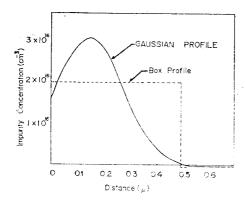

Fig.3. Gaussian impurity profile resulting from ion-implantation and box-profile approximation.

numerical technique reported in Ref. 10) with appropriate modifications. The doping profile of the implanted n-layer has been approximated by a box-profile as shown in Fig.3. The impurity concentration and the junction depth of the box-pro file have been chosen in such a way that the channel location remains the same as for the Gaussian profile. This approximation results in a slight increase (about 10%) for the total number of impurities in the implanted layer. However, as will be shown later, the more serious problem in this approximation is that it

Fig.4. Distribution of electron concentration in side the rectangular region a-b-c-d of Fig.2. The electron concentration is normalized by the doping level of the n-region (2×10<sup>16</sup>cm<sup>-3</sup>).

$V_{G}$ =5 Volts,  $V_{D}$ =14Volts,  $V_{SUB}$ =0 Volt and  $V_{S}$ =9 Volts for (a),  $V_{S}$ =8 Volts for (b)

Flat band voltage is taken to be zero. oxide thickness = 0.12 micron channel length = 5 microns

has resulted about five-to-ten times increase of the impurity concentration at the channel location, i.e., about 0.4 m deep from under the gate oxide. The results of two-dimensional computation is shown in Fig.4 for the subthreshold region and normal operating region in terms of electron concentration. The formation of the conductive channel inside the bulk nregion and channel pinch-off near the drain is clearly observed in the normal operating region. In the subthreshold region, most of the implanted region is depleted except very near the source region. In this case, the drain current is believed to be due to the electrons that are injected from the source  $n^+$  region to the channel region.

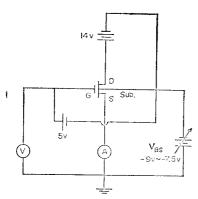

Fig.5. Drain current vs. gate-to-source voltage  $V_S = 7.5 \sim 9$ Volts,  $V_D = 14$  Volts,  $V_G = 5$  Volts with substrate grounded.

The results of the numerical computation have been compared with the experimental data in terms of the drain current in Fig.5. The experiment has been carried out on the test MOS transistor in Fairchild CCD 110 chip using three independent voltage sources for the bias of the drain, the gate, and the substrate terminals, while grounding the source. The drain current is measured with Keithley 610 C Electrometer while varying the source-to-substrate voltage and keeping the other bias voltages constant. The circuit diagram of the experimental set-up is shown in Fig.6.

The experimental curve shown in Fig.5 has been matched with the theoretical one by shifting the former horizontally by 1.68 Volts to take

Fig.6. Measurement Circuit.

A: Keithley 610C Electrometer

V: Keithly 616 Digital Electrometer

care of the non-zero flat-band voltage. The agreement between the numerical result and the experimental measurement is reasonable in the subthreshold region where the drain current depends exponentially on the gate-to-source voltage. This indicates the validity of the numerical method employed in the subthreshold region. As can be noticed in Fig.5, however, comparatively large discrepancy exists between the two curves in high and medium current levels. This discrepancy is believed to be partly due to the series resistances of the source and the drain region and partly due to the box-profile approximation which resulted in about five-to-ten times increase of the impurity concentration at the channel location, thereby increasing the channel conductance for the medium and high current levels.

### Acknowledgement

The authors wish to thank Fairchild R & D Laboratory for providing the sample device. They also would like to express their gratitude to the reviewer who pointed out the misfit between experimental and computational results and, at the same time, suggested the reason.

#### References

W.S. Boyle and G.E. Smith, "Charge coupled semiconductor devices," BSTJ, Briefs, vol. 49, No.4, p.587, April 1970.

- R.H. Walden, R.H. Krambeck, R.J. Strain, J. Mckenna, N.L. Schryer, and G.E. Smith, "The buried channel charge coupled devices," BSTJ, vol. 51, 1972.

- C.K. Kim, J.M. Early and G.F. Amelio, "Buried-channel charge-coupled devices," NEREM, Boston, Mass. Record of Tech papers, part I, p. 161~164, 1972.

- W.Sansen, P.Six, C.Verbraeken, R. Van Overstraeten, "Model and linear applications of the "JIGFET (Junction and Insulated Gate Field-Effect Transistor)," Technical Digest of International Electron Device-Meeting, p.541~p.545, Washington D.C. December 1974.

- D.D. Wen, "Design and operation of a floating gate amplifier," IEEE Journal of Solid-State Circuits, vol. SC-9, No. 6, November 1974.

- D.D. Wen, J.M. Early, C.K. Kim and G.F. Amelio, "A distributed floating gate ampli, fier in charge coupled devices," 1975 International Solid-State Circuit Conference, Philadelphia, PA., February, 1975.

- G.F. Amelio, "The impact of large CCD image sensing area arrays," International Conference on Technolonlogy and Applications of Charge Coupled Devices, Edingurgh Scotland, September, 1974.

- M.B. Barron, "Low level currents in insulated gate field effet transistors," Solid state Electronics, vol. 15, p.293, 1972.

- T. Masuhara and J.Etoh, "Low-level cur rents in ion-implanted MOSFET," IEEE Trans. on Elect. Devices, vol. ED-21, No. 12, December 1974.

- 10. C.K. Kim and E.S. Yang, "An analysis of current saturation mechanism of junction field-effect transistors," IEEE Trans. on. Elect. Devices, vol. ED-17. February 1970.