# FPGA기반 선박 무선제어 시스템 구현

#### † 윤영

↑ 한국해양대학교 전자전기정보공학부 전파융합공학전공 교수

## A Realization of Vessel Wireless Control System Employing FPGA

#### \* Young Yun

† Division of Electronics and Electrical Information Engineering, Korea Maritime and Ocean University, 727 Taejong-ro, Yeongdo-gu, Busan 49112, Korea

요 약: 최근 미국에서는 민간 우주개발업체인 스페이스 x가 스타링크 사업을 통해 2031년까지 저궤도 위성 42000개를 띄울 계획을 발표하였으며, 현재까지는 900여개의 위성을 발사하였다. 구체적으로는 Ku 대역과 ka 대역을 갖는 위성을 운용할 계획이며 광대역 신호의 전송을 위해 V 대역을 갖는 7518개 위성을 고도 340 km에 발사할 계획이다. 따라서, 원양에서도 무선통신이 가능하게 되며, 저궤도 위성을 이용한 다양한 솔루션이 제공될 계획이다. 본 연구에서는 디지털 통신 시스템과 모터 제어 시스템을 FPGA 칩 내부에 구현하여 이를 선박무선 통신 시스템에 적용하고자 한다.

핵심용어: FPGA (Field Programmable Gate Array), 선박, 무선제어 시스템

Abstract: Recently, SpaceX, private enterprise dealing in space development company, has reported a plan for launching of 42,000 low earth orbit satellites until 2031 through Starlink Business, and launched 900 satellites until now. Concretely, it plans to operate Ku/Ka band satellite, and launch 7,518 of V band satellites for broadband communication. Therefore, we can utilize wireless communication in an ocean, and various solutions through the low earth orbit satellites. This paper deals in a realization of wireless control system employing FPGA (Field Programmable Gate Array) for vessel applications.

Key words: FPGA (Field Programmable Gate Array), vessel, wireless control system

#### 1. 서 론

최근 미국의 민간 우주개발업체인 스페이스 x는 스타링크 사업을 통해 2031년까지 저궤도 위성 42000개를 발사할 예정 이며 현재까지는 900여개의 위성을 발사하였다. 향후에는 저 궤도 위성을 통해 상당부분의 인터넷 음영지역이 해소될 것으 로 기대되며, 원양에서의 선박 상에서도 인테넷 사용 및 동영 상 전송등의 무선통신이 가능할 것이라 기대된다 [1, 2].

차세대 선박에는 저궤도 위성 무선통신을 통한 인공지능기 반 자율주행기능이 추가될 것으로 기대되며, 본 연구에서는 소형 수중드론에 탑재할 FPGA기반 인공지능 영상인식 시스 템의 구현에 대해 발표하고자 하며, 그 중에서 제어 시스템에 대해 구체적으로 발표하고자 한다.

### 2. 통신시스템 시뮬레이션

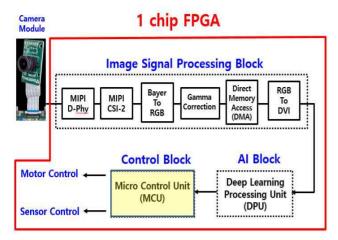

그림 1은 FPGA를 이용한 AI기반 수중드론 영상인식 시스템을 보여준다. 그림에서 보는 바와 같이 카메라 모듈과

FPGA를 연결하기 위해 물리계층 (physical layer)로는 D-Phy를 이용하였으며, 프로토콜로는 MIPI CSI-2[2]를 이용하였다. 카메라 모듈내부에 있는 이미지 센서는 그림 2와 같이 Bayer 패턴이 입력되며, Bayer 패턴을 RGB 영상으로 변경하기 위한 블록이 MIPI CSI 블록에 연결되어 있다. 그리고, 감마보정 (Gamma Correction) 블록과 RGB 영상신호를 DVI로 변경하는 블록과, 영상처리 블록이 frame buffer에 저장된 픽셀데이터에 직접 억세스 가능하도록 하는 DMA (Direct Memory Access) 블록도 내장하였다. DPU (Deep Learning Processing Unit)은 카메라로부터 받은 영상신호를 통해 장애물 회피등의 동작을 수행하도록 제어회로에 신호를 전송하며, 제어회로는 모터등을 구동하여 DPU가 명령한 동작을 수행한다.

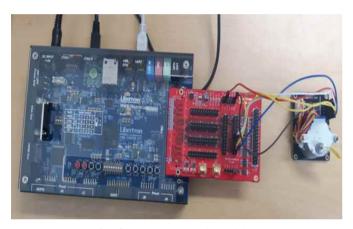

그림 2는 모터제어부에 대한 모듈 사진을 보여준다. 모터 제어부는 FPGA 내부에서 디지털 회로로 구현되어 있다.

Fig. 1 FPGA-based image recognition system of underwater drone.

Fig. 2 Motor control module.

## 3. 결 론

본 연구에서는 소형 수중드론에 탑재할 FPGA기반 인공지 능 영상인식 시스템을 구현하였으며, 이에 대해 발표하고자한다.

# 참 고 문 헌

- [1] 윤영(2021), "차세대 선박통신을 위한 무선통신 시스템 개발", 2021년도 한국해양과학기술협의회 공동학술대회 논문지, 나T2-Z10-1.

- [2] 윤영(2021), "저궤도 해상 위성통신을 위한 FPGA Chip 개발", 2021년도 한국해양과학기술협의회 공동학술대회 논문지, 나T2-Z10-2.