# 펄스 전기장 방식을 위한 전류원 기반의 고전압 펄스 발생 회로

오현준, 강윤수, 황훈하, 노정욱 국민대학교 전자공학과

# High voltage pulse circuit based on current source for Pulsed Electric Field method

Hyun Jun OH, Yoonsu kang, Hoonha Hwang, Chung Wook Roh Dept, of Electronics Engineering, Kookmin Univ.

#### **ABSTRACT**

식품을 보다 신선하고 오래 보관하기 위하여 처리 및 보존에 관한 여러 방법들이 연구되고 있다. 특히 열에 민감한 유제품 또는 액체 식품들에 대하여 열을 가하지 않는 비열처리 방식의 기술들이 연구되고 있다. 그 중 식품 내 미생물의 활성화와 고유한 속성의 변화를 최소화하는 방법으로 Pulsed Electric Field 방식에 대한 연구가 활발히 진행되고 있다. 하지만 해당 방식은 기존의 열처리 방식에 비해 경제적인 면에서 단점을 가지고 있다. 이에 본 논문에서는 기존 Pulsed Electric Filed 방식의 효율을 높이고 비용을 저감할 수 있는 회로를 제안한다. 전압제어 방식의 DC/DC Power stage 부를 전류제어 방식으로 바꾸어 기존 회로의 Charging resistor를 사용하지 않음으로써 전력손실을 줄이고 비용 및 전기요금을 줄이고자 하였다. 본 논문에서는 시뮬레이션을 통해 제안회로를 검증하였다.

#### 1. 서론

최근 음식물의 처리 및 보존을 위하여 cold plasma, high pressure processing, irradiation, microwave heating, ohmic heating, pulsed high intensity light, pulsed x-rays, oscillating magnetic field, pulsed electric field 등의 여러 비열처리 방식 의 기술들이 연구되고 있다. 여러 기술들 중 Pulsed electric field 방식은 고전압의 전압원과 충전 저항을 포함한 고압의 스 위칭 회로로 구성되어 있는 회로를 이용해 고압 펄스를 발생시 키는 방식으로써, 열에 민감한 쥬스, 우유, 유제품 등의 액체 식품의 처리를 위해 특히 전도유망한 기술이다. 이는 미생물의 활성화를 최소한으로 제한하면서 동시에 영양성분과 맛, 향 등 식품 본래의 특성을 최대로 유지 시켜줄 수 있을 뿐더러 기존 의 열처리 방식과 비교하여 환경 오염이나 독성의 발생이 없고 더 적은 에너지를 이용하여 큰 효율을 낼 수 있다는 점에서 각 광받는 기술이다. 다만 기존의 열처리 방식과 비교하여 단점이 있다면 pulsed electric filed 방식을 위한 장비나 작업 환경 등 과 관련하여 초기 투자사항이나 비용 측면에서 비싸다는 점이 다. 이러한 비용과 효율 측면의 단점을 보완하기 위한 연구가 최근 다수 진행되고 있다.[1]

이에 본 논문에서는 기존의 Pulsed electric field 방식의 고 전압 펄스 발생을 위한 기존 회로의 효율을 상승시키고 소비전 력 및 비용을 감소시키기 위한 회로를 제안한다. 본 논문에서 는 시뮬레이션을 통하여 제안한 회로를 검증한다.

# 2. Pulsed Electric Filed 방식을 위한 고전압 펄스 발생 회로

#### 2.1 펄스 전기장 방식을 통한 식품 처리의 원리

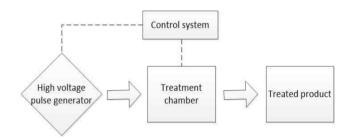

그림 1 펄스 전기장 방식을 통한 식품 처리 과정

고전압 펄스 발생기로부터 마이크로초에서 밀리미터초에 해당하는 짧은 지속시간과 10~80kV/cm의 강도를 갖는 고압 펄스를 발생시켜 Treatment chamber 내부에 있는 두 개의 전국에 인가한다. 이때, 처리되고자 하는 식품은 양 전극 사이에 위치한다. 고압 펄스가 인가된 두 전극은 전기장을 생성하고 이전기장은 식품의 미생물을 비활성화시키는 역할을 하는데 이는식품 내부의 전기전도성을 띄는 여러 이온들의 존재로 인하여식품으로의 전기 전도가 가능하기 때문이다. 이렇게 처리된 식품은 냉장 상태로 보관된다. 펄스 전기장 방식은 이와 같은 원리로 쥬스, 우유, 요거트 등의 액성 식품에 저온 살균의 형태로적용된다.

## 2.2 펄스 전기장 방식의 기존 펄스 발생 회로 2.2.1 기존 펄스 발생 회로의 구성

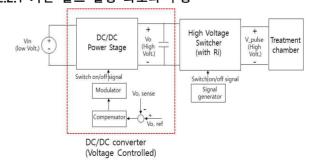

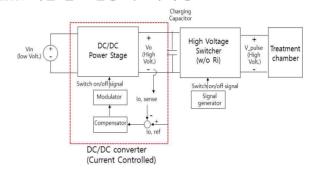

그림 2 기존 펄스 발생 회로의 구성 불록도

그림 2에 기존의 펄스 발생 회로의 구성을 블록도로 나타내었다. 크게는 DC/DC converter와 High Voltage Switcher로 구성되어 있어 이를 통해 발생된 고전압 펄스가 Treatment chamber에 인가되는 구성이다. DC/DC 컨버터는 기준전압에 출력전압이 추종하도록 제어하는 방식으로(voltage controlled), Boost, Buck/Boost, Flyback, Forward, Hlaf-Bridge, Full-Bridge, 공진형 컨버터 등의 기존 전력 회로 topology를 활용한 DC/DC Power stage와 통상 PI, PID 제어 방식을 사용하는 Compensator(Hysteresis, Sliding Mode Control 등의 고급 제어 방식 사용 가능), 통상 PWM(Pulse Width Modulation), 공진형 컨버터의 경우 PFM(Pulse Frequency Modulation) 방식을 사용하는 Modulator로 구성되어 있다.

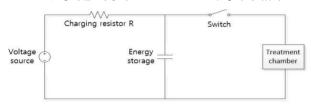

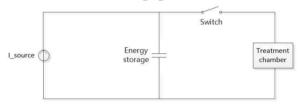

그림 3 기존 High voltage switcher의 등가회로

그림 3에 High voltage switcher 부를 등가회로로 나타내었다. High voltage switcher 부는 DC/DC converter를 통해 만들어진 전압원이 충전 전류를 제한하는 역할을 하는 충전 저항을 통해 캐패시터에 충전되고 스위치에 의해 Treatment chamber로 방전하는 시스템으로 구성되어 있다.

#### 2.2.2 기존 펄스 발생 회로의 문제점(simulation)

그림 3의 High voltage switcher의 등가회로에서 Charging resistor R을 통해 전력손실이 발생할 수 밖에 없음을 유추할 수 있다.

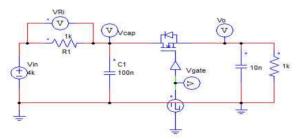

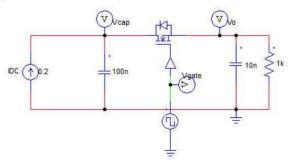

그림 4 기존 HV switcher의 시뮬레이션 회로도

DC/DC converter를 통해 발생된 전압원을 4kV로 설정하였을 때, Charging resistor R에서의 소모전력을 시뮬레이션을 통해 확인하였다.

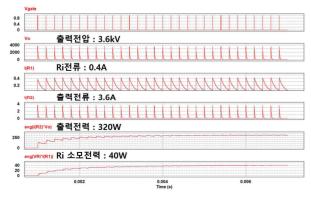

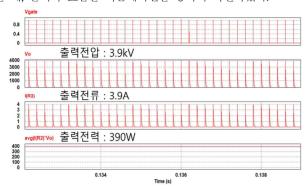

그림 5 기존 HV switcher의 시뮬레이션 결과 파형

일례로 4kV의 입력과, 320W의 부하 펄스 발생시, Charging resistor Ri에서의 소모전력은 40W, 입력전력은 360W로 관측되었다. 회로의 모든 조건이 이상적이라는 가정하에 기존 방식의 고전압 펄스 발생 회로는 최대 효율이 88%이고, Charging resistor Ri에서의 소모 전력이 40W로 큰 전력손실과 이로 인해 고사양의 resistor를 선정해야 한다는 문제점이 있다. 뿐만아니라 부하 전력에 비해 입력 전력이 크기 때문에 전기세가증가한다는 문제점도 발생한다.

## 2.3 펄스 전기장 방식의 제안 펄스 발생 회로 2.3.1 제안 펄스 발생 회로의 구성

그림 5 제안 펄스 발생 회로의 구성 블록도

그림 5에 제안된 펄스 발생 회로의 구성 블록도를 나타내었다. 제안된 회로의 DC/DC converter는 기준전류에 출력전류가 추종하도록 제어하는 방식으로(Current controlled) 기존의 출력 캐패시터는 switcher의 charging 캐패시터의 역할을 한다.

그림 6 제안 High voltage switcher의 등가회로

그림 6에 High voltage switcher 부의 등가회로를 나타내었다. High voltage switcher 부는 기존 회로와 비교하여 전압원을 전류원으로의 변화를 통해 전력손실의 큰 원인이 되는 Charging resistor를 사용하지 않을 수 있다.

## 2.3.2 제안 펄스 발생 회로의 개선사항(simulation)

기존 회로와 비교하여 전력손실의 큰 원인이 된 Charging resistor가 사용되지 않아 효율을 높일 수 있음을 유추할 수 있다.

그림 7 제안 HV switcher의 시뮬레이션 회로도 DC/DC converter를 통해 발생된 전류원을 0.2A로 설정하였

을 때, 출력과 효율을 시뮬레이션을 통하여 확인하였다.

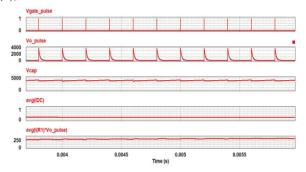

그림 8 제안 HV switcher의 시뮬레이션 결과 파형

0.2A의 입력, 390W의 부하 펄스 발생시, 전력손실의 큰 원인이 되었던 Charging resistor가 없기 때문에 회로의 모든 조건이 이상적이라는 가정하에 최대 이상 효율이 100%로 증가함을 확인 할 수 있다.

#### 2.4 시뮬레이션을 통한 제안 회로의 검증

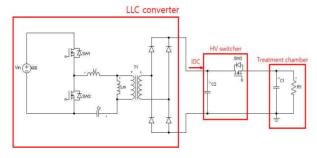

그림 9 제안된 고전압 펄스 발생 회로

제안된 펄스 발생 회로의 실 예로 그림 9와 같이 회로를 구성하였다. 회로의 DC/DC Power stage 부는 LLC topology를 활용한 공진형 컨버로 구성하여 전류원을 발생시키게 하였고 High voltage switcher 부는 cahrging resistor를 제외한 Energy storage 캐피시터와 스위치로 구성하였다. 제안 회로를 다음의 시뮬레이션을 통해 검증한다.

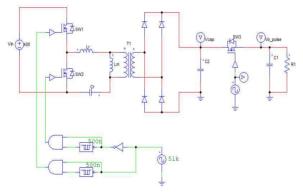

그림 10 제안 회로의 시뮬레이션 회로도

| SPECIFICATION |          |

|---------------|----------|

| VIN           | 400V     |

| Lr            | 85.2uH   |

| Cr            | 82.6nF   |

| IDC           | 0.2A     |

| T1 turn ratio | 10:182.5 |

| T1 Lm         | 512uF    |

표 1 제안 회로의 specification

그림 10과 표 1에 시뮬레이션 회로도와 specification을 나타내었다.

그림 11 제안 회로의 시뮬레이션 파형

시뮬레이션을 통하여 회로를 검증하였다. LLC converter를 통해 약 0.2A의 전류원을 제어하여 4kV의 고전압 펄스를 발생시키는 것을 확인할 수 있다. 이 과정에서 Charging resistor를 생략하였기 때문에 Charging rsistor로 인한 전력손실은 없다고 볼 수 있다.

#### 3. 결론

본 논문에서는 펄스 전기장 방식을 위한 기존 펄스 발생 회로에서의 효율과 비용 문제를 제기하였고 개선된 고전압 펄스 발생 회로를 제안하였다. Power stage에는 LLC topology의 공진형 컨버터를 사용하였고 기존 전압 제어 방식이던 회로를 전류 제어 방식의 회로로 바꾸어 전력 손실의 가장 큰 원인을 제공하는 Charging resistor인 Ri를 사용하지 않을 수 있었다. Charging resistor를 사용하지 않음으로써, 비용을 절감할 수 있고 출력대비 입력의 효율을 증가시켜 전기세 또한 저감할 수 있다.

본 연구는 과학기술정보통신부 및 정보통신기획평가원의 대학ICT연구센터지원사업의 연구결과로 수행되었음. (IITP-2020-2018-0-01396)

### 참 고 문 헌

- [1] Mahendra Pal(2017), Pulsed Electric Field Processing-An Emerging Technology for Food Preservation: Pal, J Exp Food Chem 2017, 3:2 ISSN:2472-0542

- [2] 백주원, 유동욱, 조정구, 정창용, Pavlov, 김학성, 김홍근 (1998). 고압 대전류 펄스 전계를 이용한 저온 살균장치 시스템 연구. 전력전자학회 학술대회 논문집, 162-165