# 전기철도용 전력보상장치 제어 및 실험

우제훈, 조종민, 박상해, 차한주 충남대학교 전기공학과

## Control and Experiment of Railway Power Compensator System

Jehun Woo, Jongmin Jo, Sanghae Park, Hanju Cha Department of Electrical Engineering. Chungnam National University

#### **ABSTRACT**

본 논문은 전기철도용 전력보상장치로 사용되는 단상 3레벨 인버터를 제작하였으며, 단상 3레벨 인버터의 유·무효 전력제어기를 설계하였다. 단상 3레벨 인버터는 유·무효전력을 제어하기 위해 가상 동기좌표계 축 상에서 PI 제어기를 통해 전류제어를 수행한다. DC 링크 제어는 3레벨 인버터를 고려할때 DC 링크 전압의 상단부와 하단부 전압의 평형상태를 유지하기 위해 제어하는 밸런싱 제어기를 포함한다. 10kVA 단상 3레벨 인버터 프로토타입을 설계하였으며, 안정한 유·무효전력제어 특성 실험 결과를 통해 단상 3레벨 인버터의 설계 및 제어 동작의 타당성을 검증하였다.

## 1. 서 론

국내 교류 전기철도의 급전 방식은 전력공급회사로부터 3상 전력을 수전받아 한국철도공사 변전소에서 스코트 변압기를 이 용하여 2개의 단상으로 변환하여 공급하고 열차에 급전 운행하는 방식을 적용하고 있다. 이때, 3상에서 단상으로 변환된 전력을 공급받는 열차의 부하로 인하여 3상의 전력공급시스템에서 전압 불평형이 발생하게 된다<sup>111</sup>.

이러한 전압 불평형은 전원 발전기의 발전용량 감소 뿐만아니라 역상전류로 인한 전동기 토크 감소 및 국부적 가열현상으로 인한 절연열화 등 회전기기 전반에 영향을 미치게 된다. 스코트 변압기는 전원측 불평형을 최소화하기 위해 철도급전시스템에 폭넓게 사용되고 있으나 각 상에서 실시간 급변하는 대용량 단상 차량부하로 인해 일반적으로 전원측 PCC(point of common coupling)에는 불평형이 발생한다<sup>12</sup>.

이러한 유·무효전력을 보상하여 불평형을 해결하기 위해 전기철도용 전력보상장치를 적용하는 연구가 진행되고 있으며, 전기철도용 전력보상장치의 토폴로지로는 3레벨 인버터와 MMC (Modular Multi-level Converter) 등이 있다. 본 논문에서는 전기철도용 전력보상장치로 사용되는 단상 3레벨 인버터의 설계 및 실험에 대해 서술하였다.

### 2. 단상 3레벨 NPC 타입 인버터 구성 및 제어

## 2.1 단상 3레벨 인버터 구성

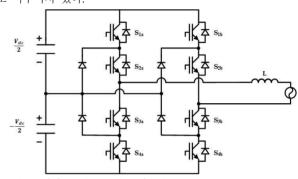

그림 1은 단상 3레벨 인버터의 구성을 보여주는 것으로 DC 전압원, DC 링크, 3레벨 NPC 타입 IGBT, L 필터, 단상 계통 으로 이루어져 있다.

그림 1 단상 3레벨 NPC 타입 인버터

Fig. 1 Single phase 3-level NPC type Inverter

#### 2.2 단상 3레벨 인버터 제어

단상 3레벨 인버터의 제어 기법으로는 유효전력 제어, 무효 전력 제어, DC 링크 밸런싱 제어 등이 있다. 본 논문에서는 전 류를 피드백 받아 유·무효전력 지령치에 해당하는 전류 지령치 로 전류를 제어하는 방법을 사용했다.

## 2.2.1 유·무효 전력 제어

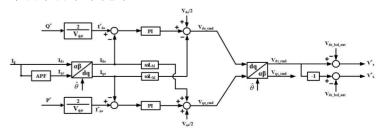

그림 3은 유·무효전력 제어의 전체적인 제어 블록도를 나타내고 있다. 유·무효전력은 동기 좌표계인 d-q축 상에서 PI 제어기를 이용해 제어하게 된다. 본 논문에서 구성한 시스템은 단상 인버터이기 때문에 APF (All Pass Filter)를 사용하여 90° 지연된 q축을 만들고 이를 회전좌표변환을 통해 d-q축 상에서 제어한다. 유효전력의 경우 q축 전류를 통해 제어하고, 무효전력의 경우 d축 전류를 통해 제어하게 된다. 유효전력과 무효전력의 지령치에 해당하는 전류 지령치를 계산하는 수식이식 (1)과 (2)에 나타난다.

그림 3 유효전력 및 무효전력 제어 블록도

Fig. 3 P-Q control block diagram

$$I_{qe\_ref} = \frac{2P^*}{V_{qe}} \tag{1}$$

$$I_{de\_ref} = \frac{2Q^*}{V_{qe}} \tag{2}$$

## 2.2.2 DC 링크 밸런싱 제어

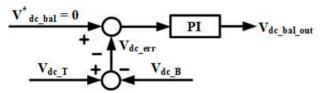

DC 링크 밸런싱 제어기는 상단부 전압과 하단부 전압의 차이를 PI 제어기의 입력으로 받아 지령치인 0으로 제어하게 된다. 그림 2는 DC 링크 밸런싱 제어기의 구조를 나타낸다.

그림 2 DC 링크 밸런싱 제어기

Fig. 2 DC-link balancing controller

#### 2.3 시뮬레이션 결과

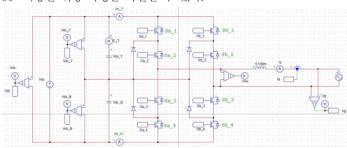

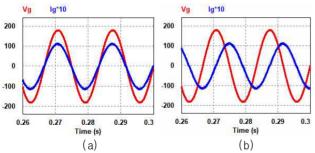

그림 4는 PSIM 시뮬레이션의 구성을 보여주는 것으로 DC 전압원, DC 링크 커패시터, NPC 구조의 IGBT, 그리고 출력부의 L필터와 단상 계통으로 구성된다. 그림 5 (a)와 (b)는 각각 유효전력 제어와 무효전력 제어 시뮬레이션의 결과 파형을 나타낸다. 유효전력 제어는 1kW의 지령치로 제어했으며 단위역률 제어로 전압과 전류가 동상인 것을 확인할 수 있다. 무효전력 제어는 1kVar의 지령치로 제어했으며 전압에 대해 전류가 90° 지상인 위상 특성을 확인할 수 있다.

그림 4 단상 3레벨 인버터 시뮬레이션 회로

Fig. 4 Single-phase 3-level Inverter simulation circuit

그림 5 시뮬레이션 결과 (a) 유효전력 제어 (b) 무효전력 제 어

Fig. 5 Simulation results (a) P control (b) Q control

## 2.4 하드웨어 구성 및 실험

그림 6은 전체적인 하드웨어의 구성을 나타내는 것으로 시뮬레이션을 바탕으로 하드웨어를 구성하였으며 본 논문에서는 직접 설계한 인버터 스택을 사용하여 단상 3레벨 인버터를 구 성하였다. 제어보드에는 TMS320F28377D 제어기를 사용했다. 그림 7 (a)와 (b)는 단상 3레벨 인버터의 유효전력 및 무효전력 제어 실험 파형을 보여주는 것으로 실험 조건은 시뮬레이션과 동일하게 진행하였다. 유효전력의 경우 전압과 전류가 동상이고 무효전력의 경우 전압에 대해 전류가 90° 지상인 위상 특성으로 시뮬레이션과 동일한 결과를 확인할 수 있다.

그림 6 단상 3레벨 인버터 하드웨어 프로토타입 Fig. 6 Single-phase 3-level Inverter hardware prototype

그림 7 실험 결과 (a) 유효전력 제어 (b) 무효전력 제어 Fig. 7 Experimental result (a) P control (b) Q control

#### 3. 결 론

본 논문에서는 10kVA급 단상 3레벨 인버터를 시뮬레이션을 통해 검증하였고, 이를 바탕으로 하드웨어를 설계하여 유효, 무효 및 DC 링크 밸런싱 제어기를 접목하였다. 또한 설계된하드웨어를 실제 계통에 연계하고 유·무효전력 제어 실험을 하여 성능을 검증하였으며, 검증결과 시뮬레이션과 비교하여 실제 하드웨어가 동일한 동작을 하는 것을 확인하였다.

#### 참 고 문 헌

- [1] 김정철 "급전계통 해석과 한국철도전기의 이해", 기다리, 2018.08

- [2] 손국현, 최규형, 김성일, 정호성 "전기철도 급전시스템에서 SVC를 이용한 전압불평형 보상에 관한 연구", 한국철도학회 학술발표대회논문집, 2011.10, 3124-3132 (9 pages)