# 기생 인덕턴스를 최소화한 GaN FET 구동 게이트 드라이버 설계

부한영, 조영훈 건국대학교 전기공학과

## Gate Driver Design for GaN FET Minimizing Parasitic Inductances

Hanyoung Bu, Younghoon Cho Konkuk Univ.

## **ABSTRACT**

최근, WBG 반도체 소자에 대한 연구가 활발히 진행됨에 따라 고속 스위칭으로부터 발생되는 문제점들을 해결하기 위한여러 방안들이 제시되고 있다. WBG 반도체 소자의 안정적인고속 스위칭을 실현하기 위해서는 게이트 드라이버 내에존재하는 기생 인덕턴스를 최소화하는 것이 가장 중요하다. 본논문에서는 layout의 최적화 설계를 통해 GaN FET 구동용게이트 드라이버 내의 기생 인덕턴스를 최소화할 수 있는 방안을 제시하고 설계를 통해 만들어진 게이트 드라이버를 실험을 통해 스위칭 특성을 분석하였다.

### 1. 서 론

본 논문에서는 WBG 반도체 소자 중 GaN FET 소자를 이용하여 GaN FET 구동용 게이트 드라이버를 최적 설계한다. 게이트 드라이버와 GaN FET 사이에 존재하는 기생 인덕턴스를 최소화함으로써 안정적인 스위칭 동작을 보장할 수 있다. [1] 제작된 게이트 드라이버를 실험을 통해 스위칭 파형을 검증하고, 드레인-소스 전압의 링잉(Ringing) 성분을 줄이기위한 RCD스너버 회로를 적용하여 그 효과를 관찰하였다.

## 2. 게이트 드라이버 설계

### 2.1 게이트 드라이버 회로 설계

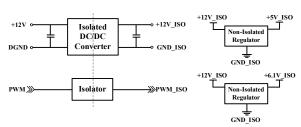

먼저, GaN FET 소자를 구동하기 위한 게이트 드라이버의 회로를 설계하였다. 게이트 드라이버는 크게 두 부분으로 나눌 수 있는데, 그 중 첫번째는 게이트 드라이버 입력 신호의 절연 및 전원을 생성하는 전원부이다. 그림 1에서와 같이 절연형 DC/DC 컨버터를 이용하여 절연 전원과 절연 접지를 생성하였다. 또한 디지털 절연기(Digital Isolator)를 사용하여 PWM 신호의 공통 모드 성분의 dv/dt 변화에 강인하도록 설계하였다. 해당 디지털 절연기는 5kVms의 절연 내력과 50kV/us의 공통 모드 dv/dt 내성을 가지고 있어 우수한 절연 능력을 보여준다.[2]

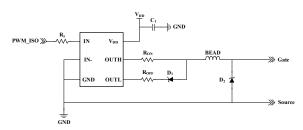

두번째는 게이트 드라이버와 GaN FET 소자의 게이트를 연결하는 게이트 드라이버부이다. 게이트 드라이버부를 구성할 때 가장 중요한 것은 원치 않는 턴 온 현상(Unwanted turn on)이 발생하지 않도록 스위칭 전압의 안정성을 확보하는 것이다. 안정성을 확보하기 위한 방법 중하나는 GaN FET 소자의 게이트-드레인 커패시터(Miller Capacitor)로 인해 발생하는 밀러 턴 온 효과(Miller Turnon Effect)를 방지하기 위해 턴 온, 턴 오프 전류 패스를 분리하는 것이다. 이런 구성은 게이트 드라이버 출력에 낮은 풀다운(Pulldown) 임피던스를 가질 수 있어 밀러 턴 온 효과에 강인함을 가진다. 또한 4A 소스, 8A 싱크 전류

능력을 갖는 게이트 드라이버를 선정하고 높은 싱크 능력을 이용하여 밀러 턴 온 효과를 방지하였다.<sup>[3]</sup>

그림 1 게이트 드라이버의 전원부 회로 Fig. 1 Power Stage Circuit of Gate Driver

그림 2 게이트 드라이버부 회로 Fig. 2 Gate Driver Circuit

그림 3 게이트 드라이버의 싱크 전류의 흐름 Fig. 3 Flow of Sink Current for Gate Driver

#### 2.2 게이트 루프 내의 기생 인덕턴스 분석

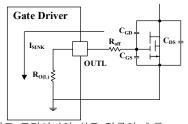

게이트 드라이버 게이트 루프 내의 기생 인덕턴스는 링잉 (Ringing)성분과 dv/dt 성분의 오버슈트(Overshoot)를 동반하기 때문에 턴 온 또는 턴 오프 시 스위치에 스트레스를 가할 수 있다. 따라서, 게이트 루프 내의 기생 인덕턴스를 최소화하는 것이 중요하다.

본 논문에서는 ANSYS Electronics 소프트웨어의 Q3D Extractor 툴을 이용하여 기생 인덕턴스 분석을 진행하였다. 분석에 진행된 솔루션 주파수(Solution Frequency)는 수십kHz에서 수백MHz사이의 주파수를 선정하여 인덕턴스 값의 변화를 살펴보았다. 분석 결과 주파수에 따라 약

3.6nH의 기생 인덕턴스 값을 가지며 값의 변동이 거의 없음을 알 수 있었다.

그림 4 ANSYS Electronics를 이용한 기생 인덕턴스 분석 Fig. 4 Analysis of Parasitic Inductances

## 3. 실험 결과

## 3.1 게이트-소스 전압 확인

위 설계에 따라 제작된 게이트 드라이버의 동작을 확인하기 위해 게이트-소스 전압을 확인하였다. 해당 게이트 드라이버는 GaNSystems사의 GS66508T 소자 구동용 게이트 드라이버로 제작되었다.

그림 5 게이트-소스 전압 파형

Fig. 5 The Waveform of Gate-Source Voltage

그림 5의 파형과 같이 게이트-소스 전압이 GaN FET 소자 구동 전압(턴 온 전압 : 6V, 턴 오프 전압 : 0V)을 만족하는 것을 확인할 수 있다. 그러나 턴 온 지점에서 약-2.3V의 음의 오버슈트를 확인할 수 있는데 이는 밀러 커패시터를 통해 흐르는 전류가 음의 오버슈트를 발생하기 때문이다. 턴 온, 턴 오프 저항을 적절히 바꿔 줌으로써 오버슈트의 크기를 감소할 수 있다.

#### 3.2 하프 브리지 인버터 실험

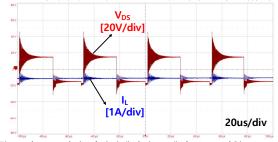

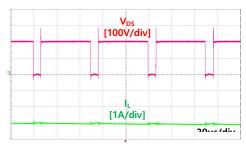

RL부하를 포함한 하프 브리지 인버터 시스템을 구성하고, GaN FET 소자에서의 드레인-소스 전압 파형을 확인하였다.

그림 6 하프 브리지 인버터에서의 드레인-소스 전압 Fig. 6 Drain-Source Voltage in the Half Bridge Inverter

실험 결과, 파워 루프 내 존재하는 기생 인덕턴스 및 기생 커패시터의 영향으로 드레인-소스 전압 파형에 극심한 링잉(Ringing) 현상이 발생하는 것을 그림 6에서 확인할 수 있다.

링잉 현상을 방지하고 안정적인 스위칭 동작을 확보하기 위해

RCD 스너버를 스위치 레그 사이에 삽입하여 그 효과를 관찰하였다.

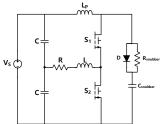

그림 7 RCD 스너버를 적용한 하프 브리지 인버터 회로 Fig. 7 The Half Bridge Inverter applying RCD Snubber

#### 표 1 회로 파라미터

Table 1 The Parameters of Circuit

| 입력전압(Vs)   | 200V      |

|------------|-----------|

| DC 링크 커패시터 | 4700uF    |

| RL부하       | 10Ω, 20mH |

| 스너버 저항     | 5 Ω       |

| 스너버 커패시터   | 15uF      |

그림 8 RCD 스너버를 적용한 드레인-소스 전압 Fig. 8 Drain-Source Voltage applying RCD Snubber

RCD 스너버를 적용한 결과, 그림 8과 같이 링잉 현상이 현격하게 줄어든 것을 확인할 수 있다.

#### 4. 결 론

본 논문에서는 GaN FET 소자 구동용 게이트 드라이버를 설계하고 실험을 통해 스위칭 파형을 검증하였다. RCD 스너버를 사용하여 드레인-소스 전압에서의 링잉 성분을 감소하였다. 그러나 턴 오프 시 오버슈트의 크기가 드레인-소스 전압의 %50 수준으로 나타나 안정된 스위칭을 달성하기 어렵다. 따라서, 앞으로 스너버 값 설계 및 게이트저항 재선정을 통해 해당 부분에 대한 연구를 계속 진행할 예정이다.

이 논문은 2017년도 정부(미래창조과학부)의 재원으로 한국연구재단의 지원을 받아 수행된 기초연구사업임 (No.2017R1C1B2009425)

#### 참 고 문 헌

- [1] Seiya Ishiwaki, Toshihiro Iwaki, "Analysis of False Turn-On Phenomenon of GaN HEMT with Parasitic Inductances for Propose Novel Design Method Focusing on Peak Gate Voltage", 2017 IEEE INTELEC, pp. 347-350, 2017, Oct.

- [2] Silicon Lab, "Si861x/2x Data Sheet"

- [3] Texas Instrument, "UCC2751x Single-Channel, High-Speed, Low-Side Gate Driver"