# 고주파 LLC 공진형 컨버터를 위한 FPGA 제어기 디자인

박화평, 김민아, 정지훈 울산과학기술원 (유니스트)

## High Frequency LLC Resonant Converter Using FPGA Controller

Hwa Pyeong Park, Mina Kim, and Jeehoon Jung Ulsan National Institute of Science and Technology (UNIST)

#### **ABSTRACT**

기존 Digital Signal Processor (DSP)를 사용하여 높은 동작주파수의 LLC 공진형 컨버터를 구동하는 경우 낮은 동작 주파수 분해능과 계산 속도에 의해 출력 전압 제어성능과 동특성에 한계가 생긴다. 이를 해결하기 위해 기존의 분해능 및 계산 속도 부족에 의한 영향을 분석하고 Field Programmable Gate Array (FPGA)를 설계하여 높은 동작주파수 분해능 및 동특성을 얻고자 제안한다. FPGA를 이용한 성능향상을 DSP (TI TMS 38335)와 FPGA (Xilinx XC7A100T)를 사용하여 비교

TMS 38335)와 FPGA (Xilinx XC7A100T)를 사용하여 비교 분석하고자 한다.

#### 1. 서론

기존의 Digital Signal Processor (DSP)는 노이즈에 취약하지 않고 다양한 제어 기법을 활용할 수 있기 때문에 LLC 공진형 컨버터를 구동하는데 널리 사용되고 있다 [1]. 하지만 기존 DSP는 높은 동작주파수를 구현하는데 주파수 분해능의 한계가 있고 낮은 주파수 분해능에 의해 큰 출력 전압 리플, 1차 2차측 전류 변동이 생긴다. 뿐만 아니라 DSP는 제어 연산 속도의한계에 의해 높은 스위칭 주파수에서 제어기를 디자인하여 빠른 동특성을 얻지 못한다.

Field Programmable Gate Array (FPGA) 기반의 제어기는 빠른 시스템 동작 주파수와 연산 병렬화를 통해 높은 주파수분해능 및 제어 연산 속도를 가진다. 본 논문에서는 FPGA를 사용하여 주파수 분해능 문제를 해결함과 동시에 빠른 제어 연산 속도를 통한 빠른 동특성을 얻고자 한다.

## 2. FPGA를 이용한 성능 향상

## 2.1 주파수 분해능 향상

본 논문에서 사용한 DSP와 FPGA는 각각 150 MHz, 450 MHz의 시스템 동작 주파수를 가지고 있고, 이는 PFM의 주파수를 만들기 위한 삼각파의 Time Step을 결정한다. 이 Time step은 다음과 같이 계산할 수 있다.

$$T_{b,prd} = \frac{T_s}{2T_{th \ c/k}} \tag{1}$$

$T_{b,prd}$ 는 Time Step의 개수이고,  $T_s$ 는 스위칭 주기,  $T_{tb,ck}$ 은 시스템 동작 주기이다. 이를 이용하여 스위칭 주파수의 분해능을 구하면 다음과 같다.

$$\Delta f_s = \frac{1}{2T_{tb,clk}} \left( \frac{1}{T'_{b,prd}} - \frac{1}{T_{b,prd}} \right)$$

(2)

(1)과 (2)를 사용하면 1 MHz의 동작주파수에서 DSP는 13.158 kHz의 주파수 분해능을 가지고 FPGA는 2.2 kHz의 주파수 분해능을 가짐을 알 수 있다. 위의 주파수 분해능에 따른 전압이 득 변동은 다음과 같이 나타낼 수 있다.

$$G(\Delta T_{b,prd}) = \left\| H_r \left( \frac{T'_{b,prd}^{-1}}{2T_{tb,clk}f_r} \right) - H_r \left( \frac{T_{b,prd}^{-1}}{2T_{tb,clk}f_r} \right) \right\|$$

(3)

이때  $H_r$ 은 LLC 공진형 컨버터의 전압이득이고,  $f_r$ 은 공진 주파수이다. (3)을 이용하면 FPGA는 DSP에 비해 15배 작은 출력 전압 변동을 얻을 수 있다.

## 2.2 동특성 향상

LLC 공진형 컨버터는 동작 주파수가 증가함에 따라 높은 Crossover frequency를 설계할 수 있다. 이상적인 디지털 제어기의 경우 모든 제어 연산이 스위칭 주기 내에 끝나고 다음 스위칭 주기에 업데이트된다. 하지만 실제 제어기의 경우 제어연산 속도의 한계에 의해 높은 스위칭 주파수에서 Cycle by Cycle 제어를 구현하기 어렵다. 1 MHz의 동작 주파수에서 DSP는 PI 제어기를 사용하였을 경우 14 us의 Time Delay가 1번의 제어 연산을 끝내기 위해 발생한다. 반면 FPGA는 2 us의 Time Delay가 발생한다. Time Delay의 전달함수는 다음과 같이 나타낼 수 있다.

$$G_{delay}(s) = \frac{1 - e^{-sT_{delay}}}{sT_{delay}} \cong \frac{1}{1 + \frac{sT_{delay}}{2}}$$

(4)

이를 고려하면 컨버터의 Crossover Frequency는 Time Delay 보다 충분히 낮은 주파수에서 형성되어야 함을 알 수 있다.

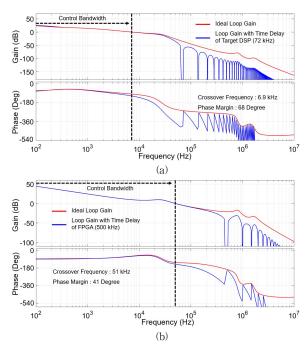

그림 1 (a)는 DSP 제어기의 Time Delay를 고려한 Loop Gain을 나타낸다. 그림 1 (b)는 FPGA의 Time Delay를 고려한 Loop Gain을 나타낸다. DSP에 비해 FPGA가 7.4배 높은 Crossover Frequency를 가짐을 보이고 이는 빠른 컨버터의 동특성을 의미한다.

#### 3. 실험 결과

본 논문은 Hardware in the Loop (HIL) 테스트를 통해 제어기의 제어 연산 속도 및 주파수 분해능을 측정하였고, 이 측정된 값들을 이용하여 PSIM 시뮬레이션 모델을 구성하였다.

그림 1 제어기에 따른 Loop Gain: (a) DSP를 사용한 Loop Gain, (b) FPGA를 사용한 Loop Gain.

Fig. 1 Loop Gain according to the controller: (a) Loop Gain of the DSP, (b) Loop Gain of the FPGA

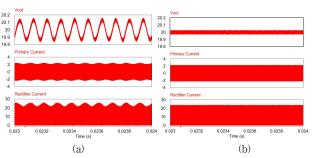

그림 2 제어기에 따른 Time Delay 및 주파수 분해능 비교: (a) 경부하에서 전부하로 변할 때 FPGA 제어 성능, (b) 경부하에서 전부하로 변할 때 DSP 제어 성능.

Fig. 2 Comparison of time delay and switching frequency resolution: (a) FPGA controller with light to heavy load change, (b) DSP controller with light to heavy load change.

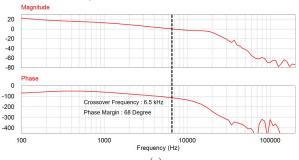

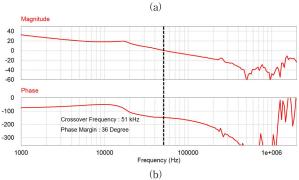

PSIM 시뮬레이션을 사용하여 출력 전압 리플 및 소신호 응답을 측정하고 나타내었다. 그림 2는 HIL 테스트를 통한 제어기에 따른 제어 연산 속도 및 주파수 분해능을 나타낸다. 그림 3은 제어기에 따른 출력 전압 리플을 나타내고, 그림 4는 제어기에 따른 소신호 응답 특성을 PSIM을 사용하여 측정하였다.

그림 3 제어기에 따른 출력 전압 리플: (a) DSP, (b) FPGA.

Fig. 3 Simulation results of output voltage ripple: (a)

DSP case, (b) FPGA case.

#### 4. 결론

본 논문은 제어기 설계에 따른 LLC 공진형 컨버터의 제어특성을 분석하고 작은 출력 전압 리플 및 빠른 동특성을 구현하기 위한 방법으로 FPGA 제어기를 제안하였다. 이를 증명하기 위하여 HIL 테스트을 통한 신호 레벨 실험을 진행하여 제어기에 따른 성능을 확인하였다.

이 논문은 2016년 정부(교육부)의 재원으로 한국연구재단의 지원을 받아 수행된 중견연구사업임 (NRF2016R1A2B4011934)

## 참 고 문 헌

[1] A. Prodic, D. Maksimovic and R. W. Erickson, "Design and implementation of a digital PWM controller for a high frequency switching DC DC power converter," Industrial Electronics Society, 2001, pp. 893-898 vol.2.