# 고효율 저비용을 위한 인터리브드 준공진 플라이백 컨버터에 적용된 최적의 밸리 스위칭 기법

서동우, 이준희, 이교범 아주대학교

# Optimal Valley Switching Method for High Efficiency and Low Cost Interleaved Quasi-Resonant Flyback Converter

Seo. Dong woo, Lee. June hee, Lee. Kyo Beum Ajou University

#### **ABSTRACT**

본 논문은 인터리브드 준공진 플라이백 컨버터에 추가회로 없이 적용된 최적의 밸리 스위칭 기법을 제안한다. 인터리브드 준공진 플라이백 컨버터는 스위치 양단 전압(Drain Source voltage)  $V_{DS}$ 이 최소화 되는 지점에서 스위치 턴 온이 되어 전체 시스템의 효율이 향상되고, EMI (Electro Magnetic Interference)와 EMC (Electro Magnetic Compatibility)의 영향을 최소화시킬 수 있다. 제안한 기법은 MCU (Micro Controller Unit) 기반 소용량 컨버터에 간단한 수식을 이용하여 최적의 밸리 스위칭 기법을 가능하게 한다. 제안한 기법은 시스템의 가격과 부피 상승 없이 효율을 향상시키고, EMI와 EMC의 영향을 최소화시킨다. 제안하는 기법의 성능은 시뮬레이션을 통해 확인하였다.

## 1. 서 론

최근 정보화 사회의 발전에 따라 전자기기의 보급이 증가하 여 전원의 중요성 또한 높은 비중을 차지한다. DC DC 컨버터 는 고효율화 및 경량화, 노이즈 저감 등을 위한 기술이 요구되 고 있으며, 다양한 컨버터가 SMPS (Switched Mode Power Supply)에 적용되고 있다. 그중 플라이백 컨버터는 구조가 간 단하고 부품의 수가 적기 때문에 주로 소용량 전원시스템에 적 용되며, 변압기를 사용하여 1차 측과 2차 측을 절연시킨 컨버 터로서 저비용과 고효율의 장점이 있다.[1] 플라이백 컨버터의 손실에 대한 주요 원인은 스위치 동작에 따른 스위칭 손실과 전도손실, 변압기의 동손과 철손이다. 현재 변압기는 제조방법 이나 새로운 물질의 코어로 손실을 낮추고 있고, 스위칭 손실 은 많은 연구를 통해 다양한 소프트 스위칭 기법이 제안되었 다. 최근에는 스위치와 병렬로 기생 캐패시터를 추가하여 준공 진 플라이백 컨버터를 구성하고, 변압기의 자화인덕턴스와 스 위치의 기생 캐패시터의 공진현상을 이용하여 스위치 양단 전 압  $V_{DS}$  이 최소화 되는 지점에서 다음 스위치 동작을 수행하 는 밸리 스위칭 기법이 많이 사용된다. 하지만 준공진 플라이 백 컨버터는 스위칭 손실을 최소화 할 수 있지만 밸리를 검출 하는 추가 회로가 필요하다는 단점이 있다. 또한 밸리의 개수 에 따라 스위칭 주파수가 가변하게 되는데 출력 전력에 따라 밸리의 개수를 조절하려면 추가회로의 가격이 상승한다.[2]

본 논문은 인터리브드 준공진 플라이백 컨버터에 추가 회로

없이 MCU를 통해 제안하는 기법을 적용하여 밸리 스위칭을 동작한다. MCU로 소프트 스위칭을 가능하게 할 수 있기 때문 에 시스템의 가격과 부피 상승에 영향을 주지 않는다. PSIM을 이용하여 제안하는 최적의 밸리 스위칭 기법의 타당성을 검증 하였다.

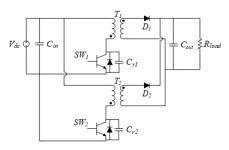

그림 1. 인터리브드 준공진 플라이백 컨버터 Fig. 1. Interleaved Quasi-Resonant Flyback Converter

#### 2. 인터리브드 준공진 플라이백 컨버터

#### 2.1 토폴로지 구성

그림 1은 플라이백 컨버터 2개를 병렬로 연결한 인터리브드 준공진 플라이백 컨버터이다. 인터리브드 방식을 사용해  $180^\circ$ 의 위상차를 두어 입력전류를 절반으로 나누어 흐르게 함으로써 입출력 전류 리플은 감소한다.  $V_{DS}$ 는 스위치 오프 상태동안 변압기 2차 측 전류가 부하로 모두 흐른 후에 변압기의 자화인덕턴스  $L_m$ 과 스위치의 기생 커패시터  $C_r$ 의 공진현상으로 밸리 스위칭 한다.  $V_{DS}$ 가 최소가 되는 점에서 스위치 턴온 시, 스위칭 손실이 저감된다. [3]

#### 2.2 제안된 밸리 스위칭 기법

기존 공진형 플라이백 컨버터는 밸리 스위칭 방식으로 EMI, EMC의 영향을 최소화 할 수 있지만, 여러 가지 IC칩으로 구성된 아날로그 보조회로가 추가되어 비용과 부피가 증가하는 단점이 있다. 또한 경부하시 스위치의 온 시간이 짧아짐에 따라 전체적인 스위칭 주파수가 증가하므로 스위칭 손실이증가한다. 따라서 본 논문에서는 MCU를 통해 제안하는 최적의 밸리 스위칭 기법을 사용하여 모든 출력 범위에서 우수한성능을 나타내도록 한다. 스위칭 주파수는 스위치의 온, 오프주기와 공진 주기의 합으로 결정된다. 공진 주기는  $L_m$ 과  $C_r$ ,

공진계수  $\alpha$ 로 계산된다. 공진계수는 변압기 1차 측의 피크전 류로 결정되며 피크전류가 낮을 때 공진계수를 증가시켜 스위 칭 주파수를 감소시킨다. 이럴 경우 낮은 출력에서 불필요하게 스위칭 주파수가 증가하는 것을 막아준다. 공진주기와 변압기 1차측 피크전류는 (1). (2) 와 같다.

$$t_r = \alpha 2\pi \sqrt{L_m C_r} \,, \tag{1}$$

$$I_{peak} = \frac{V_{dc}}{L_m} t_{on} = \frac{n V_{off}}{L_m} t_{off}. \tag{2}$$

n은 변압기의 턴수비 이며, (1)과, (2)를 사용하여 제 안하는 스위칭 듀티비는 다음과 같다.

$$Duty = \frac{t_{on}}{T_{samp}} = \frac{\frac{I_{peak}L_m}{V_{dc}}}{\frac{I_{peak}L_m}{V_{dc}} + \frac{I_{peak}L_m}{n V_{out}} + \alpha 2\pi \sqrt{L_m C_r}}.$$

(3)

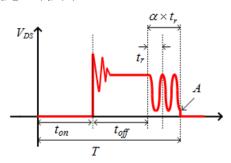

그림 2는 준공진 플라이백 컨버터 스위치의  $V_{DS}$  를 나타낸 다. 공진계수 lpha가 2.5일 때 스위치가 턴 온 되는 시점은  $V_{DS}$ 가 최소점인 A지점이다.

그림 2. 스위치 드레인 소스 전압 Fig. 2. Drain Source voltage of Switch

#### 3. 시뮬레이션 결과

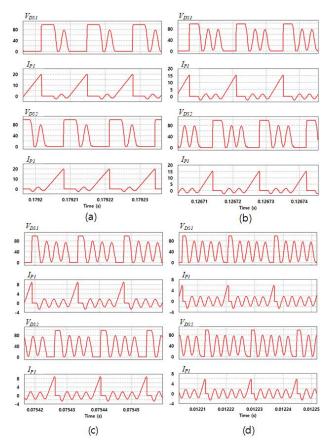

PSIM을 통해 제안하는 최적의 밸리 스위칭 기법을 검증했 다. 시뮬레이션 파라미터는 표 1과 같다. 그림 3은 준공진 플라 이백 컨버터에 제안한 밸리 스위칭 기법을 적용한 파형이다. 스위치 1과 스위치 2는 180°의 위상차를 가지며 동작한다. 준 공진 플라이백 컨버터의 출력 전력을 가변 하여 최적의 밸리 스위칭 동작을 확인 하였다. 출력 전력에 따라 공진 주기를 조 절하여 높은 출력전력 일 때 공진주기를 최소화 하여 스위칭 주파수가 과도하게 낮아지지 않도록 하고, 낮은 출력전력일 때 공진주기를 증가시켜 스위칭 주파수가 과도하게 상승하지 않도 록 한다. 따라서 제안한 기법은 스위칭 주파수에 따른 손실감 소 및 EMI, EMC 영향을 최소화 한다.

#### 4. 결론

본 논문은 준공진 인터리브드 플라이백 컨버터를 위한 최적 의 밸리 스위칭 기법을 제안했다. 제안하는 기법은 보조회로나 PWM IC칩 없이 MCU 출력 전력에 따른 최적의 공진주기를 계산한다. 제안하는 최적의 밸리 스위칭 기법을 통해 시스템의 가격과 부피 증가 없이 효율을 증가시키고, EMI, EMC의 특성

을 개선할 수 있으며, 마이크로인버터와 같은 소용량 인버터 시스템에 적용이 가능하다.

표. 1 시뮬레이션 파라미터

Table. 1 Simulation Parameters

| Parameter    | Value                | Parameter | Value   |

|--------------|----------------------|-----------|---------|

| $V_{in}$     | 40 V                 | $L_m$     | 10 μF   |

| $V_{out}$    | 400 V                | $C_r$     | 22 nF   |

| Output Power | 300 W                | $C_{in}$  | 1100 μF |

| Peak Current | 20 A <sub>peak</sub> | $C_{out}$ | 2200 μF |

| n            | 7                    | R         | 100 Ω   |

그림 3. 제안한 기법을 적용한 시뮬레이션 파형

- (a) 100% 출력전력

- (b) 75% 출력전력

- (c) 50% 출력전력

- (d) 25% 출력전력

Fig. 3 Simulation waveforms of Proposed Algorithm

- (a) 100% Output Power (b) 75% Output Power

- (c) 50% Output Power

- (d) 25% Output Power

## 참 고 문 헌

- [1] C. Olalla, D. Clement, M. Rodriguez, and D. Maksimovic, "Architectures and Control of Submodule Integrated DC-DC Converters for Photovoltaic Applications," IEEE Transactions on Power Electronics, vol. 28, no. 6, pp. 2980-2997, Jun. 2013.

- J. M. Kwon, W. Y. Choi, and B. H. Kwon, "Single-Stage Quasi-Resonant Flyback Converter for a Cost-Effective PDP Sustain Power Module," *IEEE Transactions on Industrial* Electronics, vol. 57, no. 6, pp. 2187-2190, Jun. 2010.

- June-Hee Lee, June-Seok Lee, and Kyo-Beum Lee, "Current Sensorless MPPT Control Method for Dual-Mode PV Module-Type Interleaved Flyback Inverters," Journal of Power Electronics, vol. 15, no. 1, pp. 54-64, Jan. 2015.