# Body-Bias Technique을 이용한 저전압 진동에너지 하베스팅 전파정류회로

박근열, 유종근

인천대학교

A Low-Voltage Vibrational Energy Harvesting Full-Wave Rectifier using Body-Bias Technique

Keun-Yeol Park, Chong-Gun Yu Incheon National University E-mail: keunyeol89@naver.com

#### 요 약

본 논문에서는 진동 에너지를 이용하여 에너지를 수확하는 전파 정류 하베스팅 회로를 설계하였다. 설계된 회로는 저전압에서도 전력효율이 우수하도록 Beta-Multiplier를 이용하여 Body-Bias technique을 Negative Voltage Converter에 적용하였으며, Comparator를 Bulk-Driven type으로 설계하였다. 제안된 회로는  $0.35 \mu$ m CMOS 공정으로 설계하였으며, 설계된 회로의 칩 면적은  $931 \mu$ m  $\times$  785  $\mu$ m이다.

#### **ABSTRACT**

This paper describes a full-wave rectifiers for energy harvesting circuit using a vibrational energy. The designed circuit is applied to the negative voltage converter with the body-bias technique using the Beta-multiplier so that the power efficiency is excellent even at the low voltage, and the comparator is designed as the bulk-driven type. The proposed circuit is designed with 0.35  $\mu$ m CMOS process, and The designed chip occupies 931 $\mu$ m  $\times$  785 $\mu$ m.

#### 키워드

Energy Harvesting, Low-Voltage, Body-Bias Technique, Full-Wave Rectifiers

## I . 서 론

IoT에 대한 관심과 기술의 발전으로 디바이스들은 소형화되고 있으나 많은 데이터량을 처리해야한다. 그로 인해 기기들의 전원공급 방법이 매우 중요해 졌으며 필요한 에너지를 열과 진동, 빛 등을 이용하여 전기에너지로 변환하는 기술인 에너지 하베스팅 기술이 매우 유용할 것으로보인다. 또한, 이러한 기술이 저전압에서도 고효율로 동작 할 수 있어야 한다. 주변에 존재하는에너지들은 대게 AC 형태이기 때문에 먼저 DC신호로 변환하기 위한 AC-DC 변환기가 필요하며 수확된 진동에너지가 부하로 잘 전달되기 위해서는 AC-DC 변환기의 전력변환효율이 높아야

하며 AC-DC 변환기 자체의 전력효율도 높아야 한다.

AC-DC 변환기는 4개의 MOS 스위치로 구성된 NVC (Negative Voltage Converter)와 능동 (active) 다이오드로 구성된 능동 구조가 주로 이 용되고 있다 [1-3]. 또한, 저전압 동작을 위해 Body-Bias technique을 적용하여 NVC에 사용되 는 MOS 트랜지스터 문턱전압을 낮춘 AC-DC 변 환기[2]도 보고된바 있다. 그러나 수확된 전압 레벨이 변하면 Body Bias 전압 또한 비례해서 변하므로 동작 가능한 입력 전압 범위가 제한적 수밖에 없다. 이를 개선하기 일 Beta-Multiplier를 사용하여 Body-Bias technique 을 적용한 회로가 보고되었으나 [3], 저전압에서 동작을 하지 못하였다.

이 논문은 IDEC 지원에 의해서 일부 수행되었음.

본 논문에서는 이러한 문제점을 해결하기 위해 Beta-Multiplier의 PVT 특성을 개선하여 더 안정적으로 Body Bias 전압을 공급하여 효율을 향상시키도록 하였고, Comparator에 전류를 공급하는 Beta-Multiplier 또한 PVT를 개선시켜 비교기의 성능을 향상시켰다. 또한, 제안된 AC-DC 변환기를 적용한 진동에너지 하베스팅 회로를 0.35um CMOS 공정으로 설계하였다.

## Ⅱ. 회로 설계 및 검증

#### 2.1 AC-DC Converter

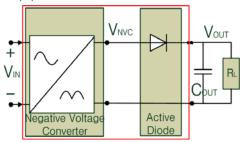

AC-DC 변환기는 두 개의 단으로 NVC와 Active Diode로 구성된다. 첫 번째 단인  $V_{\rm NVC}$ 는 입력 교류전압의 음의 영역을 양의 영역으로 바꾸는 역할을 한다. 그러나 NVC만으로는 전류 방향이 제어가 되지 않기 때문에 역전류에 의해 Load Capacitor의 전하를 유지시킬 수 없다는 문제점이 있다. 따라서 두 번째 단인 Active Diode가 필요로 하다. 그림 1은 AC-DC 변환기의 블록도이다.

그림 1. AC-DC 변환기의 블록 다이어그램

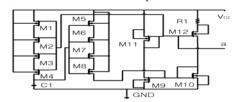

## 2.2 Negative Voltage Converter

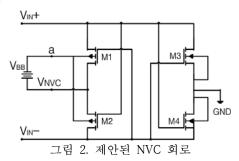

본 논문에서 제한된 NVC의 회로도를 그림 2에 보였다. PMOS의 Body 단자에 전압을 인가하여 문턱전압을 낮춰 낮은 전압에서도 MOSFET이동작하게 할 수 있는 기술인 Body Bias technique을 사용하여 낮은 전압에서도 전파정류동작을 할 수 있도록 설계하였으며 기존 논문[3]보다 전체적인 사이즈를 줄여 Leakage Current를 감소시켰다.

NVC의 PMOS Body 단자에 인가되는 순방향바이어스 전압은 문턱전압을 넘지 않는 선에서 클수록 전력 효율이 좋다. 그러나, 문턱전압을 넘어 Diode가 On 될 정도로 커지면 Body Diode에서의 누설전류를 인해 효율이 다시 감소하게되다

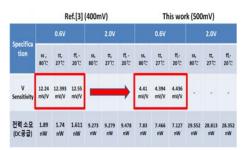

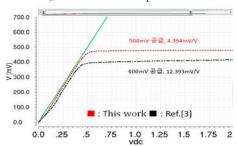

전압 전원  $V_{BB}$ 를 구현하기 위해 Beta-Multiplier 회로를 이용하여 입력 전압이 바뀌어도 고정된  $V_{BB}$  전압을 인가할 수 있도록 하였다. 기존 논문 [3]에서는  $V_{BB}$  전압을 400 mV로 정하여 마진을 두었으나 본 논문에서는 Beta-Multiplier의 PVT 특성을 크게 향상시키고  $V_{BB}$  전압을 500 mV로 정하여 효율 향상을 도모하였다. 이는 그림 3-1과 3-2에 나타내었다. 개

선된 Beta-Multiplier의 Sensitivity는 tt,  $27^{\circ}$ 인에서  $V_{DD}$ 가 1V 증가하는 동안 4.394mV만큼 증가하였다.

그림 3-1. Beta-Multiplier 비교표

그림 3-2. Beta-Multiplier의 PVT 특성

그림 4는 설계된 Beta-Multiplier 회로이다.

그림 4. Beta-Multiplier 회로

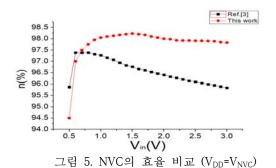

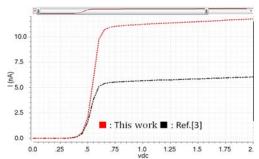

그림 5는 Beta-Multiplier의 공급 전원 전압인  $V_{DD}$ 를 NVC의 출력에 연결한 경우(즉,  $V_{DD}$ = $V_{NVC}$ ), 설계된 NVC의 효율과 기존 논문 [3]의 효율을 비교한 그래프이다. 기존 논문 [3]에 비해 NVC의 전력효율이 더 증가된 것을 확인 할 수 있다. 이는 그림 6에서 보듯이 NVC의 사이즈를 기존보다 줄여서 누설전류를 줄였으며, NVC Body에 인가되는 전압  $V_{BB}$ 를 기존 보다 더 크게 하여문턱전압을 낮추었기 때문이다.

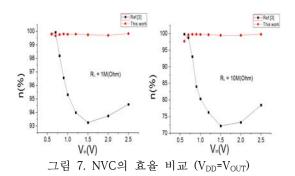

그림 7은 AC-DC 변환기의 출력 직류전압 V<sub>OUT</sub>을 Beta-Multiplier의 V<sub>DD</sub>에 연결한 경우 (즉,  $V_{DD}$ = $V_{OUT}$ )의 효율 비교 그래프이다. 그림에서와 같이 부하저항의 크기가 메가 단위로 커질수록 기존 회로 [3]는 NVC의 효율이 상당히 떨어짐을 알 수 있다. 반면, 본 회로에서는 저항이 커져도 효율이 유지됨을 확인 할 수 있는데 이는 기존 회로에서 [3]는 출력 임피던스가 매우 작기 때문 에 상대적으로 임피던스가 작은 쪽으로 전류가 흐르게 되어 전력 효율이 상당히 떨어졌다.

그림 8은 V<sub>DD</sub>=V<sub>OUT</sub> 일 때 Beta-Multiplier가 Body Bias 전압을 일정하게 인가하는 것을 확인 할 수 있고, 누설전류가 기존 [3]보다 줄어드는 것을 확인 할 수 있다.

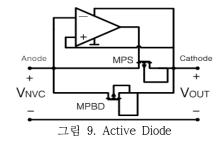

#### 2.3 Active Diode

스위치인 Active Diode는 PMOS MPS와 Comparator 그리고 Comparator Buffer로 구성되 어 있다. 그리고 Active Diode의 안정된 동작 시 작을 보장하기 위해 PMOS Diode인 MPBD를 병 렬로 사용하였다. 또한, 누설전류와 latch-up 현 상을 방지하기 위해 Bulk Regulation(BR)을 사용 하였다. 저전압에서도 동작 가능하도록 하기 위 해 Bulk-Driven technique을 이용한 비교기의 구 조를 그림 10에 나타내었다. 이 때, Comparator 는 Beta-Multiplier를 통해 전류를 공급받는다.

본 논문에서는 Beta-Multiplier의 PVT 특성을 개선하고 더 많은 전류가 흐르게 함으로써(그림 11-1, 11-2), 기존 논문보다 Comparator의 동작 속도와 대역폭을 개선하였다.

그림 8. 입력 전압에 따른  $V_{BB}$  Peak값과  $I_{leak}$ 의 평균값(VDD=VOUT)

그림 10. 비교기 회로

|                     | Ref.[3]      |              |              |             |             |               | This work    |              |               |             |             |               |

|---------------------|--------------|--------------|--------------|-------------|-------------|---------------|--------------|--------------|---------------|-------------|-------------|---------------|

| Specificati<br>on   | 0.7V         |              |              | 1.4V        |             |               | 0.7V         |              |               | 1.4V        |             |               |

|                     | , 22<br>5'08 | tt,<br>27°C  | ff,-<br>20℃  | 55,<br>30°C | tt,<br>27°C | ff, -<br>20°C | ss ,         | tt,<br>27°C  | ff, -<br>20°C | 55,<br>80°C | tt,<br>27°C | ff, ∙<br>20°C |

| Iref Current        | 5.69<br>nA   | 5.47<br>nA   | 5.30<br>nA   | 5.99<br>nA  | 5.80<br>nA  | 5.71<br>nA    | 11.25<br>nA  | 10.82<br>nA  | 10.53<br>nA   | 11.77<br>nA | 11.43<br>nA | 11.21<br>nA   |

| Iref<br>Sensitivity | 5.615<br>%/V | 6.865<br>%/V | 8.284<br>%/V |             | 3,          |               | 5.341<br>%/V | 6.544<br>%/V | 7.823<br>%/V  | à           | T.          | 0.0           |

| 전류 소모               | 17.13<br>nA  | 16.47<br>nA  | 15.96<br>nA  | 17.93<br>nA | 17.40<br>nA | 17.05<br>nA   | 27.28<br>nA  | 26.33<br>nA  | 25.62<br>nA   | 28.17<br>nA | 27.33<br>nA | 26.77<br>nA   |

그림 11-1. Beta-Multiplier(Current) 비교표

그림 11-2. Beta-Multiplier(Current)의 PVT 특성

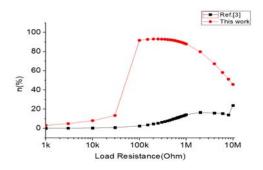

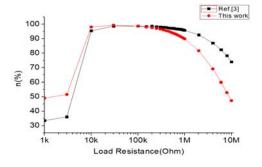

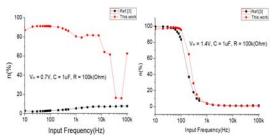

제안된 NVC와 Active Diode를 연결하여 AC-DC 변환기 전체 회로의 효율 특성을 검증하였다. 입력전압의 피크치가 0.7V, 주파수가 40Hz 그리고  $C_{OUT}$ 이 1uF 일 때 부하저항  $R_L$ 에 따른 효율 특성은 그림 12에 보였다. 그림 13은 입력전압의 피크치가 1.4V일 때 이다. 설계된 AC-DC 변환기의 최대 효율은 입력전압 피크치가 0.7V에서  $R_L$ 이  $300K\Omega$  일 때 92.97%이고 1.4V에서  $R_L$ 이  $30K\Omega$  일 때 99.36%이다. 그리고 입력 주파수에 따른 전력 효율은  $C_{OUT}$ 이 1uF 그리고 부하저항  $R_L$  이  $100K\Omega$ 일 때 입력전압의 피크치를 각 각 0.7V와 1.4V로 하여 측정하였고 결과는 그림 14와 같다.

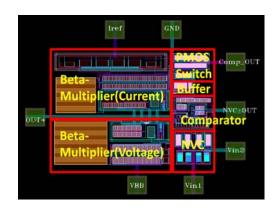

그림 15는 제안 된 회로의 레이아웃으로 크기 는 패드를 포함하여 931 $\mu$ m × 785 $\mu$ m이다.

그림 12. 부하저항에 따른 AC-DC 변환기의 효율 특성(0.7V)

그림 13. 부하저항에 따른 AC-DC 변환기의 효율 특성(1.4V)

그림 14. 입력주파수에 따른 AC-DC 변환기의 효율 특성

그림 15. 레이아웃 도면

### Ⅲ. 결론

본 논문에서는 Beta-Multiplier 구조의 간단한 저전압 기준전압 회로를 이용하여 NVC에 항상고정된 body bias 전압을 공급하여 효율을 향상시키고 저전압에서도 동작 가능한 새로운 AC-DC 변환기를 제안하였다. 제안된 AC-DC 변환기의 최대 효율은 입력전압 피크치가 0.7V 일때, 92.97%이고 1.4V 일때, 99.36%이다. 본 논문에서 제안된 AC-DC 변환기는 저전압 동작이 요구되는 다양한 진동에너지 하베스팅 시스템에 활용될 수 있다.

#### 참고문헌

- [1] A. S. Herbawi, et al, "An Ultra-Low-Power Active AC-DC CMOS Converter For Sub-1V Integrated Energy Harvesting Applications," *IEEE Sensors*, pp.1-4, 2013.

- [2] Z. Yang, et al, "A highly efficient interface circuit for ultra-low-voltage energy harvesting," *IEICE Electronics Express*, vol.10, No.24, pp.1-6, 2013.

- [3] H.-S. Kong. et al., "A Low-voltage Vibrational Energy Harvesting Circuit using a High-performance AC-DC converter" 한국 정보통신학회 추계종합학술대회, pp. 533-536, 2016.