# 넓은 입력 전압 범위에서 작은 트랜스포머 오프셋 전류를 가지는 비대칭 하프-브리지 컨버터

한정규, 김종우, 문건우 한국과학기술원

## A New Asymmetric Half-Bridge Converter with Reduced Transformer Offset Current in Wide Input Voltage Range

Jung-Kyu Han, Jong-Woo Kim, Gun-Woo Moon KAIST

#### **ABSTRACT**

이 논문에서는, 홀드-업 보상 기법을 통해 넓은 입력 범위에서 최적 설계가 가능한 비대칭 하프-브리지 컨버터를 제안한다. 제안된 회로가 갖는 주된 장점은 기존의 회로 동작에 어떠한 변화도 주지 않은 채, 넓은 입력 전압 범위에서도 최적 설계가 가능하게 하는 것이다. 기존의 비대칭 하프-브리지 컨버터는 입력 전압이 가장 낮은 홀드-업 시 설계가 되어, 정상 동작 시 비대칭 동작에 의한 단점을 갖는 반면, 제안 된 컨버터는 홀드-업 시 추가적인 전압 이득을 통해 출력 전압을 제어하기 때문에 홀드-업 동작 시 넓은 입력 전압 범위에 관계없이 컨버터의 최적 설계가 가능하다. 또한 기존의 방법들에 비해, 정상 동작 시에 추가 소자에 의한 손실이 발생하지 않아,전 범위에서 고효율을 달성하였다. 250~410V 입력, 45V/3.3A 출력의 컨버터를 통해 제안 된 회로의 동작을 검증하였다.

#### 1. 서론

비대칭 하프-브리지 컨버터는 적은 소자 개수를 갖고, 모든 스위치의 영전압 스위칭이 가능하다는 특징을 가지고 있어, 낮은 파워에서 많이 쓰이는 토폴로지이다. 하지만 비대칭 하프-브리지 컨버터는 입력 전압이 가장 낮은 홀드-업 상황을 기준으로 설계가 되어, 낮은 턴비를 갖고 정상 동작 시에 작은 시비율로 동작한다는 문제점을 가지고 있다. 이를 해결하기 위해추가 소자를 사용하여, 비대칭 동작으로 인한 문제점들을 해결하기 위한 연구들이 개발되어 왔지만, 환류 전류가 발생하고 여전히 작은 턴 비를 갖는 문제가 있었다. 다른 연구에서는홀드-업 보상 회로를 이용해 비대칭 동작을 해결하고 큰 턴비를 가져 최적 설계가 가능하게 하였지만, 정상 동작 시에 추가 된 소자에 의한 손실이 크게 발생한다. 따라서 본 논문에서는홀드-업 보상 회로를 이용하여 넓은 입력 전압 범위에서추가 되는 소자에 의한 손실 없이 최적 설계가 가능하게 하는 회로를 제안한다.

#### 2. 제안 된 회로의 특징 및 설계

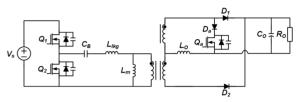

제안 된 회로는 그림 1에서 볼 수 있듯이, 기존의 비대칭 하프-브리지 컨버터 정류단에 스위치와 다이오드를 추가한 구조를 가진다. 정상 동작시에는 추가 스위치와 다이오드가 도통되지 않아 기존의 비대칭 하프-브리지 컨버터와 같은 동작을 하

그림 1 비대칭 하프-브리지 컨버터의 전압 이득 곡선

그림 2 비대칭 하프-브리지 컨버터의 전압 이득 곡선

그림 3 제안 된 회로의 전압 이득 곡선

며, 홀드-업 상황에서 추가 스위치가 켜지면 정류단이 부스트 컨 버터를 병합한 구조가 되어 추가적인 전압이득을 얻을 수 있다.

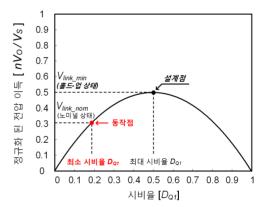

기존의 비대칭 하프브리지 컨버터는 그림 2와 같은 전압 이 득 곡선을 가지기 때문에, 입력전압이 가장 낮은 홀드-업 상황

표 1 설계 값 비교

|                      | 비대칭 하프-브리지 | 제안 된 회로  |

|----------------------|------------|----------|

| 정상 동작 시<br>시비율       | 0.19       | 0.38     |

| 트랜스포머<br>오프셋 전류      | 1.02       | 0.19     |

| 트랜스포머 코어             | PQ2620     | PQ2020   |

| 트랜스포머 턴비             | 40:20:20   | 81:20:20 |

| 정류기 다이오드1<br>전압 스트레스 | 76V        | 75V      |

| 정류기 다이오드2<br>전압 스트레스 | 324V       | 122V     |

| 하프-브리지<br>전류 스트레스    | 1.30       | 0.79     |

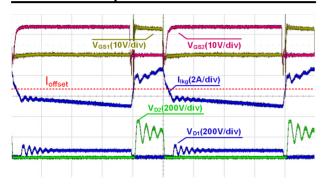

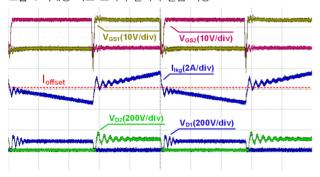

그림 4 비대칭 하프-브리지 컨버터 실험 파형

그림 5 제안 된 회로의 실험 파형

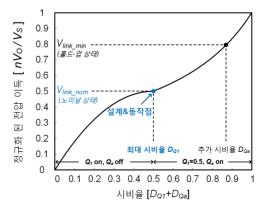

에서 가장 큰 전압이득을 얻도록 설계된다. 하지만 이로 인해, 효율이 중요한 정상 동작 지점에서 비대칭 동작으로 인한 문제를 갖게 된다. 하지만 제안 된 회로의 경우, 그림 3과 같이 홀드-업 구간에서 추가적인 전압 이득을 통해 낮은 입력 전압을 보상해주기 때문에, 홀드-업 구간에 관계없이 컨버터를 최적으로 디자인 할 수 있다.

표 1을 통해 400V 입력, 45V/3.3A 출력에서 제안 된 회로가 기존의 하프-브리지 컨버터에 비해 얼마나 최적 설계가 되는 지 알 수 있다.

#### 3. 실험 결과

실험 파형을 보면, 그림 4에 비해 그림 5에서 오프셋 전류와 1차측 전류 스트레스, 정류기 다이오드 스트레스가 모두 줄어드는 것을 볼 수 있다.

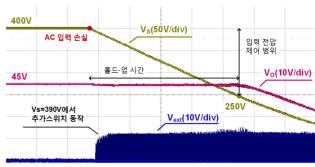

또한 그림 6을 통해서 홀드-업 구간에 추가 전압이득을 통

Thase = 10ms/div

그림 6 홀드-업 구간 동작 파형

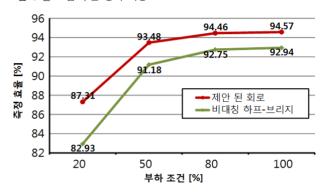

그림 7 효율 비교

해, 입력 전압이 작아지는 상황에서도 출력 전압이 일정하게 제어되고 있는 것을 볼 수 있다.

그림 7을 통해 전 부하 조건에서 제안 된 회로가 기존의 비대칭 하프-브리지 컨버터에 비해 높은 효율을 달성하였다는 것을 증명하였다.

#### 4. 결론

본 논문에서는, 홀드-업 보상 기법을 통해 넓은 입력 범위에서 최적 설계가 가능한 비대칭 하프-브리지 컨버터를 제안하였다. 제안 된 회로는 홀드-업 구간에서 추가 스위치를 통해 출력 전압을 제어하기 때문에, 컨버터가 홀드-업 구간에 상관없이 최적 설계되어 기존의 넓은 입력 전압 범위 설계로 인한 문제점을 모두 제거하였고, 전 부하 영역에서 높은 효율을 달성하였다.

이 논문은 2016년도 정부(미래창조과학부)의 재원으로 한 국연구재단의 지원을 받아 수행된 연구임(No.2010-0028680)

### 참 고 문 헌

- [1] Hong Mao, Jaber Abu-Qaghoug, Shiguo Luo and Issa Batarseh, "Zero-Voltage-Switching Half-Bridge DC-DC Converter With Modified PWM Control Method", IEEE Trans. Power Electron., Vol. 19, pp. 947-958, 2004, Jul.

- [2] Chuan Yao, Xinbo Ruan, "Isolated Buck-Boost DC/DC Converters Suitable for Wide Input- Voltage Range," IEEE Trans.Power Electron, Vol. 26, No. 9, pp. 2599–2613, 2011, Sept.