# 곡률보상 기능을 갖는 0.35μm CMOS 저전압 기준전류/전압 발생회로

박은영·최범관·양희준·윤은정·유종근 인천대학교

0.35µm CMOS Low-Voltage Current/Voltage Reference Circuits with Curvature Compensation

Eun-Young Park, Beom-Kwan Choi, Hee-Jun Yang, Eun-Jung Yoon, and Chong-Gun Yu Incheon National University

E-mail: dmsdudlove06@naver.com

#### 요 약

본 논문에서는 0.35-μm standard CMOS 공정에서 낮은 전력을 소모하면서 낮은 전원전압에서 동작하는 곡률보상 기능을 갖는 기준전류/전압 발생 회로를 제안한다. 제안된 회로는 weak-inversion 영역에서 동작하는 MOS 트랜지스터들을 사용하으로써 1V 이하 전원전압에서 동작할 수 있다. 시뮬레이션 결과는 제안되는 곡률보상 기술을 사용하여 기존의 곡률보상 기능이 없는 BGR 회로들처럼 종 모양이아닌 사인 곡선과 같은 모양을 나타내 작은 TC 값을 보여준다. 제안된 회로들은 모두 0.9V의 전원전압에서 동작한다. 먼저, 기준전압 발생 회로는 176nW 전력을 소모하며, 온도 계수는 26.4ppm/℃이다. 기준전류 발생 회로는 194.3nW 전력을 소모하며, 온도 계수는 13.3ppm/℃이다.

#### **ABSTRACT**

This paper presents curvature-compensated reference circuits operating under low-voltage condition and achieving low-power consumption with  $0.35\mbox{-}\mu m$  standard CMOS process. The proposed circuit can operate under less than 1-V supply voltage by using MOS transistors operating in weak-inversion region. The simulation results shows a low temperature coefficient by using the proposed curvature compensation technique. It generates a graph-shape temperature characteristic that looks like a sine curve, not a bell-shape characteristic presented in other published BGRs without curvature compensation. The proposed circuits operate with 0.9-V supply voltage. First, the voltage reference circuit consumes 176nW power and the temperature coefficient is 26.4ppm/°C. The current reference circuit is designed to operate with 194.3nW power consumption and 13.3ppm/°C temperature coefficient.

#### 키워드 Bandgap reference, low-voltage, low-power, TC, curvature compensation, weak-inversion

#### I. 서 론

BGR 회로는 공정, 전원전압 그리고 온도 변화에 무관한 기준전압이나 기준전류를 발생함으로써 아날로그 시스템과 디지털 시스템에서 기준전압이나 전류를 발생하는 전압원 또는 전류원으로 사용되고 있다. 아날로그 시스템과 디지털의 전원전압은 공정 기술의 발달로 점점 낮아지고 있는 추세이다. 그러므로 이 시스템에 사용되는 밴드갭 회로는 저전압에서 동작할 필요가있다[1].

BGR 회로에서 가장 중요한 디자인 파라미터는 온도 계수(TC)이다. 대부분의 BGR 회로에서는 BJT를 이용하는데, BJT의 베이스-이미터 전압의

이 논문은 IDEC 지원에 의해서 일부 수행되었음.

온도 의존성 특성에 의해 온도에 대해 비선형적 전류가 발생한다. BJT를 사용하는 BGR 회로에서는 이 비선형적인 특성과 MOS 트랜지스터들의 소스-게이트 전압이 가지는 온도에 대한 비선형적 특성을 이용하여 보상시키는 곡률보상 기술(curvature compensation)을 적용해 향상된 TC를얻는다[1]-[3]. 하지만 곡률보상 기능을 가지는 BGR 회로들의 BJT와 MOS 트랜지스터들의 다양한 파라미터들은 각각 다른 특성을 가지고 있어 매칭 시키는데 어려움이 있다. 또한 BJT를 사용하는 경우 저전압 동작에 제한적일 수밖에 없다. 본 논문에서는 BJT 없이 MOS 트랜지스터들만을 이용하여 곡률보상 기능을 갖는 기준전압/전류 발생 회로를 제안한다. 제안되는 회로들의 모든 MOS 트랜지스터들은 weak-inversion 영역

즉, sub-threshold ( $V_{gs} < V_{TH}$ ) 영역의 saturation ( $V_{ds} \gg V_{T}$ ,  $V_{T} \simeq 25 m \, V$ )에서 동작한다. weak-inversion 영역에서 동작할 수 있는 MOS 트랜지스터의 특성 때문에 MOS 트랜지스터들만 이용한 회로들은 큰 전원전압 없이 낮은 전압으로도 동작할 수 있다[4]-[5]. 그러므로 큰 전원전압을 필요로 하는 BJT 없이 MOS 트랜지스터들만 이용한 본 논문에 제안되는 회로들은 1V 이하의 0.9V라는 낮은 전원전압에서 동작한다. 낮은 전원전압에서 동작하므로 현재 기기들의 소모되는 전력이 점점 낮아지고 있는 추세에 맞게소모되는 전력 또한 낮다.

## Ⅱ.본 론

### 2.1 곡률보상 기능을 갖는 기준전압 발생 원리

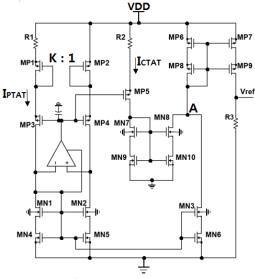

그림 1은 설계한 기준전압 발생 회로를 제시한다. 제시된 기준전압 발생 회로는 R1, MP1 그리고 MP2에 의해 절대온도에 비례하는 전류(PTAT 전류)가 발생된다. PTAT 전류의 식은 다음과 같다.

$$I_{PTAT} = \frac{V_{sg2} - V_{sg1}}{R_1} = \frac{n V_T \ln(K)}{R_1}$$

(1)

여기서 K는 MP1과 MP2의 트랜지스터 사이즈 비이다.

R2 에 흐르는 절대온도에 반비례하는 전류 (CTAT 전류)는 MP2, MP4, MP5 그리고 R2 에 의해 발생되는데 그 식은 다음과 같다.

$$V_{sg2} + V_{sg4} = V_{sg5} + I_{CTAT}R_2$$

(2)

$$I_{CTAT} = \frac{V_{sg2} + V_{NL}}{R_2} \tag{3}$$

$V_{NL}$ 은 MOS 트랜지스터 MP4 와 MP5 의 소스-게이트 전압차이다. 낮은 전원전압에서 기준전압 발생 회로가 동작하기 위해 사용되는 모든 MOS 트랜지스터들은 weak-inversion 에서 동작한다. 그에 대한 전류 식은 다음과 같다.

$$I_D = \mu C_{o\chi} V_T^2 \frac{W}{L} exp \left( \frac{V_{GS} - V_{TH}}{n V_T} \right)$$

(4)

식 (4)는 weak-inversion 영역에서 동작하는 MOS 트랜지스터들의 게이트-소스 전압이 온도에 비선형적인 특성을 가진다는 것을 나타낸다. 이를 통해 MP4 와 MP5 의 소스-게이트 전압은 온도에 비선형적인 전압이고, 두 전압 차인  $V_{NL}$  또한 온도에 비선형적이라는 것을 알 수 있다. 이 비선형적인 전압 때문에 곡률보상 기술이 회로에 적용된다. 온도에 비선형적인  $V_{NL}$ 과 온도에 따라 비선형적인 특성을 갖는 MP2 의 소스-게이트 전압이 상쇄되어 TC 에 영향을 미치는 비선형적인 성분을 없어게 되면 선형적으로 온도에 반비례하는 전류( $I_{CTAT}$ )가 발생되는 것이다. 이렇게 발생된 두 전류, PTAT 전류와 CTAT 전류는 A 노

드에서 합쳐지고, R3에 합쳐진 전류가 흐르게 되면서 기준전압이 발생한다. 기준전압의 식은 다음과 간다

$V_{ref} = R_3 (nI_{PTAT} + mI_{CTAT})$  (5) n과 m은 상수이다. 이 상수 값들은 MOS 트랜지스터 미러들의 사이즈 비 때문에 나타난다.

그림 1. 기준 전압 발생 회로

## 2.2 곡률보상 기능을 갖는 기준전압 발생 회로

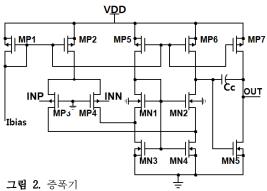

2.1절의 그림 1에 제시된 기준전압 회로에서 필요한 증폭기는 그림 2에 제시되어 있다. 표 1은 그 회로에 대한 성능 결과표이다. 증폭기는 PTAT 전류를 발생시키는 단의 하단 쪽에 양쪽 두 노드의 전압을 같게 해줌으로써 양쪽에 흐르는 전류를 같게 만들어 정확도를 높이는데 사용된다. 증폭기는 낮은 전원전압에서 동작하는 기준전압 발생 회로 안에서 제대로 동작되기 위해 bulk-driven 기법을 사용하여 입력 단 MOS 트랜지스터들의 문턱 전압을 낮춰주었고, 필요한 이득을 얻기 위해 이단(Two stage)으로 설계하였다.

제안된 기준전압 발생 회로는 sub-threshold 영역에서 동작하는 MOS 트랜지스터를 사용하기때문에 channel length modulation 효과가 발생한다[1]. 이를 줄이기 위해 모든 MOS 트랜지스터 미러들은 composite 트랜지스터들을 사용하였다

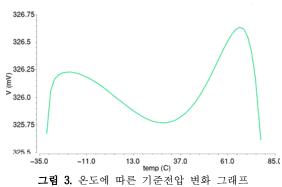

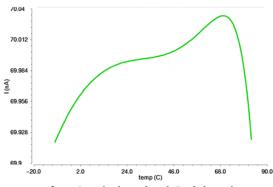

그림 3과 표 2는 그림 1에서 제시된 회로의 시뮬레이션 결과이다. 그림 3을 보면 기존에 다른 BGR 회로들처럼 종 모양이 아닌 두 개의 curve 모양을 나타내고 있다. 이는 개선된 TC와 밀접한 관련이 있다. 표 2 결과표를 보면 제안된 기준전압 발생 회로는 -30~75℃의 온도범위에서 온도 계수 26.4ppm/℃를 가지는 것을 보여준다.이는 참고논문[1]의 온도 계수 53.1ppm/℃와 비교했을 때, 제안된 회로의 온도 계수가 더 낮은 것을 볼 수 있다.

또한 sub-threshold 영역에서 동작하는 MOS 트

랜지스터들만 사용했기 때문에 BJT를 사용한 참고논문[1]의 소모되는 전력 580nw 보다 낮은 176nW 전력을 소모하였다.

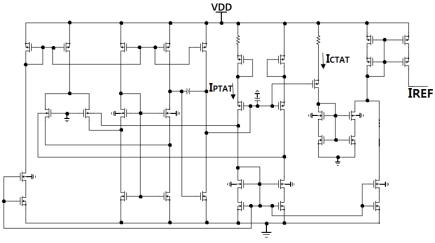

# 2.3 곡률보상 기능을 갖는 기준전류 발생 회로

이 절은 앞서 제안한 기준전압 발생 회로에서 저항 R3를 제거하고 저항 및 MOS 트랜지스터들의 사이즈를 조정하여 낮은 TC를 가지는 기준전류 발생 회로를 제안한다. 동작되는 원리는 제안한 기준전압 발생 회로와 같다. 그림 4에 그 회로도가 제시되어 있고, 그림 5와 표 3은 그에 대한 시뮬레이션 결과이다. 표 3을 보다시피 온도범위 -10~80℃에서 온도계수는 13.3ppm/℃이고, 194.3nW의 낮은 전력을 소모한다. 그림 6은 기

표 1. 증폭기 성능 결과표

| Process                  | 0.35um CMOS  |             |             |

|--------------------------|--------------|-------------|-------------|

| VDD (V)                  | 0.6          |             |             |

| Ibias (nA)               | 13           |             |             |

| Condition                | Worst        | Typical     | Best        |

| Gain (dB)                | 57.9         | 75.9        | 70.8        |

| Phase margin (°)         | 68.0         | 66.3        | 64.1        |

| UGF (kHz)                | 1.2          | 1.5         | 1.9         |

| Current consumption (nA) | 53.7         | 53.2        | 52.4        |

| ICMR (V)                 | 0 ~ 0.6      | 0 ~ 0.6     | 0 ~ 0.6     |

| CMRR (dB)                | 97.1         | 97.2        | 100.0       |

| PSRR+/- (dB)             | 71.73 / 56.4 | 78.0 / 71.3 | 77.4 / 76.9 |

| Offset (uV)              | 76           | 12.         | 25          |

표 2. 기준전압 발생 회로 결과표

|                        | Proposed    | 참고 논문 [1] |

|------------------------|-------------|-----------|

| Process                | 0.35um CMOS | 90nm CMOS |

| VDDmin                 | 680 mV      | 1.15 V    |

| VREF (mV)              | 325.8       | 720       |

| Power consumption (nW) | 176 @0.9V   | 580 @1.2V |

| VDD sensitivity (%)    | 0.73        | 0.35      |

| Temperature Range(℃)   | -30 ~ 75    | 0 ~ 100   |

| TC (ppm/℃)             | 26.4        | 53.1      |

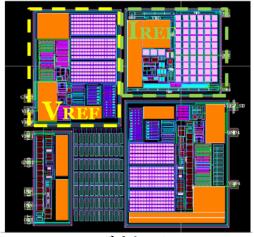

준전압 회로(VREF)와 기준전류 회로(IREF)의 layout을 보여준다. 기준전압 발생 회로와 기준 전류 발생 회로의 layout 크기는 각각  $1m\ x$  1.1m,  $1m\ x$  0.9m이다.

표 3. 기준전류 발생 회로 결과표

| Process                | 0.35um CMOS |  |

|------------------------|-------------|--|

| VDDmin                 | 740 mV      |  |

| IREF (nA)              | 70.0        |  |

| Power consumption (nW) | 194.3 @0.9V |  |

| VDD sensitivity (%)    | 1.09        |  |

| Temperature Range (℃)  | -10 ~ 80    |  |

| TC (ppm/°C)            | 13.3        |  |

그림 4. 기준전류 발생 회로

그림 5. 온도에 따른 기준전류 변화 그래프

그림 6. Layout

# Ⅲ. 결 론

본 논문에서 제안된 회로들은 BJT 대신 sub-threshold 영역에서 동작하는 MOS 트랜지스터들만 사용함으로써, BJT를 사용한 참고논문[1]의 전원전압인 1.2V보다 낮은 0.9V에서 회로가동작 가능했다. 이로써 소모되는 전력을 낮출 수있었으며 회로에 곡률보상 기능을 적용해 개선된 TC를 얻었다. 하지만 개선된 TC를 얻기 위해서는 MOS 트랜지스터의 사이즈를 키워야 했고결과적으로 칩의 사이즈도 커지게 되었다 또한 MOS 트랜지스터들만 사용하는 것은 게이트에서누설되는 전류를 발생시켜 전원전압에 따른 기준전압 및 전류의 변화, 즉 VDD sensitivity는 조금 나빠졌다.

#### 참고문헌

[1] K. K. Lee, T. S. Lande, and P. D. Häfliger, "A Sub- Bandgap Reference Circuit With an Inherent - Curvature Compensation Property," *IEEE T. Circuits and Systems,* vol. 62, no. 1, pp. 1-9 Jan. 2015.

[2] P.Malcovati, F. Maloberti, C. Fiocchi, andM. Pruzzi, "Curvature-compensated BiCMOS bandgap with 1-V supply voltage," *IEEE J. Solid-State Circuits*, vol. 36, no. 7, pp. 1076–1081, Jul. 2001.

[3] Z.-K. Zhou *et al.*, "A 1.6-V 25- 5-curvature-compensated bandgap reference," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 4, pp. 677-684, Apr. 2012.

[4] L. Magnelli, F. Crupi, P. Corsonello, C. Pace, and G. Iannaccone, "A 2.6 nW, 0.45 V temperature-compensated subthreshold CMOS voltage reference," *IEEE J. Solid-State Circuits*, vol. 46, no. 2, pp. 465-474, Feb. 2011.

[5] K. Ueno, T. Hirose, T. Asai, and Y. Amemiya, "A 300 nW, 15, 15 ppm/V CMOS voltage reference circuit consisting of subthreshold MOSFETs," *IEEE J. Solid-State Circuits*, vol. 44, no. 7, pp. 2047-2054, Jul. 2009.