# 포인트 터널링과 라인 터널링을 모두 고려한 실리콘 기반의 포켓 터널링 전계효과 트랜지스터의 최적 구조 조건

안태준, 유윤섭\*

한경대학교 전기전자제어공학과

Guide Lines for Optimal Structure of Silicon-based Pocket Tunnel Field Effect

Transistor Considering Point and Line Tunneling

Tae-Jun Ahn, Yun Seop Yu\*

Department of Electrical, Electronic and Control Engineering, Hankyong National University

E-mail: jigo1235@hknu.ac.kr

#### 요 약

이 논문은 라인 터널링과 포인트 터널링을 모두 고려한 포켓 터널링 전계효과 트랜지스터의 여러 가지 구조 및 물질 파라미터에 따른 시뮬레이션 결과를 소개한다. 포켓의 도핑 농도와 두께가 증가할수록 구동전류  $I_m$ 이 증가하고 포켓의 두께와 게이트 절연체의 유전율이 증가할수록 SS(subthreshold swing)가 좋아짐을 보인다. hump 효과는 SS를 나쁘게 하기 때문에 최소화할 수 있도록 최적의 구조를 만들어야 한다.

#### **ABSTRACT**

The structure guide lines of pocket tunnel field effect transistor(TFET) considering Line and Point tunneling are introduced. As the pocket doping concentration or thickness increase, on-current  $I_{on}$  increases. As the pocket thickness or gate insulator increase, subthreshold swing(SS) increases. Optimal structure reducing the hump effects should be proposed in order to enhance SS.

#### 키워드

포켓 터널링 트랜지스터, 라인 터널링, 포인트 터널링, hump effects, subthreshold swing, on-current

# I. 서 론

최근 급격하게 발달한 모바일 기기 및 IoT (internet of things) 분야에서 성능 향상과 함께 소비전력의 감소를 위해 제품의 핵심인 반도체 의 성능 향상 및 소비전력 감소에 대한 연구가 활발히 이루어지고 있다[1]. 지금까지 무어의 법 칙(Moore's Law)에 따라 반도체 집적회로는 소형 화를 거듭하였고, 이에 따라 필요한 구동전압  $(V_{DD})$ 과 전력 소모의 감소 또한 함께 요구되어 왔지만 소형화의 발달에 비해 구동전압은 약 1/5 수준으로 밖에 감소하지 않았다. 이는 기존의 금 속-산화물 반도체 전계효과 트랜지스터(MOSFET) 의 문턱전압 이하 기울기(Subthreshold Swing; SS)가 60mv/dec 이하로 줄어들 수 없는 물리적 인 한계를 가지고 있기 때문이다. 이 같은 한계점 은 구동전압을 감소시키면 누설 전류( $I_{off}$ )가 증가 하는 문제를 초래한다. 따라서 열전자 방출 방식

의 금속-산화물 반도체 전계효과 트랜지스터와는 다른 터널링(Tunneling)을 이용한 터널링 전계효 과 트랜지스터(Tunnel Field-Effect Transistor; TFET)가 개발되었고, 문턱전압 이하 기울기가 60mV/dec 보다 작은 트랜지스터를 사용하여 구 동전압을 더 감소시킬 수 있다[2].

밴드 간 터널링에는 라인 터널링과 포인트 터널링이 있으며, 문턱전압 이하 기울기와 구동 전류 ( $I_m$ )가 더 좋은 라인 터널링을 활용한 실리콘기반의 포켓 구조 터널링 전계효과 트랜지스터의 최적의 구조 조건에 대하여 연구를 진행 한 바가 있다[3]. 포켓 구조 터널링 전계효과 트랜지스터에서는 라인 터널링 뿐만 아니라 포인트 터널링도 함께 일어난다. 하지만 이전의 연구에서는 두가지의 터널링 중 지배적인 라인 터널링만을 고려한 시뮬레이션을 진행하여 최적의 구조 조건을 제시하였다.

본 연구에서는 구동전류와 SS면에서 최적의 구

조 조건을 찾기 위해 두 가지 터널링을 모두 고려한 포켓 구조 터널링 전계효과 트랜지스터의다양한 구조 및 물질 파라미터에 따라서 시뮬레이션한다.

### Ⅱ. 본 론

## 2.1 포켓 구조 터널링 전계효과 트랜지스터

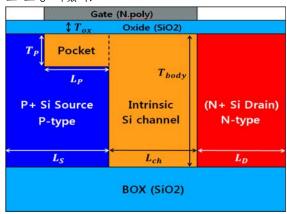

그림 1은 시뮬레이션에 이용한 포켓 구조 터널링 전계효과 트랜지스터의 기본 구조를 나타낸것이다. 구조의 각각의 길이는 게이트 산화막 두께  $T_{ox}=1nm$ , 포켓 두께  $T_{p}=4nm$ , 포켓 길이  $L_{p}=40nm$ , 실리콘 두께  $T_{body}=20nm$ , 채널 길이  $L_{ch}=50nm$ , 소스 길이  $L_{S}=60nm$ , 드레인 길이  $L_{D}=50nm$ 이다. 소스, 채널, 드레인의 도핑농도는 각각  $N_{a}=10^{20}~{\rm cm}^{3}$ ,  $N_{ch}=10^{15}~{\rm cm}^{3}$ ,  $N_{d}=10^{18}~{\rm cm}^{-3}$ 으로 도핑 하였다.

그림 1. 포켓 구조 터널링 전계효과 트랜지스터

## 2.2 시뮬레이션 모델 및 결과

시뮬레이션은 Silvaco사의 ATLAS를 이용하였고 사용된 터널링 모델은 Non-local 모델이며 라인 터널링과 포인트 터널링이 모두 고려되었다. 이동도 모델은 Lombardi CVT, 재결합 모델은 Auger와 Consrh 모델을 사용하였다. 캐리어 특성모델은 Fermi 모델을 사용하였으며, BGN(Band Gap Narrowing) 모델을 사용하였고, 온도는 300k이다[4].

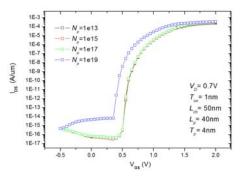

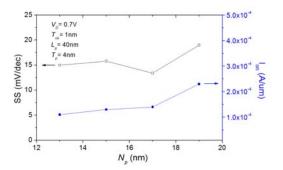

그림 2와 그림 3은 포켓의 도핑 농도(N-type) 의 변화에 따른  $I_{ds}-V_{gs}$  특성 및 SS와  $I_{on}$  특성을 나타내고 있다. 포켓의 도핑 농도가 증가할수록 SS와  $I_{on}$ 는 거의 변화가 없다. 포켓의 도핑 농도  $N_p=10^{19}~\rm cm^{-3}$ 일 때의 경우에 도핑이 낮을 때와 다르게 왼쪽으로 0.2V 정도 쉬프트 하는 것이나타난다.

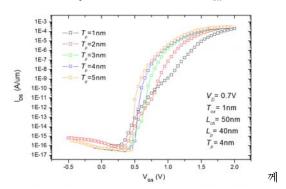

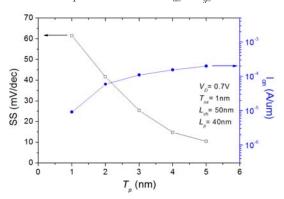

그림 4와 그림 5는 포켓 구조의 두께 변화에 따른  $I_{ds}-V_{gs}$  특성 및 SS와  $I_{on}$  특성을 나타내고 있다. 포켓의 두께가 증가할수록 SS가 감소하고  $I_{on}$ 는 증가하며 문턱 전압이 감소한다. 포켓 구조

그림 2.  $N_{P}$ 의 변화에 따른  $I_{ds}-V_{qs}$  특성

그림 3.  $N_{P}$ 의 변화에 따른 SS와  $I_{om}$  특성

그림 4.  $T_P$ 의 변화에 따른  $I_{ds}-V_{qs}$  특성

그림 5.  $T_P$ 의 변화에 따른 SS와  $I_{on}$  특성

$T_p$ =1, 2nm에서 Hump 효과가 나타나고 있다. Hump 효과는 포켓의 구조상 라인 터널링과 포인트 터널링이 동시에 발생하면서 생기는 현상으로 hump 효과는 SS에 매우 안 좋은 영향을 끼친다. 두께가 증가하면서 hump 효과가 점점 사라지고 있다.

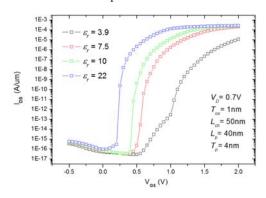

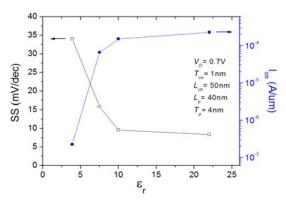

그림 6과 그림 7은 게이트 절연체의 유전율  $\epsilon_r$  변화에 따른  $I_{ds}-V_{gs}$  특성 및 SS와  $I_{on}$  특성을 나타내고 있다. 게이트 절연체의 유전율이 증가할 수록 SS는 감소하고  $I_{on}$ 는 증가하며 문턱전압이 감소한다. 절연체의 유전율  $\epsilon_r$ =3.9(SiO<sub>2</sub>)일 때는 낮은 전압에서 hump 효과가 나타나지만 유전율이 증가하면서 hump 효과가 사라진다.

그림 6.  $\epsilon_r$ 의 변화에 따른  $I_{ds}-V_{gs}$  특성

그림 7.  $\epsilon_r$ 의 변화에 따른 SS와  $I_m$  특성

# Ⅲ. 결 론

본 연구에서는 라인 터널링 만을 고려한 지난 연구와 달리 라인 터널링과 포인트 터널링을 모두 고려한 포켓 구조 터널링 전계효과 트랜지스터의 여러 가지 조건에 대하여 시뮬레이션을 진행하였다. 시뮬레이션 결과에 따라 포켓의 도핑 농도와 포켓의 두께가 증가할수록 더 큰  $I_{on}$ 를 얻을 수 있다. 포켓의 두께와 게이트 절연체의 유전율은 hump 효과로 인해 SS에 많은 영향을 끼친

다. 게이트 절연체가  $SiO_2$ 이고  $T_{ox}$ =1nm인 경우에, 구동 전압에 비해 문턱전압 $(V_{th}$ =1V)이 매우높기 때문에 사용하기 부적절하고 고유전율 물질을 사용하는 것이 적절하다.

위의 시뮬레이션 결과를 고려하여 가장 좋은 SS와  $I_m$  및 문턱 전압을 가지는 포켓 구조 터널링 전계효과 트랜지스터의 최적 구조 조건을 사용하여 더 나은 성능을 가지는 트랜지스터 제조에 활용 할 수 있을 것으로 본다.

#### Acknowledgement

본 연구는 산업통상자원부(프로젝트번호:10054888)와 KSRC 지원 사업인 미래반도체소자 원천기술 개발사업의 연구결과로 수행되었음.

#### 참고문헌

- [1] G. Yeap, "Smart mobile SoCs driving the semiconductor industry: Technology trend, challenges and opportunities," in *IEDM Tech. Dig.*, 2013. pp. 13–23, 2013.

- [2] A. M. Ionescu, H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches," *Nature*, Vol. 479, pp. 329–337, 2011.

- [3] T. J. ahn, *et. al.*, "Structure Guide Lines of Silicon-based Pocket Tunnel Field Effect Transistor," 한국정보통신학회 2016년도 춘계학술대회, pp. 166-168, 2016년 5월.

- [4] SILVACO, int. "ATLAS Users Manual", Santa Clara, CA, 2014.

- [5] S. W. kim, et. al, "Hump Effects of Germanium/Silicon Heterojunction Tunnel Field-Effect Transistors," IEEE Transactions on Electron Devices, vol. 63, Issue:6, pp. 2583-2588, 2016.