# 3상 계통연계형 태양광 시스템의 JET규격을 위한 LVRT 제어

황의선, 최수완, 서진범, 권효상, 조영균, 나병훈, 민준기 (주)다쓰테크 기술연구소

## LVRT Control of Three Phase Gird-connected PV Inverter for JET Standard

Uiseon Hwang, Suwan Choi, Jimbum Seo, Hyosang Kwon, Youngkyun Cho, Byunghun Ra, Joonki Min DASS Tech Co., Ltd. R&D Center

#### **ABSTRACT**

태양광발전시스템이 연계된 전력계통에서 저전압이 발생되면 인버터에서 일정시간 동안 계통과 연계를 유지해야 하는 FRT 기능은 일본의 계통연계 규격에도 포함되어 있다. 일본의 FRT 규격은 3상 혹은 2상 지락에서 일정시간 계통과 연계를 유지하도록 규정하고 있으며, 이러한 상황에서 계통과 연계를 유지하기 위해서는 인버터의 과전류를 막는 것이 중요하다. 본 논문에서는 FRT 상황에서 저전압이 발생되는 시점을 검출함과 동시에 그 전압의 크기를 측정하여 FRT 규격을 만족하는 계통연계 알고리즘을 제안하고 있다.

#### 1. 서론

전 세계적으로 신·재생에너지에 의한 분산전원 시스템의 도입 확대되고 있다. 전력계통에 분산전원 시스템이 대규모로 연계될 경우에 발생하는 계통사고와 이에 따른 분리 동작에 의한 전력품질의 하락의 우려는 점차 커지고 있다. 이에 대한 대책으로 각 국에서는 FRT(Fault Ride Through) 기능을 분산전력시스템에 요구하고 있다.

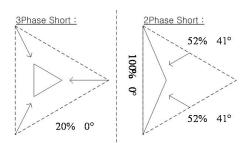

일본전기협회(JEAC)에서도 FRT 규격(JETGR0003 1 4.0)을 지속적으로 검토를 진행하고 있으며 인증규격에도 포함시키고 있다. 그림 1.은 단락사고의 전압벡터를 나타내고 있다. 인버터는 3상 계통전압의 강하 그리고 위상 변동을 포함한 2상 계통전압의 강하되는 상황에서 0.3s 동안 계통과 연계를 유지해야되다.

본 논문에서는 전압 강하 및 전압 복귀시점 그리고 전압의 크기를 검출하여 일본의 FRT 규격을 만족하기 위한 계통연계 알고리즘을 제안하고자 한다.

#### 2. 본 론

#### 2.1 전압 강하 검출 알고리즘

일본의 FRT 조건에서는 전압 강하는  $100\% \sim 20\%$  범위이며, 정상 전압 복귀 시에 150% 이상의 과전류가 발생하지 않음과 동시에 전압 강하 발생 전 전류의 80%까지 0.1s이내, 100%까지 도달하는 시간이 0.5s 이내야 한다고 규정되어 있다. 따라서 계통전압의 강하/복귀 시에 계통연계형 태양광 인버터

그림 1. 단락사고의 전압벡터

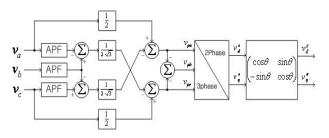

그림 2. 전압 강하 검출 알고리즘의 블록다이어그램

가 계통과 연계를 유지하기 위해서는 계통사고 시점을 검출하여 과전류를 방지해야 한다. 그림 2.는 계통전압의 전압강하 검출 알고리즘의 블록다이어그램이다. 계통전압의 전압 강하는 3상 계통전압의 불평형을 고려한 정상분을 추출하여 d q변환을하도록 하였으며 식 (1)과 같이 나타내어 진다.

$$\begin{bmatrix} v_{pa} \\ v_{pb} \\ v_{pc} \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 1 & a & a^2 \\ a^2 & 1 & a \\ a & a^2 & 1 \end{bmatrix} \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix} = \begin{bmatrix} \frac{1}{2} v_a - \frac{1}{j2\sqrt{2}} \left( v_b - v_c \right) \\ - \left( v_{pa} + V_{pc} \right) \\ \frac{1}{2} v_c - \frac{1}{j2\sqrt{2}} \left( v_a - v_b \right) \end{bmatrix}$$

(1)

식 (1)에서  $v_a,v_b,v_c$ 는 계통전압의 상전압,  $v_{pa},v_{pb},v_{pc}$ 는 계통전압의 정상분이고, 여기서  $a=e^{j\frac{2\pi}{3}}$  이다.

$$\begin{bmatrix} v_d^e \\ v_q^e \end{bmatrix} = \begin{bmatrix} \cos\theta & \sin\theta \\ -\sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} v_d^s \\ v_q^s \end{bmatrix}$$

(2)

식 (2)에서  $v_d^\epsilon$ 의 값은 계통전압의 전압 강하, 및 정상 전압 복귀 시점을 신속하게 검출 할 수 있으며, 과전류를 방지하기 위한 제어도 가능하다.

#### 3. 실험 및 고찰

본 논문에서 제안하는 FRT 계통연계 알고리즘을 적용하여 정격출력 12.4kW의 3 레벨형 인버터를 제작하여 제어동작을 실험을 통해 확인하였다. 본 실험에서 계통전압은 선간 202V/60Hz에서 일본의 FRT 조건으로 실험을 진행하였으며, 전압 강하 시 제안한 알고리즘의 타당성 및 인버터의 출력전류의 과전류 상태 및 제어 여부를 확인하였다.

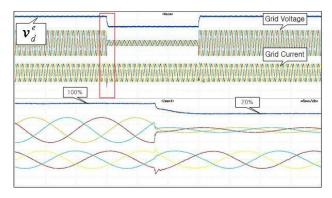

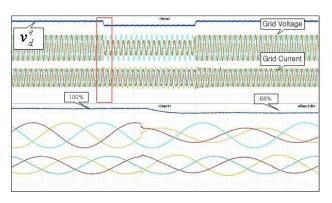

그림 3. 3상 전압 강하(20%, 0°) 발생 시 파형

그림 4. 3상 전압 강하(20%, 0°) 복귀 시 파형

그림 3, 4는 3상 전압이 20%로 전압강하가 발생하여 0.3초 동안 유지한 후 전압이 다시 100% 까지 복귀 하였을 때 d q 변환의  $d = (v_d^e)$ 과 계통전압 그리고 인버터의 출력전류 파형이다. 제안한 알고리즘의 출력인  $v_d^e$ 은 신속하게 계통전압의 강하 및 복귀를 검출하였으며 그 크기를 검출 할 수 있었다. 또한  $v_d^e$ 의 신호를 이용하여 인버터 출력전류의 과전류를 방지할 수 있음을 확인하였다.

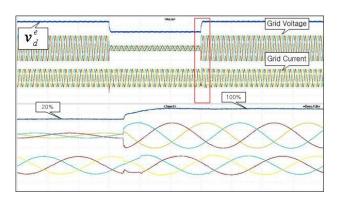

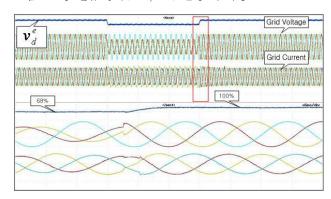

그림 5, 6.은 2상 전압이  $41^{\circ}$ 의 위상변화를 동반하고 52%로 전압강하가 발생하여 0.3초 동안 유지한 후 전압이 다시 100%까지 복귀 하였을 때  $v_d^e$  신호와 계통전압 그리고 인버터의 출력전류 파형이다. 계통이 불평형 전압 강하가 발생하여도 정확하게 강하 및 복귀시점을 알 수 있었으며, 이를 통하여 FRT 조건에서 과전류를 방지하였고 계통연계형 태양광 인버터는 계통과 지속적으로 연계를 하였다.

또한, 계통사고 이후 복전 시 신속하게 유효전력을 출력하기 위해 인버터의 출력전류는 계통사고 이전 전류의 크기를 유지 하였으며 무효전력은 출력하지 않았다.

그림 5. 2상 전압 강하(52%, 41°) 발생 시 파형

그림 6. 2상 전압 강하(52%, 41°) 복귀 시 파형

#### 4. 결론

일본의 FRT 규격 조건은 3상 전압강하와 위상변동을 포함한 2상 전압강하 시에도 계통과 연계운전을 유지해야 된다. 그리고 전압복귀 시에 신속하게 유효전력을 발전함과 동시에 과전류가 발생하지 않아야 한다. 이러한 조건을 만족하기 위해전압강하 또는 전압복귀 시점과 그 크기를 신속하게 측정하는 것이 중요하다. 따라서 본 논문에서는 FRT 규격 조건에서 계통전압의 전압강하 시 신속하게 검출하고 그 크기을 측정하여계통연계형 태양광 인버터의 출력 과전류를 방지하였으며 일본의 FRT 규격 실험을 통해 만족함을 확인하였다.

이 논문은 2014년도 정부(미래창조과학부)의 재원으로 연구개발특구진흥재단의 "연구개발특구육성(특구기술사업화사업)" 지원을 받아 (주)다쓰테크에서 수행된 연구임(2014DD021)

### 참 고 문 헌

- [1] Muhamad Mansor, Nasrudin Abd. Rahim, "Three Phase PWM Switched Autotransformer Voltage Sag Compensator Based on Phase Angle Analysis", Journal of Power Electronics, Vol. 11, No. 6, pp. 897 903, Nov. 2011..

- [2] Y. Silapawicham, Y. KumsuwanCurtis, "An Improvement of Synchronously Rotating Reference Frame Based Voltage Sag Detection for Voltage Sag Compensation Applications under Distorted Grid Voltages", Power Electronics and Drive Systems(PEDS) IEEE, pp. 100 1403, Dec. 2011..