# 계통 외란에 강인한 동기 좌표계 비례 적분 전류 제어기 이득 선정 연구

조현길, 김지찬, 차한주 충남대학교

## A Study of Synchronous Reference Frame PI Current Controller Gain Selection Robust to Grid Disturbance

Hyeungil Jo, Ji Chan Kim, Hanju Cha Chungnam National University

#### **ABSTRACT**

본 논문에서는 동기 좌표계 비례 적분(PI) 전류 제어기의 이 등 산정에 따른 계통 외란 발생 시 제어기의 응답 특성을 연구하였다. PI 전류 제어기의 이득 선정 시 플랜트의 시정수와 적분기 시정수를 같게 설정하는 극점 영점 상쇄 기법을 사용하여 전류 제어 특성을 결정할 수 있다. 그러나 극점 영점 상쇄기법을 통해 이득이 선정된 전류 제어기는 계통에 외란 발생시 제어기 응답 특성이 느려진다. 적분기 시정수를 샘플링 주기를 이용하여 선정한다면 계통 외란에 강인한 특성을 갖게 된다. 제안된 방법은 각각 선정된 적분기 시정수를 가지고 외란에 대한 주파수 응답 특성과 데드 타임이 추가된 계통연계형인버터 시뮬레이션 결과를 비교 분석하여 제안된 적분기 시정수 선정 방법이 외란에 더 강인함을 검증하였다.

## 1. 서론

태양광, 풍력 등 신재생 에너지원을 이용한 분산전원들은 전 력변화 장치를 통하여 계통과 연계되며, 대부분의 장치들은 전 압형 인버터(VSC)를 사용하고 있다. 계통연계형에 사용되는 전류 제어기는 이득 선정 시 적분기 시정수와 플랜트 시정수를 같게 설정하는 극점 영점 상쇄 기법을 통해 이득을 선정할 수 있다.[1] 극점 영점 상쇄 기법을 통해 이득을 선정하면 플랜트 의 특성은 제거되고 전류 제어기의 이득으로만 전류 제어의 특 성을 결정할 수 있다. 그러나 이러한 방법으로 제어기 이득을 선정하면 적분기 시정수가 느려지며, 제어기가 시스템의 파라 미터 값의 변동에 영향을 받고, 외란 발생 시 외란에 강인하지 못하는 단점이 있다. 그에 반해, 적분 시정수 선정 시 샘플링 주기를 이용하면, 극점 영점 상쇄 기법으로 선정된 적분 시정 수에 비하여 적분기 시정수의 크기가 작아지고 대역폭 증가 및 외란에 강인한 제어기 성능을 기대할 수 있다. 본 논문에서는 각각의 제어기 이득 선정에 따른 주파수 응답 특성 결과 및 계 통연계형 인버터 시스템을 모델링 한 시뮬레이션 결과를 비교 분석하여 외란에 강인한 특성을 확인하였다.

#### 2. 제어기 이득 선정

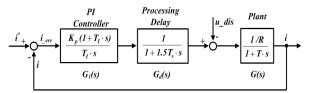

전류 제어 시스템 구조를 동기 좌표계상에서 표현하면 그림 1과 같다.  $k_p$ 는 비례 이득,  $T_s$ 는 샘플링 주기,  $T_l$ 는 적분기 시 정수,  $T_l$ 는 플랜트 시정수,  $T_l$ 는 계통 외란이다.

그림 1 전류 제어 구조

Fig. 1 Block diagram of current control

그림 1에서 PI 전류 제어기는 비례 이득과 적분기 시정수로 표현하였고, 플랜트는 3상 기준 좌표계에서 d q 동기 좌표계로 변환하는 과정에서 생기는 상호 간섭을 보상하면 1차 전달함수로 표현할 수 있다. 실제 디지털 시스템의 지연 성분은샘플링 주기 1.5배로 표현하였다.

$$G_{c} = \frac{\frac{k_{p}/R}{1.5T_{s}T_{I}T}(1+T_{I}s)}{s^{3} + \frac{T+1.5T_{s}}{1.5T_{s}T}s^{2} + \frac{1+k_{p}/R}{1.5T_{s}T}s + \frac{k_{p}/R}{1.5T_{s}T_{I}T}}$$

$$T_{I} = T = L/R$$

(2)

그림 1의 폐루프 전달 함수를 구하면 식(1)로 정리되는데, 만약 적분기 시정수를 식 (2)와 같이 설정하면 극점 영점 상쇄 기법이 가능하므로 그림 1의 폐루프 전달함수는 다시 식 (3)으로 간단하게 표현할 수 있다.

$$G_{c} = \frac{\frac{2k_{p}}{3T_{s}L}}{s^{2} + \frac{2}{3T_{s}}s + \frac{2k_{p}}{3T_{s}L}}$$

(3)

$$k_p = \frac{L}{3T_s} \tag{4}$$

$$T_I = 15T_c \tag{5}$$

식 (3)은 기본적인 2차 시스템과 동일한 형태다. 이때 감쇠비 5를 5=0.707로 설정하면 비례 이득은 식 (4)와 같이 설정할 수 있다. 여기서 식 (2)의 적분 시정수를 그대로 적용하지 않고 식 (5)와 같이 샘플링 주기를 이용하여 적분기 시정수를 설정하면 식 (2)에 비하여 동일한비례 이득을 가진 채 기존의 적분 시정수의 크기보다 작게 되어 계통에 외란 발생 시 강인한 특성을 가지게 되

고, 제어기의 주파수 대역폭이 증가하는 효과를 볼 수 있다.

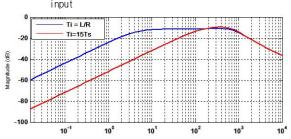

## 3. 제어기 응답 특성 비교

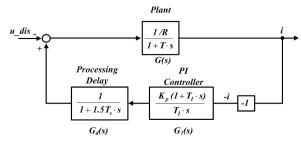

각각의 제어기 이득 선정에 따른 계통의 외란 발생 시 제어기의 주파수 응답 특성을 알아보기 위하여, 그림 1에서 외란에대한 출력 전류의 구조로 보면 그림 1은 그림 2로 다시 표현할수 있다. 그림 3은 식 (4)에서 구한  $k_p$ 와 각각의 적분기 시정수를 그림 2에 적용한 주파수 응답 특성 결과다. 계통에서 발생한 외란은 d q 좌표계에서는 직류 성분과 동일하며, 그림 3을 통해 식 (2)의 적분기 시정수보다 식 (5)의 적분기 시정수를 선정하였을 때 외란의 크기가 훨씬 줄어드는 것을 확인할 수 있다.

그림 2 외란이 입력으로 들어오는 전류 제어 구조

Fig. 2 Current control structure for Voltage disturbance

그림 3 외란 입력 시 제어기 주파수 응답 특성

Fig. 3 Frequency response of current controller by voltage disturbance input

#### 4. 시뮬레이션 결과

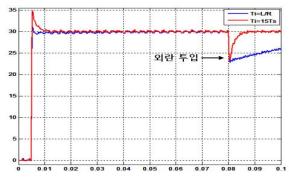

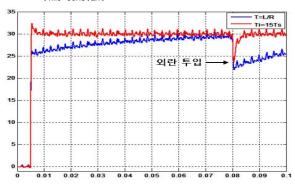

전류 제어기의 성능을 알아보기 위하여 PSIM을 통해 계통 연계형 인버터 시스템을 모델링 하여 시뮬레이션을 진행하였다. 시뮬레이션에서 사용한 파라미터는 표 1과 같다. 시뮬레이션은 전압 외란의 크기를 Vpeak의 20 [%]인 36[V]로 지정하여 5 [msec]에서 전류 지령을 인가 후 80 [msec]에서 계통 외란을 투입하였다. 그림 4는 데드 타임이 생략된 경우의 전류 제어결과다. 데드타임이 없는 이상적인 경우, 초기 지령 값 인가 시식 (2)의 적분기 시정수의 경우가 식 (5)의 적분기 시정수보다오버슈트가 작고, 정착 시간이 빠르다. 그렇지만, 그림 5를 보면 실제 시스템과 같이 데드타임 추가 이후 데드타임의 비선형특성에 의하여 식 (2)의 경우는 26[A]부터 지령 값을 추종하지만, 식 (5)의 경우 데드타임이 없는 경우보다오버슈트가 줄어들며 정착 시간이 빨라진다. 또한 데드 타임의 유/무에 관계없이 외란에 대한 동일한 응답 특성을 가지며 식 (5)의 경우가빠른 시간 안에 정상상태로들어가는 것을 볼 수 있다.

#### 표 1 시뮬레이션 파라미터

Table 1 Parameter values of the simulation

| 필터 인덕턴스 | 1.1[mH]   | 필터 저항  | 30[mΩ] |

|---------|-----------|--------|--------|

| 샘플링 주기  | 100[µsec] | 직류 전압  | 530[V] |

| 용량 지령치  | 8.1[kW]   | 전류 지령치 | 30[A]  |

그림 4. 데드 타임 제거 시 적분기 시정에 선정에 따른 결 시뮬레이션 결과

Fig. 4 Simulation result in omitted dead time by Each PI time constant

그림 5. 데드 타임 추가 시뮬레이션 결과

Fig. 5 Simulation result in added dead time by Each PI time constant

## 5. 결론

본 논문에서는 계통연계형 인버터의 전류 제어기 이득 선정 방법을 연구하였다. 제어기 이득 선정시 극점 영점 상쇄 기법을 보완하기 위하여 샘플링 주기를 이용한 적분기 시정수 선정방법을 제안하였다. 각각의 적분기 시정수를 시스템에 적용하여 보드 선도를 통해 제어기 주파수 응답 특성을 확인하였고 계통연계형 인버터 시스템 시뮬레이션을 통하여 각각의 적분기 시정수를 적용하여 출력 결과를 비교 분석하였다. 보드 선도와시뮬레이션 결과를 통하여 샘플링 주기를 이용하여 선정된 적분기 시정수를 적용한 결과가 외란에 더 강인한 특성을 나타내는 것을 확인하였다.

## 참 고 문 헌

[1] V. Blasko, V. Kaura, "A New Mathmatical Model and Control of a Three Phase AC DC Voltage Source Converter", IEEE Journals & Magazines, Vol. 12, No. 1, pp. 116 121, 1997, January.