# Cascode-GaN과 p-GaN의 동작 특성 및 설계 요소 분석

박상민, 주동명, 김민중, 이병국<sup>†</sup> 성균관대학교 전자전기컴퓨터공학과

# Analysis of Design Elements and Operating Characteristics in Cascode-GaN and p-GaN

Sang Min Park, Dong Myoung Joo, Min Jung Kim, and Byoung Kuk Lee<sup>†</sup> Department of Electrical and Computer Engineering, Sungkyunkwan University

#### **ABSTRACT**

본 논문은 GaN (Gallium Nitride) HEMT (High Electron Mobility Transistor) 소자의 동작 특성과 Normally off형 p GaN 및 cascode GaN 소자의 구현 방식에 따른 차이점을 분석한다. 두 소자의 차이점에 따른 동작 특성을 비교하고 게이트 구동 시 고려되어야 할 설계 요소를 분석한다.

#### 1. 서 론

최근 전자산업의 발전과 IT 기술이 발달하면서 개인 휴대용 단말기부터 상업용, 군사용 전력변환장치에 이르기까지 고출력, 고온 안정성, 고효율 소자가 요구되고 있다. 더불어 기술의 발 달로 인한 전력변환장치의 소비전력 증가와 소형화가 요구됨에 따라 반도체 소자의 기술 개발 필요성이 부각되고 있다.

전력 스위칭 소자는 고출력, 고효율, 고전력밀도 특성을 위해 높은 항복전압, 낮은 온 저항과 고주파 스위칭이 동시에 실현되어야 한다. 현재 40년 가까이 전력시장의 대부분을 차지하고 있는 기존의 Si (silicon) 기반 소자는 Super Junction 구조 등에 따라 높은 항복전압과 온 저항 저감 노력이 계속 되고 있지만 물성의 한계에 도달하여 새로운 화합물 반도체의 개발이 요구되고 있으며, 그 중에 GaN (Gallium Nitride)과 SiC (Silicon Carbide) 기반으로 하는 소자가 각광을 받고 있다<sup>[1]</sup>.

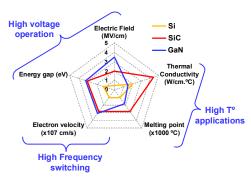

특히, GaN 물질은 그림 1과 같이 3.4 eV의 높은 밴드갭 에너지와  $2.2 \times 10^7 \text{ cm/s}$ 의 큰 전자포화 속도,  $3 \times 10^6 \text{ V/cm}$ 의 높은 항복전계 및 고온안정성  $(700^{\circ}\text{C})$  등의 재료적인 특성 때문에차세대 전력 반도체 소자로 연구가 활발히 이루어지고 있으며 전력변환장치 응용에 큰 장점을 가진다.

그림 1 Si, SiC, GaN 소자들의 특성

Fig. 1 Device characteristics of Si, SiC, GaN

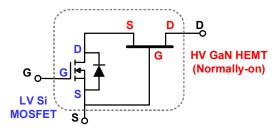

그림 2 Cascode GaN HEMT 소자의 패키지 구조

Fig. 2 Packaging prototype for cascode GaN devices

GaN HEMT (High Electron Mobility Transistor) 소자는 게이트회로 고장 시 전류가 흐르지 않아 안전하고 단일 전원동작이기 때문에 전원회로가 단순하여 소형화가 가능하다는 이유로 Normally off형 E mode (Enhancement Mode) 스위치가선호된다. 이러한 E mode 동작은 구현하는 방식에 따라 Cascode 접속방식과 p type 도핑방식으로 나뉜다. 따라서 본논문에서는 GaN HEMT 소자의 E mode 구현 방식에 따른 p GaN과 Cascode GaN의 동작 특성 및 설계요소를 분석한다.

#### 2. E-mode 동작 특성 및 설계요소

## 2.1 GaN HEMT소자의 Normally off Design

기본적인 GaN 소자는 Schottky Gate 전극 구조로 문턱전압이 약 3.5V를 갖는 Normally on형으로써 off시키려면 음전압이 필요하기 때문에 전원 회로에 사용하기 어렵다. 따라서 D mode (Depletion Mode) GaN HEMT와 저전압 Si MOSFET을 Cascode 접속하여 그림 2처럼 단일 패키지화하여 Normally off를 구현할 수 있다.

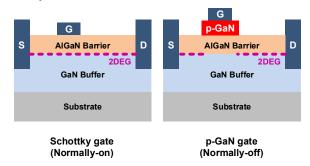

그림 3 Schottky gate와 p-GaN gate 구조의 단면도

Fig. 3 Schematic of a schottky and p-GaN gate

GaN HEMT 소자가 Normally on 동작을 하는 원인은 AlGaN과 GaN사이의 hetero 경계면에 자발 분극에 의해 생기는 2EDG (Two Dimensional Electron Gas : 2차원 전자 가스) 층을 채널층으로 하기 때문이다<sup>[2]</sup>. 따라서 그림 3처럼 p type GaN을 게이트 아래에 만들어 PN 접합의 공핍층으로 게이트를 제어하여 2DEG를 감소시켜 Normally off 동작을 할 수 있다.

### 2.2 게이트 드라이버 설계 요소

GaN HEMT 소자의 고효율, 고속 스위칭 장점을 살리기 위해서 기본적으로 게이트 드라이버와 GaN HEMT 사이의 턴 온오프 경로와 기생 인덕턴스가 최소화되어진 최적 PCB 설계가 필요하다. Cascode GaN과 p GaN HEMT 소자는 구조적특성 때문에 표 1처럼 게이트 드라이버 설계 요소에 차이점이존재한다. 먼저 Cascode GaN HEMT 소자는 기존 양산용 게이트 드라이버 회로를 변경 없이 그대로 사용할 수 있는 장점이 있지만, 식 (1) 과 같이 저내압 Si MOSFET 접속에 따른온 저항이 증가하고 실장 시에 복잡해지는 단점이 있다.

$$V_{DS} = I_{DS} \bullet \left( R_{ds \ GaN} + R_{ds \ Si} \right) \tag{1}$$

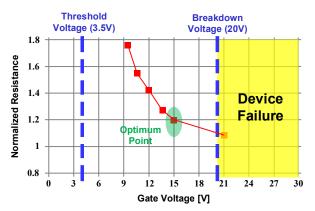

스위칭 시간에 영향을 주는 입력 커패시턴스  $C_{iss}$ 는 GaN HEMT 홑원소 물질 (Simple substance) 의  $C_{iss}$ 와는 무관하게 저내압 Si MOSFET의  $C_{iss}$ 로 정해진다. 반대로 출력 커패시턴 스  $C_{oss}$ 는 Si MOSFET의 의존성은 볼 수 없고 GaN HEMT의  $C_{oss}$ 로 정해진다. 따라서 Half bridge 구조에서는 수학적 분석에 의한 스위칭 속도를 고려한 데드타임 설정이 필요하다<sup>[3]</sup>. 문턱전압은 그림 4의 (a)에서 볼 수 있듯이 저전압 Si MOSFET에 의하여 약 35V로 정해진다. 또한  $V_{gs}$  항복전압은  $\pm 20V$ 를 가지며 구동전압 최적점은 15V이다. Cascode GaN 패키지의 600V급 이상의 HV GaN HEMT 소자는 게이트 문턱전압 22V, 항복전압 35V 정도를 가지기 때문에 저전압 Si MOSFET은  $V_{DS}$  항복전압 30V 소자를 많이 사용한다. 이 값은 저내압으로 낮기 때문에 전압 스트레스에 의하여 소손되어 단락될시 스위치 역할을 못하게 되므로 스너버 회로를 통하여스파이크성 전압을 방지해야 한다<sup>[3]</sup>.

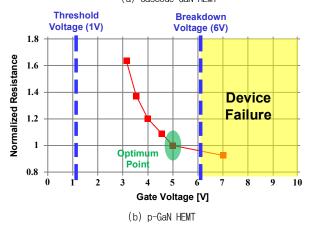

GaN HEMT 소자 하나만으로 Nomally off를 구현 가능한 p GaN은 Cascode GaN HEMT 소자 보다 FOM (Figure of Merit,  $R_{DS(on)}*Q_G$ ) 낮아서 스위치 효율 면에서 유리하다. 하지만 복잡한 공정이 발생하기 때문에 공정상의 비용발생이 Cascode GaN보다 크다는 것이 큰 단점이다. 또한 1V 정도의 매우 낮은 문턱전압 때문에 스파이크 성 Gate Source 구동전 압으로 인한 faulty turn on이 발생 할 수 있다. 그리고  $V_{gs}$  항복전압이  $\pm 6V$ 로 낮고 매우 민감한 게이트 전압 제어가 필요하기 때문에 기존 MOSFET 및 IGBT 절연 게이트 드라이브 회로를 그대로 적용할 수는 없는 단점이 있다. 게다가 온 저항을 낮추기 위해 최대한 Gate Source 구동 전압을 높여야 하므로

표 1 Cascode-GaN과 p-GaN의 동작 특성 Table 1 Driving characteristics of cascode-GaN and p-GaN

| Parameter                         | Cascode-GaN | p-GaN  |

|-----------------------------------|-------------|--------|

| Manufacturer                      | IR          | EPC    |

| Threshold Voltage V <sub>th</sub> | 3.5 [V]     | 1 [V]  |

| Breakdown Voltage $V_{gs\_max}$   | ±20 [V]     | ±6 [V] |

|                                   | 15 [V]      | 5 [V]  |

(a) Cascode-GaN HEMT

그림 4 게이트 전압에 따른 Cascode-GaN과 p-GaN 동작특성 Fig. 4 Operating characteristics of cascode-GaN and p-GaN

제너 다이오드와 같은 클램프 회로가 필요하며 그림 4의 (b)처럼 매우 민감한 범위의 게이트 전압 제어가 요구된다. 따라서 시뮬레이션을 통한 게이트 전압 진동을 예측하고 필요에 따라서 양방향 (Bipolar) 게이트 전압 제어를 통하여 노이즈에 의한 faulty turn on 방지 및 스위칭 속도 향상이 필요하다.

# 3. 결 론

본 논문은 GaN HEMT 소자의 동작 특성과 E mode 구현 방식에 따라 나뉘는 Cascode GaN과 p GaN의 차이점을 분석 하였다. 두 소자의 차이점에 따른 게이트 구동 요소를 비교하 고 장단점을 분석하였다. 가격 및 게이트 드라이버 구현에서는 Cascode GaN이 우위성을 가졌고 전원장치 효율 면에서는 p GaN이 우위를 점하였다.

#### 참 고 문 헌

- [1] Millan, J., "Survey of Wide Bandgap Power Semiconductor Devices," IEEE Trans. Power Electron., vol 29, no. 5, pp. 2155 2163, 2014.

- [2] O. Hilt, A, "Normally off AlGaN/GaN HFET with p type Ga gate and AlGaN buffer," in Proc. 22nd Int. Symp. Power Semicond. Devices ICs, pp. 347 350, Jun 2010.

- [3] Zhenguang Liu, "Characterization and Failure Mode Analysis of Cascode GaN HEMT," Master of Science in Electrical Engineering, Virginia, May 8, 2014.