## Ⅲ-V족 반도체 소자의 Interface Passivation Layer을 위한 원자충 식각

# Atomic Layer Etching of interface Passivation Layer for III-V compound semiconductor devices

윤덕현<sup>a\*</sup>, 김화성<sup>a</sup>, 박진우<sup>a</sup>, 염근영<sup>a,b</sup> <sup>a\*</sup>성균관대학교 신소재공학과(E-mail:pasfinder@hanmail.net), <sup>b</sup>성균관대학교 성균나노과학기술원

초 록: 플라즈마 건식 식각 기술은 반도체 식각공정에서 효과적으로 이용되고 있으며, 반도체 소자의 크기가 줄어듬에 따라 미세하고 정확하게 식각 깊이를 제어할 수 있는 원자층 식각 기술이 개발되었다. 3-5족 반도체 소자의 Interface Passivation Layer 로 이용되는  $Al_2O_3$  와 BeO 의 원자층 식각을 하였으며, 각각의 원자층 식각 조건과 식각 후의 표면 거칠기 변화에 대한 영향을 확인 할 수 있었다.

#### 1. 서론

앞으로 다가올 차세대 Nano-Scale 반도체소자를 위한 미세하고 정교한 플라즈마 식각공정이 요구되고 있다. 기존 플라즈마 반도체 식각공정에서의 Nano-Scale 소자의 식각시 물리적, 화학적 Damage가 동반되기 때문에, Nano-Scale 소자의 식각기술이 절실히 요구되고 있다. 이 문제를 극복 할 수 있는 원자층 식각기술을 이용하여 반도체의 Interface Passivation Layer 물질 식각 기술을 개별하였다.

## 2. 본론

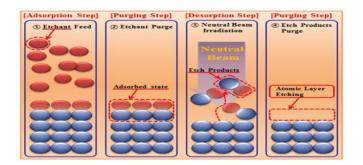

본 연구에서는 플라즈마 중성빔 원자층 식각 장비를 이용하였고, ICP 타입의 안테나에 13.56MHz 의 주파수를 인가하였다. 반도체의 Interface Passivation Layer 물질 중  $Al_2O_3$  와 BeO 샘플을 가지고 원자층 식각 조건을 확립하였다. 또한 샘플의 표면 거칠기 분석을 통하여, 흡착가스의 노출 시간 및 압력에 따른 변화에 대한 결과를 얻을 수 있었다.

Fig. 1. Schematic of atomic layer etching

### 3. 결론

반도체소자의 Interface Passivation Layer로 이용되는  $Al_2O_3$  와 BeO의 원자층 식각을 통하여,  $Al_2O_3$ 의 식각 조건 (1.00A/Cycle)과 BeO의 식각 조건 (0.75A/Cycle)의 결과를 얻을 수 있었다. 또한 AFM 표면 분석을 통하여, 완전히 한 층이 전부 식각되었을 때, 표면 거칠기 향상을 통하여 정확한 원자층 식각이 되었음을 알 수 있었다.

#### 참고문헌

- 1. B.H. Lee, S.C. Song, R. Choi, P. Kirsh, IEEE Trans. Electron Devices 55 (2008) 1.

- 2. I.C. Lee, I. Ok, H.S Kim, F, hud, M. Zhangd, S. I. Park, J.H. Yumd, H. Zhao, ECS Trans. 6 (2007) 3.