# 불평형 및 왜곡된 계통 전압 조건에서의 PLL 알고리즘

이충렬\*, 전태원\*, 이홍희\*, 김흥근\*\*, 노의철\*\*\* 울산대학교\*, 경북대학교\*\*, 부경대학교\*\*\*

# PLL Algorithm Under Unbalanced and Distorted Gird Voltage Conditions

C.R.Lee\*, T.W.Chun\*, H.H.Lee\*, H.G.Kim\*\*, E.C.Nho\*\*\*

Ulsan University\*, Kyungpook University\*\*, Pukyoung University\*\*\*

## **ABSTRACT**

본 논문에서는 계통 전압이 불평형 및 왜곡되었을 경우에 정확한 위상각을 검출 할 수 있는 DSOGI QSG(dual second order generalized integrator quadrature signal generation)를 이용한 PLL (phase locked loop) 방법을 제안한다. 제안된 PLL 방법은 기존의 DSOGI PLL 방법과 비교하기 위해, 전압에 불평형 및 왜곡 사고 발생 시 동기각을 검출하는 시뮬레이션을 하였고, 이를 통해 THD가 개선됨을 입증하였다.

#### 1. 서 론

모터 제어 시스템, 무정전 전원 공급 장치(UPS), 유도 가열 전원 장치 등 여러 산업 분야에서 사용하는 PLL기술은 신재생 에너지 분야의 계통 연계 인버터와 계통 전압 간의 동기화를 위해서도 사용된다. 원활한 계통 연계를 위해 계통 전압 크기 와 위상을 정확하게 알 수 있어야 한다.

불평형 및 왜곡된 상태의 계통 전압 조건에서 신속하고 정확하게 계통 전압의 크기와 위상을 추정하는 문제를 해결하기위해 여러 가지 변형된 PLL이 제시되었다. 먼저 전압 불평형시 SRF PLL(synchronous reference frame PLL) 알고리즘을 사용할 경우에는 역상분의 영향으로 인해 기본 주파수의 2배에해당하는 고조파가 발생하여 위상 추정의 어려움이 따른다.

불평형 전압에서 정상분 추출 위해 전역 통과 필터를 사용할 경우 전역 통과 필터의 차단주파수가 정해져 있기 때문에계통의 주파수가 변화 될 경우 전역 통과 필터의 위상 지연이정확하게 이루어지지 않는 문제점이 있다. 이 문제를 해결 하기 위해 정지좌표계에서 2차 적응 필터 특성을 가지는 SOGIPLL (second order generalized integrator) 방법으로 정상분을 추출하는 방법이 제시되었다.[11] [3] 이 SOGI의 출력 특성으로 인하여 고조파 성분이 일부 줄어 들지만 심각한 왜곡 조건에서는 정상분 전압에 고조파 성분이 포함 되어 있기 때문에 계통과 정확한 동기화가 이루어지지 않아 정확한 위상추종이 어렵다. 본 논문에서는 심각한 고조파 왜곡을 가지는 계통 조건에 대하여 비례 공진 제어기를 이용하여 고조파를 줄이는 PLL 알고리즘을 제안하며, 시뮬레이션을 통해 타당성을 검증한다.

# 2. SOGI-PLL

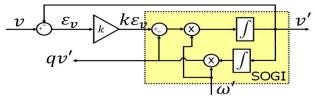

그림 1은 일반적인 SOGI의 구조이다.

그림 1 직교 신호 발생기

Fig. 1 SOGI-Quadrature signal generation

동기 신호와 궤환된 출력 신호의 차이를 이득을 곱해서 SOGI에 입력 된다. 적분기를 통과 한 후 크기를 보상하기 위해  $\omega'$ 를 곱해주게 된다.

SOGI의 전달함수는 다음과 같다.

$$SOGI_{(s)} = \frac{v'_{(s)}}{k\epsilon_{v(s)}} = \frac{w's}{s^2 + w'^2}$$

(1)

여기서 SOGI의 중심 주파수  $\omega'$ 이다.  $\omega=\omega'$  일 경우 출력 신호 v'는 계통 전압과 동기화된 신호가 나오고, 출력 신호 qv'는 동기 신호에 대해 90도 지연된다.

그림 1에서의 적응 필터의 출력 신호에 대한 전달함수는 각 각 다음과 같다.

$$D(s) = \frac{v'_{(s)}}{v_{(s)}} = \frac{kw's}{s^2 + kw's + w'^2}$$

(2)

$$Q(s) = \frac{qv'_{(s)}}{v_{(s)}} = \frac{kw'^2}{s^2 + kw's + w'^2}$$

(3)

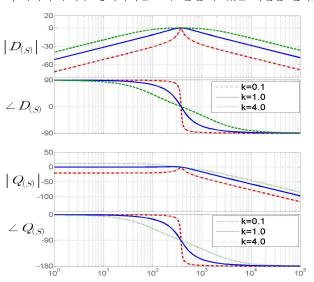

식 (2)와 (3)의 전달함수의 보도선도는 그림 2와 같이 나타 낼 수 있다. 출력 신호 v'은 대역 통과 필터의 특성을 가지며, 출력 신호 qv'는 저역 통과 필터의 특성을 가지게 된다. 두 출력의 대역폭은 이득 k에 의해 결정되며, k=1일 경우  $\omega=\omega'$ 이면 각각의 출력 v'는 입력신호과 같은 크기와 위상을 가지며, qv'는 동일한 크기와 90도의 위상차를 가진다.

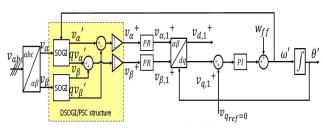

3상의 상전압을 정지좌표계로 변환시켜 2상 전압으로 만들고, 위와 같은 특성을 가지는 SOGI QSG와 2상 전압을 이용해식 (4)와 같이 정상분을 추출 하여 불평형 조건을 보상 할 수있다.

$$\begin{bmatrix} v_{\alpha}^{\ +} \\ v_{\beta}^{\ +} \end{bmatrix} = \begin{bmatrix} v_{\alpha}^{\ -} j v_{\beta} \\ v_{\beta} + j v_{\alpha} \end{bmatrix} = \begin{bmatrix} v_{\alpha}^{\ '} - q v_{\beta}^{\ '} \\ v_{\beta}^{\ '} + q v_{\alpha}^{\ '} \end{bmatrix} \tag{4}$$

SOGI QSG는 중심주파수가 아닌 주파수의 경우에는 크기가 일부 줄어드는 특성이 있지만, 주파수에 따라 크기가 다르게 줄어드는 단점이 있다. 이러한 단점을 보완하기 위해 정상분 추출한 2상 전압을 비례 공진(proportional resonant)제어기에 통과 시켜, 고조파를 상쇄한다.

식 (5)는 비례 공진 제어기의 전달함수이다.

$$G_{PR(s)} = k_p + \frac{2k_i w_{cut}}{s^2 + 2w_{cut}s + w_o^2}$$

(5)

여기서  $w_{cut}$ 은 공진 제어기의 차단주파수,  $w_o$ 는 공진 제어기의 중심주파수이다. 비례 공진 제어기는 중심 주파수를 제외하고, 나머지 주파수 영역에서는 모두 줄일 수 있는 역할을 한다.

그림 2 k값에 따른 SOGI의 보도 선도 Fig. 2 Bode plots with a variation of k

비례 공진 제어기의 출력전압  $v_{\alpha,1}^{\ +},\ v_{\beta,1}^{\ +}$  을  $\mathrm{dq}$ 변환하여 기존의 SRF-PLL을 이용하여 위상을 추정한다.

그림 3 제안된 DSOGI-PLL의 블록 다이어그램 Fig. 3 Block diagram of proposed DSOGI-PLL

# 3. 시뮬레이션 결과

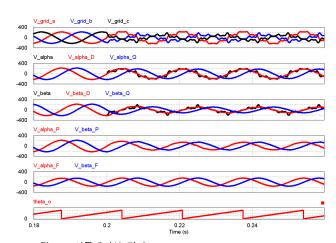

본 논문에서는 PSIM을 이용하여 시뮬레이션을 수행 하였다. 그림 4는 제안된 방법의 시뮬레이션 결과이다. 기준전압은 220~V로 설정하였으며, 불평형 조건에서 B, C상 전압이 50% 감소하고, 고조파 왜곡 조건에서 30~V 크기의 5, 7 고조파와, 15~V 크기의 11, 13고조파로 설정하였다. 두 개의 SOGI QSG의 이득은  $k=\sqrt{2}$ 으로 하였으며, 각각의 비례 공진 제어기의  $k_{p-PR}=0.001$ ,  $k_{i-PR}=1$ 로 설정하였다. 마지막으로 위상을 추정하기 위한 비례 적분 제어기는  $k_p=1$ ,  $k_i=500$ 으로 설정하였다. 표 1은 불평형 전압 영향을 제거 하기 위해 고조파가 포함된 정상분 전압과 비례 공진 제어기 통과 후의 전압을 비교 하였다.

표 1 제안된 방법에서의 전고조파왜율

Table 1 Total harmonic distortion of proposed method

|              | THD     |                    | THD    |                      | THD    |

|--------------|---------|--------------------|--------|----------------------|--------|

| $v_{\alpha}$ | 25.87 % | $v_{\alpha}^{\;+}$ | 3.09 % | $v_{\alpha,1}^{\;+}$ | 0.02 % |

| $v_{eta}$    | 43.12 % | $v_{\beta}^{\;+}$  | 3.09 % | $v_{\beta,1}^{+}$    | 0.02 % |

그림 4 시뮬레이션 결과 Fig. 4 Simulation results

## 4. 결 론

본 논문에서는 DSOGI QSG를 이용한 PLL에 비례 공진 제어기를 추가하는 방법을 제시하였다. A상 전원 전압이 일정하고, B, C상 전압이 50% 감소되는 불평형과 21%의 THD를 가지는 왜곡 전압에서 기존의 DSOGI PLL의 경우에는 2상전압이 약 3%의 THD를 가지고 있지만, 비례 공진 제어기를 통과할 경우 0.02%로 99% 감소 되는 것을 확인하였고, 동기화 시간을 줄이기 위한 추가적인 연구가 필요하다.

#### 참 고 문 헌

- [1] P. Rodriguez, R. Teodorescu, I, Candela, A.V. Timbus, M. Liserre, F. Blaabjerg, "New Positive sequence Voltage Detector for Grid Synchronization of Power Converters under Faulty Grid Conditions," *IEEE Power Electronics Specialists Conference PESC '06, pp. 17, 2006.*

- [2] P. Rodriguez, R. Teodorescu, I, Candela, A.V. Timbus, M. Liserre, F. Blaabjerg, "Multiresonant Frequency Locked Loop for Grid Synchronization of Power Converters Under Distorted Grid Conditions," IEEE Trans. Ind. Electron., vol. 58, no. 1, pp. 127–138, Jan. 2011.

- [3] S. Golestan, M. Monfared, F. D. Freijedo, "Design Oriented Study of Advanced Synchronous Reference Frame Phase Locked Loops," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 765-778, Feb. 2013.