# Analysis of junctionless field effect transistor for transparent electronics

권혁윤, 김민철, 이현우

한국과학기술원 (KAIST) 전기 및 전자공학과, 대전광역시 305-701, 대한민국 e-mail: hykwon885@kaist.ac.kr

# **ABSTRACT**

본 논문에서는 접합을 가지지 않는 Junctionless transistor (JLT)의 두께에 따른 특성 차이 및 기존의 MOSFET과의 특성비교를 EDISON 시뮬레이터를 통해 확인을 하였다. JLT의 두께가 얇아짐에 따라 On/off비율 측면에서 소자의 특성이 향상됨을 확인하였으며, 기존 Inversion mode의 MOSFET과비교하여 단 채널 효과 측면에서도 향상된특성을 확인 할 수 있었다.

## INTRODUCTION

대부분의 MOSFET은 일반적으로 소스-채널-드레인을 구성하는데 있어서 PN접합과 같은 접합면이 존재하게 된다. 하지만 소자의 채널을 줄이는 소형화에 있어서 접합면의 존재는 공정 및 소자의 성능 측면에서 제한적인 요소가 된다.

공정 측면을 보면, NMOS의 경우 소스와 드레인을 구성하는데 있어서 고농도의 Ntype 도핑을 하고 채널 부분은 상대적으로 낮은 농도의 P-type 도핑을 하게 된다. 수 나노미터 단위의 작은 소자의 경우 상당히 작은 면적에 위와 같이 급격한 농도 차이를 가지는 접촉면을 이루어야 하는데 이는 공정상에 큰 문제점으로 작용을 하게 된다. 성능 측면에서 소자의 보면 줄어들면서 발생하는 DIBL(Drain induced lowering). Subthreshold swing(SS)등 의 단 채널 효과를 대표적인 예로 들 수 있다.<sup>[1]</sup>

본 논문에서 다루는 Junctionless transistor (JLT)는 위에서 언급한 문제를 해결해 줄 수 있는 소자 구조이다. 소스-채널-드레인 모두를 같은 종류의 같은

농도로 도핑을 하게 됨으로 인해 공정상에서 큰 이점을 가지게 되고 기존의 소자에 비해 단 채널 효과로 인한 소자 성능 저하도 개선시킬 수 있을 것으로 여겨진다.

JLT 소자의 제작에 있어서 가장 중요한 부분은 얇고 좁은 고농도 도핑 된 반도체 층을 사용해야 한다는 점이다. 얇고 좁은 층을 쓰는 이유는 JLT의 Off 상태에서의 전류가 게이트 전압에 의해 채널에 형성되는 공핍층에 의해 조절되기 때문이다. Off 상태에서 채널로 쓰이는 층이 공핍층으로 완전히 덮여야 누설전류를 줄일 수 있기 때문에 얇고 좁은 반도체 층 일수록 Off 상태에서의 성능은 좋아질 것으로 예상된다. 고농도의 도핑을 하는 이유는 JLT소자의 경우 Accumulation mode 소자에 가까운데 이로 인해 충분하 양의 On current를 얻어내기 위함 이다.[2-3]

본 논문에서는 정해진 조건에서 JLT 소자의 두께에 따른 소자 특성 변화를 시뮬레이션을 통해 확인 해보고자 한다. 또한 일반적인 구조의 MOSFET과의 비교를 DIBL 과 SS등의 값을 추출하여 알아 보았다. 마지막으로는 투명 전자소자로 사용할 수 있는 가능성에 대해 실리콘 박막의 굴절률을 이용하여 두께에 따른 투과율을 통해 알아보았다.

# **METHODS**

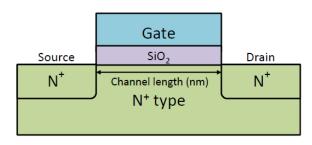

사용한 시뮬레이션은 EDISON 나노물리센터에서 제공하는 Ultra thin body FET소자 성능 및 특성 분석용 SW이다. N-type실리콘 기반의 JLT 소자 구조를 사용하였으며 상온에서 SiO<sub>2</sub> 1nm를 게이트산화막으로 사용하였다. 소자의 도핑 농도는  $10^{19}$  atoms/cm<sup>-3</sup>으로 설정하였으며 Single gate구조를 사용하였고 소스-드레인-채널의

길이는 모두 10 nm로 동일하게 설정을 하고 두께는 2,3,5,7,9,10 nm 로 변화시켜가며 시뮬레이션을 진행하였다. 소자의 대략적인 레이아웃은 Fig 1. 과 같다.

Fig 1. 시뮬레이션에 사용된 소자 구조

JLT 소자와 비교대상이 된 일반적인 MOSFET은 Inversion mode로 Table 1과 같이 소스-드레인은 N-type이며  $10^{19}$  atoms/cm<sup>-3</sup> 의 농도로 도핑을 하였다. 채널은 P-type으로  $10^{15}$  atoms/cm<sup>-3</sup> 의 농도로 도핑된 실리콘을 사용하였고 이 외의 파라미터는 동일한 값을 사용하였다.

Table 1. 시뮬레이션 파라미터

|              | Junctionless                            | Conventional                            |

|--------------|-----------------------------------------|-----------------------------------------|

| Channel type | N-type                                  | P-type                                  |

| Channel      | 10 <sup>19</sup> atoms/cm <sup>-3</sup> | 10 <sup>15</sup> atoms/cm <sup>-3</sup> |

| doping       |                                         |                                         |

| Source/Drain | 10 <sup>19</sup> atoms/cm <sup>-3</sup> | 10 <sup>19</sup> atoms/cm <sup>-3</sup> |

#### **RESULT & DISCUSSION**

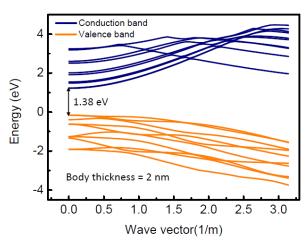

두께 변화에 따른 JLT 소자에 대한 시뮬레이션을 하기 전에 우선적으로 채널로 쓰이는 실리콘의 두께에 따른 에너지 밴드에 대하여 살펴 보았다. 에너지 밴드 역시 EDISON 나노물리 센터에서 제공하는 시뮬레이션 툴을 이용하여 구할 수 있었다. Fig 2.는 300K 에서의 두께 2nm 실리콘의에너지 밴드를 나타낸 그림이다.

Fig 2. Wave vector에 따른 Energy band (Si thickness = 2 nm)

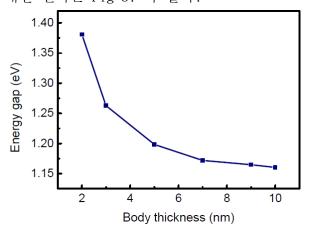

그림에서 알 수 있듯이 실리콘의 두께가 2 nm일 경우 실리콘의 Energy gap은 1.38 eV이다. 이는 일반적으로 알려진 실리콘의 Energy gap인 1.17 (@ T = 300K) 과는 차이가 있는 값이다. 이는 물체의 크기가 작아짐에 따라 그 안의 전자가 느끼는 공간의 크기가 작아지게 되고 이로 인해 불안해진 전자의 에너지 상태가 높아지게 되어 넓은 energy gap을 갖는 현상이 발생하기 때문인데 이러한 현상을 양자 구속 효과 (Quantum confinement effect) 라고 한다.[4-5] 이를 고려하여 실리콘의 두께 변화에 따른 Energy gap 차이를 확인해 보고자 JLT 시뮬레이션에 사용될 채널의 두께 별 시뮬레이션을 진행하였는데 이에 대한 결과는 Fig 3. 과 같다.

Fig 3. 두께 변화에 따른 Energy gap

시뮬레이션 결과, 두께가 감소함에 따라서양자 구속 효과에 의해 Energy gap이늘어나는 것을 확인 할 수 있었다. 좀 더정확한 시뮬레이션을 진행하고자 이후에진행한 JLT 소자의 시뮬레이션은 위의Energy gap 값을 반영하였다.

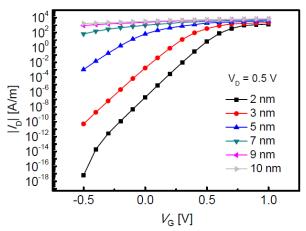

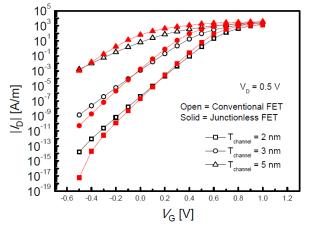

Fig 4. 는 JLT 소자의 채널 두께에 따른 시뮬레이션 결과로 소자의 Transfer curve 가 되겠다. 그래프를 보면, 두께가 감소함에 따라서 On current가 살짝 감소하는 것을 확인 할 수 있는데, Off current는 크게 감소하여 전체적으로 두께가 감소함에 따라소자의 On/off 특성이 좋아짐을 확인 할 수 있었다.

Fig 4. JLT 소자의 두께에 따른 Transfer curve

그 이유로는 채널의 두께가 얇아짐에 따라 Off 상태에서 게이트 전압에 의해 채널에 발생하는 공핍층이 차지하는 영역이 많아지기 때문이다. 채널이 두께에 따른 변화도 수의 캐리어의 영향을 미칠수 있겠으나 On current에서 그 차이가 큰 차이를 보이지 않으므로 공핍층에 의한 Off current 감소가 Off 상태에서 더 큰 영향을 주는 것을 알 수 있다. 따라서 JLT 소자의 특성을 위해서는 최대한 얇은 반도체층을 사용해야 하는 것을 확인 할 수 있었다.

이를 바탕으로 일반적으로 쓰이는 MOSFET과 소자 특성을 비교해 보았다. MOSFET의 구조는 채널로 쓰이는 물질을 JLT와 달리 P-type 실리콘을 사용한

소자구조를 이용하였다. 이에 대한 결과는 Fig 5. 와 Fig 6. 에 나타나 있다.

Fig 5. Conventional FET ♀ JLT ♀ Transfer curve

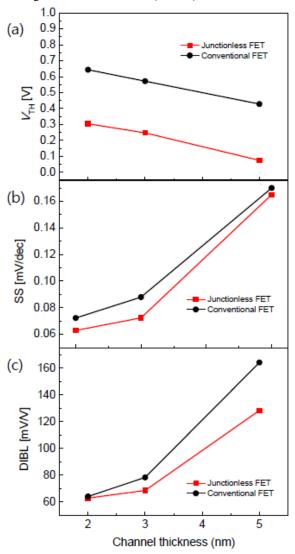

Fig 6. Conventional FET  $\mathfrak{P}$  JLT  $\mathfrak{Q}$  (a) Threshold voltage (b) Subthreshold swing (c) DIBL

Fig 5. 는 Conventional FET와 JLT의 transfer curve 를 나타낸 것인데, 그래프를 보면 JLT의 Off current가 전반적으로 조금씩 낮은 값을 가짐을 확인 할 수 있다. 이 데이터를 바탕으로 JLT가 기존의 MOSFET에 비해 단 채널 효과를 줄이는지 확인해 보고자 몇가지 파라미터를 추출하여 자세히 비교를 해보았다.

Fig 6. 을 보면 (a) 의 경우 JLT의 Vm가 전반적으로 Conventional FET에 비해 낮은 값을 가지며 V™ roll off 는 거의 유사한 비율로 나타남을 볼 수 있다. 그러나 (b)의 SS와 (c)의 DIBL을 보면 전반적으로 JLT가 기존 MOSFET 에서 발생하는 단 채널 효과로 인한 소자 성능 감소를 어느 정도 개선하였음을 확인 할 수 있다. SS의 경우 채널 두께가 2 nm 일때, 이론적인 한계 값인 mV/dec에 가까운 62.89 mV/dec을 기록하였으며 전체적으로 Conventional FET에 비해 나은 값을 가지고 있다. DIBL 의 같이 경우에도 기존의 구조와 채널이 감소하여 소스와 드레인의 거리가 가까워 졌음에도 불구하고 더 나은 특성을 보이는 것을 확인 할 수 있다.

이러한 이유로는 소스-채널-드레인 간에 접합이 발생하지 않는 구조적인 장점으로 인한 것이 가장 크다고 생각 할 수 있다. 소스와 채널, 드레인과 채널 사이에 접합이 발생하는 기존의 MOSFET의 경우 공핍층으로 인해 실제 캐리어가 이동하는 유효 채널길이는 물리적인 채널의 길이보다 짧아지게된다. 하지만 접합이 발생하지 않는 JLT의경우 소스-채널, 드레인-채널 간에 도핑농도차가 발생하지 않아 공핍층이 생성되지않으므로 물리적인 채널 길이와 실제로캐리어가 이동하는 유효 채널 길이가 거의유사하기 때문이다.

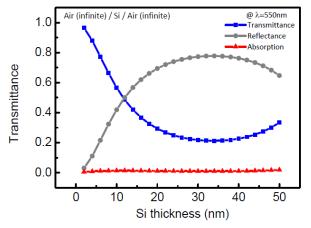

마지막으로 본 논문에서 사용한 JLT 소자가 투명소자로의 가능성이 있는지에 대하여 확인을 해 보았다. Single crystal Si의 굴절률 값을 이용하여 Si 두께에 따른 투과율을 알아 보았는데 이는 SIMOLED 라는 별도의 툴을 사용하여 계산해 보았다. 이에 대한 결과는 Fig 7. 에 나타나 있다.

Fig 7. 실리콘 두께에 따른 투과도

두께는 2 nm 에서 50 nm 까지, 550 nm 파장대로 설정을 하였는데 2 nm에서는 거의 100%에 가까운 투과율을 보이고 있으나두께가 증가함에 따라 급격히 줄어들게 된다. 하지만 시뮬레이션 상에서 5 nm 이하 두께의 JLT 소자가 좋은 특성을 보였는데 이구간에서 70% 이상의 투과율을 보이므로투명전자소자로의 제작도 가능할 것으로보여진다.

### **CONCLUSION**

연구에서는 채널의 두께에 따른 JLT의 특성 변화를 살펴보았으며 채널의 얇아 질수록 소자의 두께가 특성이 향상되었다. 또한 기존의 MOSFET 구조와 비교하여 SS, DIBL에서 더 나은 값을 가져 단 채널 효과 측면에서 JLT 소자의 구조적인 장점으로 인해 개선이 있음을 확인 하였다. 마지막으로는 해당 소자 구조의 두께에서의 투과율을 시뮬레이션을 통해 알아 보았는데 5 nm 이하 일 때, 70% 이상의 투과율을 보여 투명 소자로의 가능성도 확인할 수 있었다.

## **REFERENCES**

- [1] Colinge, J. P., et al. "Junctionless transistors: physics and properties." Semiconductor-On-Insulator Materials for Nanoelectronics Applications. Springer Berlin Heidelberg, (2011)

- [2] Lee, Chi-Woo, et al., Applied Physics Letters 94.5 (2009).

- [3] Colinge, J. P., et al., Solid-State Electronics 65 33-37 (2011).

- [4] Delley, B. et al., *Physical Review B* 47.3 (1993)[5] Öğüt, Serdar et al., *Physical review letters* 79.9 (1997).