# STATCOM용 제어시스템 개발

이종학, 김윤현, 김태형, 권병기 (주)포스코 ICT

# Design of the Control System for STATCOM

Jong Hak Lee, Yun Hyun Kim, Tae Hyeong Kim, Byung Ki Kwon POSCO ICT

#### **ABSTRACT**

본 논문은 당사에서 개발한 5Mvar급 STATCOM(static synchronous compensator)의 제어 시스템에 대해 기술한다. 제작된 5Mvar급 STATCOM은 한 상당 12대의 HBI(H Bridge Inverter)로 구성이 가능하도록 25 Level로 제작되었다. 제안된 제어시스템은 DSP(digital signal processor)를 이용하였으며, 하나의 Main Controller와 다수의 Cell Controller, FPGA 보드 등으로 구성되어 있다. Controller 간의 상호 정보를 교환하기 위해 eCAN 통신을 이용하였고, HBI의 스위칭을 위한 보드는 각각에 연결되어 있으며, Cell Controller보드와는 절연을 위해 광신호로 연결하였다. 본 논문에서는 개발한 제어시스템의 신뢰성을 검증하기 위한 실험을 진행하였다.

### 1. 서 론

당사에서 개발된 STATCOM의 구조는 Cascaded Multilevel Converter이며, 각 상은 독립적인 직류전원을 가지며 H Bridge 구조의 인버터들이 직렬로 구성되어 있다. Cascaded Multilevel 방식은 고압화와 대용량화가 용이하고 출력전압의 고조파 특성이 우수한 장점이 있는 반면, 제어시스템이 복잡하고 제어가어려운 단점을 지니고 있다.[1] 따라서 본 논문에서는 복잡한 제어 시스템을 수십 Mvar급으로 대용량화가 용이하도록 설계하였으며 이를 검증하기 위한 실험을 진행하였다.

### 2. 본 론

### 2.1 제어 시스템 구성

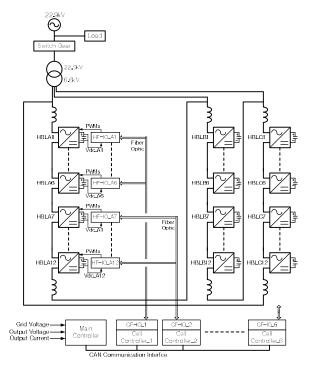

제어 시스템은 기능별로 크게 Main/Cell Controller으로 나눌 수 있으며, Controller 간의 상호 정보를 교환하기 위해 eCAN 통신을 이용하였다. 전체 제어시스템의 구성은 그림 1과 같다.

#### 2.1.1 Main Controller

Main Controller는 1대로 구성되어 있으며 전력계통에 대한 무효전력보상, 계통 전압제어, 불평형보상 등과 같이 STATCOM의 전체 제어를 담당한다.

# 2.1.2 Cell Controller

Cell Controller 1대는 최대 6개의 HBI로 연결이 가능하며,

그림 1 제어시스템 구성도

Cell Controller와 연결되어 있는 HBI의 제어와 보호를 담당한다. Cell Controller는 HBI 6대와 그룹화하여 담당하므로 제어시스템이 간략해지며, 확장이 용이하여 대용량화가 가능하게된다.

Cell Controller에서 HBI를 스위칭하기 위해 PWM 신호를 전송하게 되는데, 이는 그림 1에서와 같이 CF IO B/D (Controller side Fiber Optic Input Output Board)와 HF IO B/D (HBI side Fiber Optic Input Output Board)와 HF IO B/D (HBI side Fiber Optic Input Output Board)로 연결되어 있다. 본 시스템은 고압으로 구성되어 있으므로 HBI측과 Controller측을 절연하여야 한다. CF IO B/D와 HF IO B/D는 Cell Controller와 HBI 간의 절연이 용이하도록 송수신 데이터를 광 또는 전기 신호로 변환하여 전송하였다. CF IO B/D는 Cell Controller와 연결되며 6대의 HF IO B/D와 연결이 가능하도록 구성하였다.

### 2.2 CF-IO / HF-IO B/D 간의 데이터 송수신을 위한 Interface

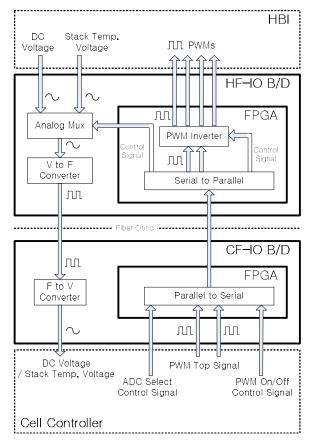

그림 2 CF-IO / HF-IO B/D 간의 데이터 송수신 블록도

그림 2는 HBI 구동을 위한 CF IO / HF IO B/D 간의 데이터 송수신 블록도이다. Cell Controller측과 HBI 측간의 데이터 송수신 데이터는 다음과 같이 정리할 수 있다. Cell Controller측의 전송 데이터는 PWM을 위한 각 스위칭 소자의 Top에 해당하는 PWM 과형, PWM On/Off 제어 신호, DC 전압 및 IGBT Stack 온도 전압 측정을 위한 ADC(Analog to Digital Converter) 선택 제어 신호이다. HBI측의 전송 데이터는 DC 전압 및 IGBT Stack 온도 전압이다.

Cell Controller에서 각 HBI를 스위칭하기 위한 신호와 PWM On/Off 제어 신호, ADC Select 제어 신호가 출력되어 CF IO B/D의 FPGA에 입력된다. FPGA에서는 각 신호들을 직렬로 변환하여 출력한다. 이 직렬신호는 CF IO B/D의 FPGA에서 출력하여 광신호로 변환되고 광케이블을 통해 HF IO B/D로 전송된다. HF IO B/D의 FPGA에서는 입력된 직렬신호의 동기 신호를 검출하여 동기를 맞춘 후 직렬 신호를 병렬신호로 변환하고 HBI 각 Leg Top 신호를 반전하여 Bottom의 신호를 생성한다. 생성된 PWM 신호는 스위칭 On/Off 제어 신호에 의해 출력이 가능하며, 출력된 신호는 HBI 측의 Gating B/D로 전송되어 스위칭 할 수 전송된다.

HBI 측에서는 제어를 위한 DC 전압과 HBI 보호를 위한 IGBT Stack 온도 전압을 Cell Controller로 전송한다. 이는 ADC Select 제어 신호를 이용하여 두 전압을 교변으로 Cell

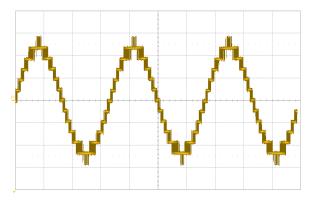

그림 3 출력 선간 전압 (2,000V/div, 5ms/div)

Controller에 입력할 수 있도록 설계하였다. 두 전압은 Analog Mux에 입력되며 ADC Select 제어 신호에 의해 해당 전압이 출력된다. 출력전압은 V to F Converter를 거쳐 주파수형태 변환되고 CF IO B/D로 전송된다. CF IO B/D는 다시 F to V Converter를 거쳐 원신호로(Analog) 복구하어 Cell Controller로 전송한다.

사용된 FPGA Clock은 40MHz이며 이를 입력받아 분할하여 10MHz로 사용하였다. FPGA는 Altera사의 EPM3128ATC100 모델을 사용하였다.

### 2.3 실험 결과

그림 3은 본 논문에서는 제안한 제어 시스템으로 구성된 STATCOM을 검증하기 위해 시스템 동작 중 상당 HBI 6단의 출력전압 3,300Vrms을 측정한 출력 선간전압 파형이며, 출력 선간전압이 13 Level임을 확인할 수 있다.

# 3. 결 론

본 논문은 당사에서 개발한 5Mvar급 STATCOM의 제어시스템에 대해 기술하였다. 또한 Cascaded Multilevel Converter를 구동하기 위한 PWM 신호 발생을 위해 FPGA를 이용한 CF IO / HF IO B/D 간의 데이터 송수신 Interface에 대해 설계 제작하고 검증하였다. 본 논문을 통해 고압, 고용량의 Multilevel Converter 시스템 개발에 적용한다면 제어 시스템을 Compact화 할 수 있음을 기대한다.

본 논문은 각 상당 6대의 HBI로 구성하여 실험이 진행되었으며, 추후 상당 HBI 12대로 구성하여 25 Level Multilevel Converter로 구현하여 검증할 예정이다.

### 참 고 문 헌

[1] Li Gong, Yong Kang, Jingjing Chen, Shuang He, "Phase Shifted Space Vector PWM and On time Correction DC Voltage Balancing Scheme for Cascaded H Bridge STATCOM", 8th International Conference on Power Electronics ECCE, pp. 2741 2748, 2011, May.