# HVDC Valve Operational Test를 위한 합성시험설비 보호 설계

<u>김영우</u>\*, 백승택\*, 이욱화\*, 정용호\* LS 산전\*

## Synthetic Test Circuit protection design for HVDC Valve Operational test

Young Woo Kim\*, Seung Taek Baek\*, Uk Hwa Lee\*, Young Ho Chung\* LS Industrial System\*

#### **ABSTRACT**

신재생 에너지의 비중 확대와 보급이 늘어남에 따라, 국가 간, 도시 간의 송전이 중요한 이슈로 대두 되고 있다. 위와 같 은 요구 조건을 만족시키기 위해서 초고압 직류 송전의 개발이 필요하다. 초고압 직류송전(HVDC)에는 전류형과 전압형으로 나뉘는데. 각 HVDC에서 사용되는 Valve는 실제 운전 전에 여 러 가지 방법으로 검증이 필요하다. 합성 시험회로 설비 (Synthetic Test Circuit = 이하 STC)는 전류형 HVDC에서 사 용되는 주요 전력변환 장치로, Thyristor Valve의 동작을 실제 동작 조건에 맞추어 동작을 시켜, 동작의 신뢰성을 검증하는 시험 설비이다.[1] 본 논문에서는 전류형 HVDC Valve의 Operational Test를 위한 STC의 보호기능에 대해 기술하고 있 다. 합성시험회로는 2상 초퍼와 6 펄스 사이리스터 컨버터를 사용하였고 설계된 보호기능은 PSCAD를 사용하여 검증하였 다. HVDC Valve Operational Test시 합성시험회로 내에서 발 생할 수 있는 사고 상황을 상정하고 그에 따른 보호 기능을 모 의하였다.

#### 1. 서론

HVDC 시스템은 크게 AC 야드, DC 야드, 전력변환기로 나눌수 있는데, 이중 전력변환기는 교류를 직류로 그리고 다시 직류를 교류로 변환하는 장치로 일반적으로 HVDC Valve(Module)이라고 불린다. HVDC Valve를 생산하기 전, 설계된 Valve의 검증을 위해 국제 표준 규정(IEC std.)따라 Type Test를 진행한다.

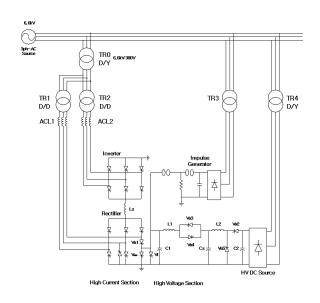

일반적으로 Type Test는 Dielectric Test와 Operational Test로 나뉘는데 Dielectric Test는 절연성능을 시험하기 위한 시험이고, Operational Test는 가혹조건에서 Valve 동작을 시험하기 위한 시험이다. [2][3] Valve Operational Test 중 의도하지 않은 과도현상이 발생할 경우 합성시험설비나 시료에 문제를 야기 시킬 수 있으므로 이런 과도현상에 대해 보호 할 수 있게 합성시험설비 내에 보호동작 회로가 마련이 되어야 한다. 그림 1은 전류형 HVDC Valve를 시험하기 위한 합성 시험설비 단선도를 나타낸 것이다.

## 2. 보호 설계

그림 1 합성시험회로

보호설계는 크게 대전류, 고전압, Thyristor로 나눌 수 있다.

#### 2.1 대전류

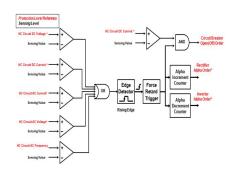

대전류 보호 설계는 그림 2와 같다. 각각의 DC 전압과 전류, AC 전압과 전류 그리고 주파수를 센싱 받아서, 과도현상이 발생 할 경우, 차단기를 동작시켜 대전류 회로의 입력 전압을 차단한다. 또한 점호각과 소호각을 미리 지정된 값으로 지령한다

그림 2 대전류 보호 설계

#### 2.2 고전압

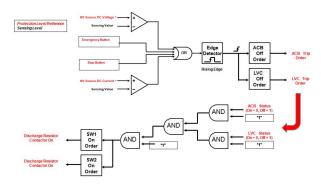

그림 3 고전압 보호 설계

고전압 보호 설계는 DC 전압과 전류를 센싱 받아 이상이 있을시 차단기와 방전 스위치가 동작을 하게 된다. 또한 작업자 안전 및 비상상황을 고려하여 Emergency 버튼과 STOP 버튼이 동작하게 되면 보호 동작을 하게 된다. 그림 3은 고전압보호 설계를 나타낸다.

#### 2.3 Thyristor

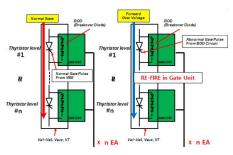

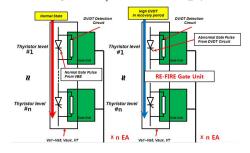

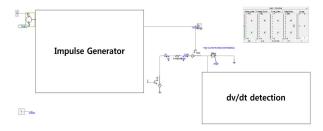

Thyristor 보호설계는 크게 Forward Over Voltage 보호와 역회복 구간에서의 dv/dt에 대한 보호로 나눌 수 있다. Forward Over Voltage 보호는 BOD(BreakOver Diode) Level 에 맞게 설정하여 설계한다. 역회복 구간에 dv/dt 보호는 dv/dt 감지 회로를 이용하여 역회복 구간에서 dv/dt가 감지 될 경우 재점호를 하여 Thyristor를 보호 할수 있게 설계한다.

그림 4 1 Thyristor BOD 보호설계

그림 4 2 Thyristor dv/dt 보호 설계

#### 2.4 시뮬레이션

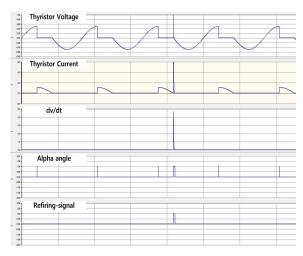

그림 5는 PSCAD를 이용한 dv/dt 보호 동작 회로도를 나타 낸 것이다. 그림 6은 역회복 구간에서 Impules Voltage가 인가 되었을 때 Thyristor를 보호하기 위해 Refiring을 하는 동작을

그림 5 dv/dt 보호 동작 회로도

그림 6 dv/dt 보호 동작 파형

나타내고 있다.

## 3. 결론

본 논문에서는 HVDC Valve Operational Test 중과도 현상으로부터 합성시험설비 및 시료를 보호하기 위한 보호 설계를 기술하였다. 과도현상으로부터 합성시험설비 및 시료를 보호하기 위한 운전모드가 필요하며, 설비보호는 설비사양에 따라 동작레벨과 시간이 계산되어 적용되어야 올바르게 설비를보호할 수 있다.

#### 참 고 문 헌

- [1] 권준범, "HVDC Valve Operational Test를 위한 개선된 합성시험회로", 전력전자학회, 전력전자학회 2013년 하계학술대회 논문집

- [2] "DC 50kV급 HVDC Valve 개발", 전력전자학회, 전력전자 학회 2012년도 전력전자학술대회 논문집 2012.7, page(s):303 304

- [3] 황호윤, "HVDC시스템의 밸브 측 사고감지를 위한 보호요 소 시뮬레이션", 전력전자학회, 전력전자학회 2012년도 추 계학술대회 논문집, 2012.11, page(s):235 236.