## 두 개의 독립적인 하프-브리지 구조의 DC-DC컨버터의 해석에 관한 연구

이아라, 정광순, 홍성수 국민대학교 전력전자 연구소

# A Study on the DC-DC Converter Analysis of Two Independent Half-Bridge Structure

Ah Ra Lee, Kwang Soon Jung, Sung Soo Hong Kookmin University Power Electronic Center

#### **ABSTRACT**

최근에 독립적인 하프 브리지 구조를 가진 DC DC컨버터가 제안되었다. 제안된 컨버터는 두 개의 트랜스포머를 가지고 독립적인 하프 브리지 구조의 형태로 구성되었고, 4개의 스위치는 기존의 위상천이 풀 브리지 컨버터의 스위칭 시퀀스와 동일하게 동작한다. 또한, 지상 레그 스위치에 관계하는 트랜스포머의 자화인덕턴스를 작게 하여 지상 레그 스위치의 영전압 스위칭(ZVS)을 용이하게 하는 것이 특징이다. 그러나, 영전압 스위칭을 위한 자화인덕턴스 설계에 대한 해석이 제시되지 않고 있다. 따라서, 본 논문에서는 제안된 컨버터의 정확한 모드해석과 지상 레그 스위치의 영전압 스위칭을 위한 설계 가이드를 제시한다.

### 1. 서 론

최근 큰 출력전류를 요구하는 부하장치가 많이 요구됨에 따라 대용량 전력변환회로에 적합한 위상천이 풀 브리지 컨버터가 주로 사용되고 있다. 이 컨버터는 스위칭 손실이 적고 EMI특성이 좋다는 장점을 갖는다. 그러나 지상 레그 스위치의 영전압 스위칭의 동작 범위의 제한, 환류 전류로 인한 도통 손실, 2차 측 정류 스위치의 기생 커패시턴스와 누설인덕턴스에 의한 전압 공진 스파이크가 생긴다는 단점이 있다.[1]

한편, 이러한 문제점 해결을 위해 많은 연구가 진행되어왔다. 그 중 보조 인덕터를 추가하여 지상 레그 스위치의 영전압스위칭 동작 범위를 늘리는 방법이 있었지만 이는 유효 시비율을 감소시키는 단점이 있었다. 따라서, 지상레그의 영전압 스위칭 만족을 위해 그림 1과 같이 중용량급에 적합한 2개의 독립적인 하프 브리지 컨버터를 사용한 회로가 제안되었다. 이회로는 Two Transformer구조를 사용하여 유효 시비율의 감소없이 영전압 스위칭이 용이하다는 장점이 있었다. 그러나, 영전압 스위칭을 가능하게 하는 정확한 설계와 해석이 없다. 또한, 1차 측의  $C_1$ 과  $C_2$ 에 각각 입력전압의 절반이 인가되므로  $C_2$ 가 제거되어도 기존과 같은 동작을 하게 된다. 따라서  $C_2$ 를 없앤 회로에 대하여 정확한 모드별 동작과 영전압 스위칭 범위를 결정하는 자화인덕턴스의 설계 가이드를 제시한다.

그림 1. 두 개의 독립적 하프-브릿지 구조의 DC-DC 컨버터

## 2. 제안회로의 특징 및 모드별 동작

### 2.1 제안회로의 특징

그림 2는 제안 회로이며 1차 측의 4개의 스위치는 기존의 위상천이 풀 브리지 컨버터와 같은 동작을 하고, 유효 시비율에 의해 전압이득이 결정된다. 트랜스포머1은 트랜스포머2에비해 자화인덕턴스와 누설인덕턴스가 작은 값을 갖는다. 그리고, 2차 측은 전류 배율기 구조를 사용하여 출력 인덕터에 흐르는 전류를 반분하여 인덕터의 도통손실을 저감하고 열을 분산시킨다. 또한, 환류구간에서의 도통손실을 줄이기 위해 SR(Synchronous Rectifier) 스위치를 사용하였고, 공진 전압을 없애기 위한 RCD 스너버 회로를 추가하였다.

그림 2. 제안된 위상천이 방식의 DC-DC 컨버터

#### 2.2 제안회로의 모드별 동작

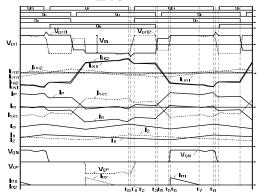

먼저,  $C_{oss}$ 의 값은 모두 같고, 모든 소자는 이상적이라고 가정한다. 스위치  $Q_A,Q_B$ 는 진상 레그,  $Q_C$ ,  $Q_D$ 는 지상 레그이고, 그림 5는 주요 동작파형이다. 모드는 총 8개로 나누어지지만설계를 위한 모드만 자세히 설명도록 하겠다.

(a)모드  $2(t_1\ t_2)$ :  $C_{ossP}$ 가 방전되며 SR스위치  $Q_P$ 의 영전압 스위칭이 이루어진다. SR스위치의 영전압 스위칭 만족시간 $(t_2\ t_1)$ 과  $C_{ossP}$ 에 흐르는 전류 값을 다음과 같이 구하였다.

$$t = \sqrt{C_{oss}L_e} \sin^{-1}(\frac{V_{QP}(t_1)}{\sqrt{V_{QP}(t_1)^2 + \frac{(i_{Lk1}(t_1)/n - i_2)^2L_e}{C_{oss}}}})$$

(2)

$$i_{\cos sP}(t) = \frac{V_{cl}}{L} \sqrt{C_{oss}L_e} \sin \sqrt{\frac{1}{C_{cs}L}} t$$

(©] 7 ]  $k$ ],  $L_e = (L_{k1} + L_{k2}) n^2$ ) (3)

(b)모드  $4(t_3 t_4)$ : 지상 레그 영전압 스위칭 구간으로 트랜스포머 2차 측은 단락상태가 유지돼 영전압 스위칭에 2차측의 출력 인덕터 전류가 영향을 주지 않는다. 하지만, 제안회로에서는  $T_2$ 의 자화전류를 증가시켜 영전압 스위칭 조건을 만족시킬 수있다. 그림 3은 모드 4의 등가회로이고 이를 이용하여 지상 레그를 영전압 스위칭하기 위해 필요한 시간( $t_4$   $t_3$ )을 구하였다.

$$t = \sqrt{2C_{oss}(L_{k1} + L_{k2})} \sin^{-1}\left(\sqrt{\frac{2C_{oss}}{L_{k1} + L_{k2}}} \frac{nV_{QD}(t_4)}{ni_{Lk1}(t_3)}\right)$$

(4)

그림3. 모드 4의 등가회로

(c)모드  $8(t_7\ t_8)$ :  $d_1$ 이 꺼지고 공진으로 인해 전류가 최대값을 갖는다.  $i_2$ 와  $i_{Lm2}$ 가 일정하면  $i_{p,peak}$ 로  $i_{Lk1,peak}$ 를 구할 수 있다. 그림4는 모드 8의 등가회로이고, 이를 이용하여  $i_p$ 를 구하였다.

그림4. 모드 8의 등가회로

$$\begin{split} &i_{P}(t) = n \frac{V_{in}t - A + \frac{L_{1}}{n}i_{1}(t_{7})}{L_{1} + L_{e}} + i_{2}(t_{7}) - \frac{nV_{in}}{L_{1} + L_{e}} \times \sqrt{\frac{C_{oss}L_{1}L_{e}}{L_{1} + L_{e}}} \sin(wt) \\ &+ \left[ \frac{n \left\{ A - \frac{L_{1}}{n}i_{1}(t_{7}) \right\}}{L_{1} + L_{e}} - \frac{A}{n(L_{k1} + L_{k2})} \right] \cos(wt) \\ & \left( \circlearrowleft 7 \left[ \lambda^{2} \right], \quad A = L_{k1}(i_{Lk1}(t_{7}) - i_{Lm}(t_{7})) + L_{k2}(i_{Lk2}(t_{7}) - i_{Lm2}(t_{7})), \\ &L_{e} = n^{2}(L_{k1} + L_{k2}), \quad w = \sqrt{\frac{L_{e} + L_{1}}{C_{oss}L_{e}L_{1}}}, i_{p,peak} = i_{p}(t_{8} - t_{7}) \right) \end{split}$$

$$(5)$$

그림 5. 제안회로의 동작 파형

## 3. 제안회로의 설계 가이드

## 3.1 $T_1$ 의 자화인덕턴스 $L_{m1}$ 의 설계

지상 레그를 영전압 스위칭 시키는 모드 4의  $i_{Lkl}(t_3)$ 를 식(3) 과 식(5)를 이용하여 다음과 같이 구할 수 있다.

$$i_{Lk1}(t_3) = \frac{V_{in}}{8f_S L_{m1}} + n \, i_{p,peak} + i_1(t_0) - n \, i_{cossP}(t_2 - t_0) \tag{6}$$

식 (6)과 식(4)를 이용하여 L<sub>ml</sub>의 조건식을 구할 수 있다.

$$L_{m1} \le \frac{1}{8f_s \left[ \frac{1}{\sin(w_2 \cdot t_d)} B + \frac{n\{-i_{p,peak} + i_1(t_0) + i_{cossp}(t_2 - t_0)\}}{V_{in}} \right]}$$

(7)

(여기사,

$$t_{\rm d}$$

=dead time,  $B = \sqrt{\frac{2C_{oss}}{L_{k1} + L_{k2}}}$ ,  $w_2 = \sqrt{\frac{1}{2C_{oss}(L_{k1} + L_{k2})}}$ )

## 3.2 클램프 저항 설계

효율 및 클램프 전압설정에 중요한 요인인 클램프 저항을  $i_{\rm dl}$  전류의 최대 값을 이용하여 구한다. 클램프 저항에 흐르는 전류는 다이오드의 평균전류이므로 다음과 같이 구한다.

$$\langle i_{d1} \rangle = \frac{1}{2} (i_{d,peak})^2 \times \frac{dt}{di_{d1}} \times f_s \tag{8}$$

$$\frac{di_{d1}}{dt} = \frac{\frac{V_{in}n}{2} \times \frac{L_{k1}}{L_{k1} + L_{k1}}}{\frac{L_{k1}}{L_{k1}}n^{2}} - \frac{\frac{V_{in}n}{2} \times \frac{L_{m1}}{L_{m1} + L_{k1}}}{\frac{L_{m1}}{L}n^{2}} - \frac{V_{cl} - V_{o}}{L_{2}}$$

(9)

$$\begin{split} i_{d1,peak} &= i_n(t_6) = Csin(\frac{1}{\sqrt{C_{oss}n^2(L_{k1} + L_{k2})}} (t_6 - t_3) + \sin^{-1}D) \\ &\left( \stackrel{\text{deg}}{\sim} |\mathcal{N}|, \ C = \sqrt{(\frac{V_{in}n}{L_{k1}n^2 + L_{k2}n^2})^2(C_{oss}n^2(L_{k1} + L_{k2}) + (i_{sec} - i_1)^2}}{D = \frac{i_{sec} - i_1}{\sqrt{(\frac{V_{in}n}{L_{k1}n^2 + L_{k2}n^2})^2(C_{oss}n^2(L_{k1} + L_{k2}) + (i_{sec} - i_1)^2}} \right) \end{split}$$

식(8),(9),(10)을 이용하여 다음과 같은 식을 얻을 수 있다.

$$R_{cl} = \frac{V_{cl}}{2 < i_{d1} >} \tag{11}$$

#### 4. 시뮬레이션

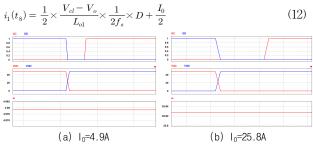

표 1의 파라미터를 3장에서 구한 식에 적용하여 PSIM을 이용한 시뮬레이션을 수행하였다. 식 (7)에서  $i_{p,peak}+i_1(t_0)=i_1(t_8)$ ,  $t_2$   $t_0=t_d$ 로 근사화 했다. 그리고, 출력 인덕터의 기울기를 이용하여 식 (12)를 구하고, 식 (7)과 식 (12)를 이용하여 주어진  $L_{ml}$ 에서 영전압 스위칭을 만족하는 최소 부하전류를 구하면  $I_0$ 는 4.36A가 나온다. 그림 6은  $I_0=4.9A$  이상에서 지상 레그 스위치가 영전압 스위칭 조건을 만족하는 것을 보여준다.

표 1 시뮬레이션 파라미터

| $V_{in}$        | 48V       | $V_o$            | 30V         |

|-----------------|-----------|------------------|-------------|

| D               | 0.621     | $t_{\rm d}$      | 100nsec     |

| $L_{m1},L_{m2}$ | 20uF,60uF | $L_{k1}, L_{k2}$ | 250nF,400nF |

| $L_1, L_2$      | 50uF      | n                | 2.5         |

그림 6. 부하에 따른 지상 레그 스위치의 영전압 스위칭 파형

#### 5. 결론

본 논문에서는 독립적인 하프 브리지 구조의 위상천이방식의 DC DC컨버터를 해석하고 설계방식을 제안하였다. 모드별 해석을 통해 얻은 수식들을 이용하여 지상 레그의 영전압스위칭을 위한 지상 레그에 관계하는 트랜스포머의 자화 인덕턴스와 클램프 저항의 설계 가이드를 제시하였다. 그리고, 시뮬레이션을 통하여 제안한 설계의 타당성을 검증하였다.

본 연구는 미래창조과학부 및 정보통신산업진흥원의 대학 IT연구센터육성 지원사업의 연구결과로 수행되었음 (NIPA 2013 H0301 13 2007)

## 참 고 문 헌

- [1] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B. H. Cho, "Design considerations for high voltage high power full bridge zero voltage switched PWM converter," in Proc. IEEE APEC, 1990, pp. 275 284

- [2] 김준구, 윤선재, 김재형, 원충연, 나종국, "AC 회생이 가능한 배터리 충.방전 테스트 시스템," 전력전자학회논문지 Vol. 17, no.2, April 2012, pp99 106

- [3] Jitaru, I.D.; Bolohan, N.D., "A High Efficiency 2KW DC DC Converter for automotive Application," inproc. IEEE APEC, 2012, pp. 22 27