# SIMT 구조 기반 멀티코어 GPGPU의 통합 ALU 설계

경규택\* · 곽재창\* · 이광엽\*\* \*서경대학교

An implementation of a unified ALU in multi-core GPGPU based on SIMT architecture

Gyu-taek Kyung<sup>\*</sup> · Jae-Chang Kwak<sup>\*</sup> · Kwang-yeob Lee<sup>\*\*</sup>

\*Seokyeong University

E-mail: amasid@skuniv.ac.kr

# 요 약

본 논문은 SIMT 구조 기반의 멀티코어 GPGPU의 통합 ALU를 설계하였다. 조건부 분기 명령어, 데이터 이동 명령어, 정수형 산술 연산 명령어, 부동소수점 산술 연산 명령어를 처리할 수 있으며 멀티코어 GPGPU의 다양한 형태의 병렬처리 기능을 지원하기 위하여 다 수의ALU가 탑재된다. 각 명령어 연산의 처리방식의 공통성을 회로 수준에서 통합하여 최소의 크기로 ALU를 설계하는 것이 본논문의 주안점이다. 모든 명령어는 테스트 프로그램을 작성하여 실험하였고 CPU로 연산한 결과와비교하여 본 논문의 ALU가 정상적으로 동작함을 검증하였다. 본 논문에서 설계한 통합 ALU의 크기는 약 2만 게이트이며 최대 동작주파수는 430MHz이다.

#### **ABSTRACT**

This paper describes an implementation of a unified ALU on multi-core GPGPU based on SIMT architecture. Our unified ALU can operate conditional branch instructions, data movement instructions, integer arithmetic instructions and floating-point arithmetic instructions. Since multi-core GPGPU contains a lot of ALU for parallel processing of various types, the main point of this paper is to design the minimum size ALU by unifying similar processing of each operations on circit level.

All instrunctions were tested by making a test program. And we compare this results with results of CPU operations to verify our ALU. Our unified ALU's gate size is approximately 20,000 and the maximum operation frequency is 430MHz.

#### 키워드

ALU, GPGPU, SIMT Architecture, IEEE754-2008

# 1. 서 론

최근 소형 임베디드 기기의 컴퓨팅 환경이 크게 발전함에 따라 다양한 컨텐츠를 지원하기 위한 노력이 시도되고 있으며 대표적인 분야로 고해상도 3차원 그래픽 컨텐츠 지원을 예로 들 수있다. 3차원 그래픽 처리를 위해서는 많은 양의데이터를 처리해야하며, 그 연산과정 또한 복잡하기 때문에 CPU만으로 이를 처리하는 것은 큰 부

담이 된다. 따라서 3D 그래픽 처리 및 다양한 형태의 병렬연산 수행이 가능한 GPGPU를 함께 탑재하는 것이 일반적인 추세가 되었다.[1]

GPGPU는 높은 병렬화를 통해 빠르게 연산을 처리하기 위해 코어의 수를 수십 개에서 많게는 수백 개를 갖는 멀티코어 구조로 설계되며 임베 디드 기기에서 사용됨에 따라 저전력과 작은 면 적을 가져야 한다. 따라서 각 코어의 크기를 줄이 는 것이 전체 GPGPU의 크기를 최소화하기 위한 방안의 핵심이 되고 있다.

본 논문에서는 GPGPU의 크기를 최소화하기 위한 방안으로 코어마다 탑재되는 ALU의 면적을 줄이는 것을 제안한다. 각 명령어를 연산하는 데 이터 처리경로와 사용 메모리를 통합하여 설계하 므로 각 연산 유닛이 중복적으로 사용하던 자원 을 절약하게 하여 전체 ALU의 면적을 감소시켰 고 이를 테스트벤치를 통한 시뮬레이션 및 합성 을 통해 동작을 실험 및 검증하였다.

### Ⅱ. 본 론

#### 1. SIMT 구조 기반 GPGPU 코어

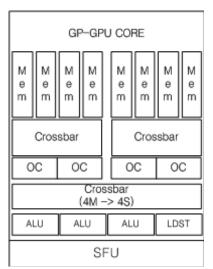

그림 1은 본 논문에서 제안하는 통합 ALU를 탑재하는 SIMT 구조 기반 GPGPU 코어의 구조이다. SIMT 구조의 특성으로 한 개의 코어는 한 개의 스레드에 대응되지만 본 논문의 코어는 슈퍼스칼라 명령어 발행방식을 적용하여 한 코어당서로 다른 네 개의 스레드를 동시에 처리할 수있는 구조이다. 따라서 본 논문에서 언급하는 GPGPU는 통합 ALU가 세 개씩 탑재된 코어와외부 제어 유닛, 특수함수 연산 유닛 및 메모리로 구성된다.[2]

본 논문의 GPGPU는 코어의 수를 선택하여 합성할 수 있는 구조이므로 코어를 많이 탑재 할수록 통합 ALU의 면적 감소 이점이 전체 GPGPU 면적 감소에 큰 영향을 미치는 요소가될 수 있다.

그림 1. SIMT 구조 기반 GPGPU 코어 구조

#### 2. 통합 ALU

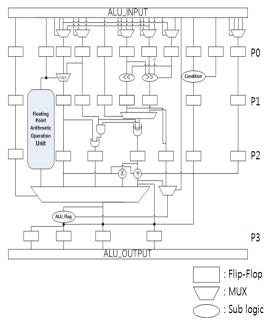

그림 2는 본 논문에서 제안하는 통합 ALU의 회로수준 구조이다. 4단 파이프라인으로 동작하도록 설계하였으며 분기 명령어, 데이터 이동 명령어, 정수형 산술 연산 명령어, 부동소수점 산술

연산 명령어의 처리가 가능하다. 각 명령어 연산의 처리방식 중 공유할 수 있는 데이터 경로 및사용 메모리를 회로수준에서 통합하였으며 코어외부의 ALU 제어유닛으로부터 제어 신호를 입력받아 해당 명령어 연산에 적합한 데이터 경로를따라 작업을 처리하는 방식으로 설계하였으나 부동소수점 산술 연산기의 경우 IEEE754-2008 표준정밀도 기준을 만족시켜야 하기 때문에 외부 제어 유닛의 입력 신호와 데이터의 입출력 경로만을 공유하고 연산기 내부는 별도로 구현하였다.[3][4]

그림 2. 통합 ALU 회로도

SIMT 구조 기반 GPGPU에 탑재되는 통합 ALU의 동작은 각 스레드가 개별적으로 레지스터를 소유하므로 동일한 레지스터 인덱스를 사용하여도 각 스레드 내 레지스터에 담긴 데이터 값이다르기 때문에 처리하고자 하는 레지스터의 인덱스 및 제어 신호에 따른 데이터 처리 경로가 모두 동일하여도 각 스레드마다 원하는 결과 값을얻을 수 있다. 이러한 특징을 이용하여 연산을 효율적으로 처리하기 위해 모든 코어에 동일한 값으로 입력되는 제어신호 및 데이터는 코어 외부의 ALU 제어유닛에서 일괄적으로 처리하도록 설계하였다. 이에 따라 코어의 수를 늘리더라도 동일한 신호 및 메모리를 중복적으로 사용하는 부분이 제거되었으므로 ALU 내부의 중복적으로 사용되는 면적의 낭비를 피할 수 있다.[5][6]

통합 ALU 제어유닛은 각 코어당 통합 ALU가세 개씩 탑재되므로 각각의 ALU를 제어하기 위해 총 세 개가 존재한다.

#### Ⅲ. 설계 및 검증

#### 1. 하드웨어 구현

본 논문에서 제안하는 통합 ALU는 Verilog HDL로 설계하여 Model-Sim SE 10.0b로 테스트 벤치 및 시뮬레이션을 진행하였고 Synopsys사의 Design Compiler로 합성하여 결과를 실험 및 검증을 진행하였다.

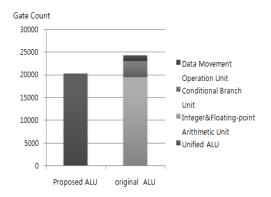

그림 3. 합성 결과 면적 비교그래프

### 표 1. 합성 결과 면적 비교표

단위 : Gate Count

| Original | Proposed                     |  |

|----------|------------------------------|--|

| ALU      | ALU                          |  |

| 1164     |                              |  |

| 1104     | 20214                        |  |

| 2651     |                              |  |

| 3031     | 20214                        |  |

| 10401    |                              |  |

| 13401    |                              |  |

| 24216    | 20214                        |  |

|          | ALU<br>1164<br>3651<br>19401 |  |

### 표 2. 코어 수 증가에 따른 면적 비교표

단위 : Gate Count

| Core            | 1     | 8      | 16      | 32      | 64      |

|-----------------|-------|--------|---------|---------|---------|

| original<br>ALU | 72648 | 581184 | 1162368 | 2324736 | 4649472 |

| Proposed<br>ALU | 60642 | 485136 | 970272  | 1940544 | 3881088 |

| 감소치             | 12006 | 96048  | 192096  | 384192  | 768384  |

## 2.합성 결과

Synopsys사의 Design Compiler를 사용하여 최

대 430MHz의 동작주파수로 합성이 가능하였으며 합성 시 약 2만 게이트의 면적을 차지하는 것을 확인하였다.

그림 3과 표 1은 본 논문에서 제안하는 ALU와 회로적으로 통합되지 않은 기존의 ALU의 합성 면적 비교 결과이다.

그림 3의 결과, 통합 ALU의 면적은 기존의 ALU의 면적보다 16.53% 감소하였다. 이 결과는 한 코어당 세 개의 ALU가 탑재되므로 한 코어당세 배의 면적 감소의 이득을 얻을 수 있다. 또한 표 2는 GPGPU의 코어 수에 따른 기존 ALU 대비 통합 ALU 탑재 시 합성 면적 감소치를 표기한 것이다. GPGPU의 코어 수가 표 2의 결과 중가장 많은 64개일 경우 면적 감소치를 통해 확보할 수 있는 면적은 코어를 약 3개, 또는 본 논문에서 제안하는 통합 ALU를 약 38개 더 탑재 할수 있는 크기이다.

# 3. 검증 방법

본 논문의 통합 ALU가 신뢰성 있게 동작하는지 검증하기 위한 기준으로 CPU의 연산결과 값을 사용하였다. 테스트벤치로부터 얻은 결과 값을 CPU 연산의 결과 값에 비교한 결과 본 논문에서제안하는 통합 ALU가 신뢰성 있게 동작함을 검증하였다.

#### Ⅳ. 결 론

본 논문은 소형 임베디드 기기에 탑재하기 적합한 멀티 코어 GPGPU의 통합 ALU를 설계하였다. 각 연산의 공통적인 데이터 처리 경로와 사용메모리를 회로수준에서 통합하여 합성 시 기존 ALU 대비 약 17%의 면적을 감소시켰으며 이는 코어 수가 늘어날수록 점차 큰 이점이 된다.

Synopsys사의 Design Compiler를 사용하여 합성한 결과 약 2만 게이트의 면적과 최대 430MHz의 동작주파수로 합성이 가능하였고 동작 검증을 위해 각종 명령어를 사용한 테스트벤치로 부터 얻은 결과 값을 CPU 연산의 결과 값과 비 교하여 본 논문에서 제안한 통합 ALU가 정상적 으로 동작함을 검증하였다.

### 참고문헌

[1] 정형기, 능동형 스레드 관리 기법을 적용한 멀티 스레드 멀티 코어 GP-GPU 설계, 서경대학 교 학위논문(박사), 2010

[2] 김성수, SIMT프로세서를 위한 테이블 기반 분기 재통합 방식, 연세대학교 학위논문(석사), 2012

[3] 황복식, 32비트 ALU 설계에 대한 연구, 한 국컴퓨터정보학회지, 제7권, 제4호, 통권 제 24호, p89-93, 12, 2002

- [4] 황진하, IEEE754-2008을 위한 고속 부동소 수점 연산기 설계, 전자공학회 논문지, 제 48권, SD편 제 10호, 10, 2011

- [5] 이보행, 멀티스레드 파이프라인 및 범용 레지스터 구조를 적용한 GP-GPU 설계, 서경대학교학위논문(석사), 2010

- [6] 전둘봉, 모바일 그래픽스용 클리핑과 컬링을 포함한 래스터라이저 설계, 서경대학교 학위논 문(석사), 2008

# Acknowledgement

본 논문은 미래창조과학부 지원으로 수행한 ETRI SW-SoC융합 R&BD센터의 연구결과입니다.