#

성명우\*·최성규\*·김성우\*·김신곤\*·이주섭\*\*·오세명\*\*·서민수\*\*·류지열\* \*부경대학교·\*\*(주)네드텍

Design of a 12-bit 1MSps SAR ADC using 0.18 m CMOS Process

Myeong-U Seong<sup>\*</sup> · Seong-Kyu Choi<sup>\*</sup> · Sung-Woo Kim<sup>\*</sup> · Shin-Gon Kim<sup>\*</sup> · Joo-Seob Lee<sup>\*\*</sup> · Se-Moung Oh<sup>\*\*</sup> · Min-Soo Seo<sup>\*\*</sup> · Jee-Youl Ryu<sup>\*</sup>

\*Pukyong National University · \*Nedtech Co., Ltd.

E-mail: db6611@gmail.com

### 요 약

본 논문에서는 0.18  $\mu$  CMOS 공정 기술을 이용하여 12-bit 1MSps 연속 근사화 아날로그-디지털 변환기(Analog to Digital Converter : ADC)를 설계하였다. 설계된 아날로그-디지털 변환기는 Cadence Tool을 이용하여 시뮬레이션 및 레이아웃을 진행하였다. 시뮬레이션 결과 1.8V의 공급전압에서 전력 소모는 5.5mW였고, 입력 신호의 주파수가 100kHz일 때, SNDR은 70.03dB, 유효 비트수는 11.34bit의 결과를 보였다. 설계된 변환기는 0.8mm  $\times$  0.7mm 크기로 레이아웃 되었다.

#### 키워드

SAR, ADC, Data Converter, 1Msps, 12-bit, CMOS

## 1. 서 론

CMOS 공정 기술이 발전하면서 트랜지스터의 최소 길이가 점점 줄어들고, 그에 따라 공급 전압과 면적이 줄어들면서 하나의 칩에 더 많은 기능들을 집적할 수 있게 되었다. 아날로그 블록과 디지털 블록을 하나의 칩 안에 구현이 가능하게 되면서 아날로그 신호를 디지털 신호로 바꾸어 주는 변환기(ADC)의 중요성이 점점 증가하고 있다[1-5].

다양한 구조의 ADC 중에서 연속 근사화(SAR) 아날로그-디지털 변환기는 적절한 해상도를 가지면서 적은 전력을 소모하는 구조이다. 본 논문에서는 1.8V의 공급 전압에서 저전력, 저면적의 12-bit 1MSps 연속 근사화 아날로그-디지털 변환기를 설계하였다.

# Ⅱ. 본 론

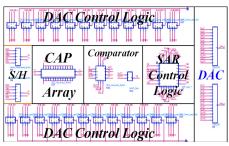

설계한 ADC는 그림 1과 같이 샘플-앤-홀드단, 커패시터 어레이단, 비교기, SAR 제어 로직단, DAC 및 DAC 제어 로직단으로 구성되며 전체 블록의 크기와 전력 소모를 최소화하기 위한 최 적화를 고려하여 설계를 수행하였다.

그림 1. SAR ADC 블록도

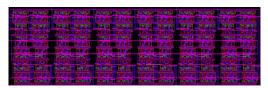

그림 2는 SAR 제어 로직단 레이아웃 결과를 나타낸 것으로, 12개의 D-플립플롭과 논리 게이 트로 구성하였다. SAR 제어 로직과 DAC 제어 로직에서 12-bit의 디지털 코드를 출력하게 되고 DAC 제어 로직은 SAR 제어 로직의 클럭이 상승 에지일 때 비교기의 출력값이 샘플링 되도록 하 여 비교기 출력이 'High'이면 접지에, 'Low'이면 기준 전압에 스위칭 되도록 설계하였다.

그림 2. SAR 제어 로직단 레이아웃 결과

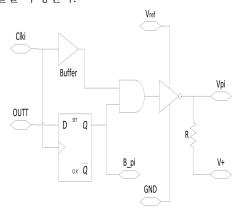

DAC 제어 로직단은 그림 3과 같이 D-플립플롭, 딜레이 버퍼, 논리 게이트 및 인버터로 구성된다. DAC 제어 로직단은 SAR 제어 로직단으로부터 제공된 12개의 순차적인 클럭과 비교기의출력 값의 상태에 따라 커패시터 어레이단에 배치되어 있는 각 커패시터의 bottom 플레이트에서기준 전압 혹은 접지로 스위칭 되도록 제어하는역할을 수행한다.

그림 3. DAC 제어 로직단

#### Ⅲ. 시뮬레이션 결과 및 레이아웃

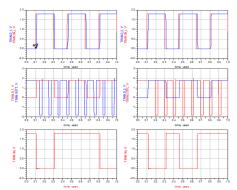

그림 4는 DAC 제어 로직단의 시뮬레이션 결과를 나타낸 것으로 D-플립플롭은 클럭 신호인 Clki의 상승 에지에서 비교기 출력을 샘플링하게된다. 이때 비교기 출력(Vourn)이 'High'가 되면기준 전압에서 접지로 스위칭 되고 비교기 출력이 'Low'가 되면 기준 전압에 연결된 상태를 유지하게된다. 그러나 Clki의 하강 에지에서는 항상기준 전압에 연결된 상태를 유지하게된다.

그림 4. DAC 제어 로직단의 시뮬레이션 결과

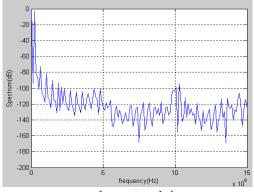

그림 5는 100kHz의 입력 신호를 인가하였을 때 아날로그-디지털 변환기의 FFT 시뮬레이션 결과를 나타낸 것이다. 시뮬레이션 결과 SNDR은 약 70.03dB, 유효비트수(ENOB)는 11.34bit의 값을 보였다.

그림 5. FFT 결과

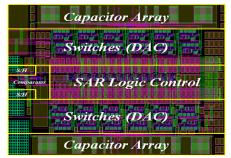

그림 6은 연속 근사화 아날로그-디지털 변환기의 각 구성단을 레이아웃한 결과로 0.18 / CMOS 공정에서 Cadence Tool을 이용하여 수행하였다.

그림 6. 연속 근사화 아날로그-디지털 변환기 레이아웃 결과

# Ⅳ. 결 론

본 논문에서 설계한 연속 근사화 아날로그-디지털 변환기는 고해상도이면서 저면적, 저전력을 요구하는 기기에 적합하도록 설계하였다. 설계된 아날로그-디지털 변환기는 0.8mm × 0.7mm 크기로 레이아웃 되었고, SNDR은 70.03dB, ENOB는 11.34bit의 시뮬레이션 특성을 보였다.

#### 감사의 글

본 연구는 한국산업기술진흥원의 지역산업기술 개발 사업 재원으로 지원을 받아 수행된 연구결 과입니다 (C-D-2013-0014, 장판 결함 검출용 초고 속 자기 영상 융합 시스템 개발).

# 참고문헌

- [1] A . M . Abo *et. al.*, "A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to- Digital Converter" Solid-State Circuits, IEEE Journal of vol. 34, pp. 599-606, 1999.

- [2] C. C. Liu *et. al.*, ""A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure" Solid-State Circuits, IEEE Journal of vol. 45, pp. 731-740, 2010.

- [3] J. McCreary *et. al.*, "All-MOS charge redistribution analog-todigital conversion techniques Part I" Solid-State Circuits, IEEE Journal of vol. , pp. 371-379, 1995.

- [4] R. E. Suarez *et. al.*, "All-MOS charge redistribution analog-todigital conversion techniques Part II" Solid-State Circuits, IEEE Journal of vol. 10, pp. 379-285, 1995.

- [5] 최성규, 김성우, 성명우, 류지열, "12bit 1MSps CMOS 연속 근사화 아날로그-디지털 변환기 설계", 한국정보통신 학회 종합학술대회 논문집, 제17권, 제1호, pp. 352-353, 2013년 5월.