# 나노선 구조를 갖는 쇼트키 장벽 MOSFET 과 MOSFET 의 특성 비교

정효은, 이재현

카이스트 전기 및 전자공학과, 대전광역시 305-701, 대한민국. e-mail: junghe@kaist.ac.kr, jaehyun.lee@kaist.ac.kr

#### **ABSTRACT**

본 논문에서는 실리콘 나노선 구조를 갖는 모스펫 (Metal-Oxide-Semiconductor Field Effect Transistors, MOSFETs)과 쇼트키 장벽 트랜지스터 (Schottky-Barrier(SB) MOSFETs, SB-MOSFETs)의 전기적인 특성을 양자역학적시뮬레이션 계산을 통해 비교하였다. 쇼트키 장벽 높이 (Schottky Barrier,  $\phi_{SBH}$ )에 따른 SB-MOSFETs의 터널링 특성을 분석하고, 소스/드레인 (S/D) 길이가 변함에 따라 달라지는 S/D 저항을 계산하여,  $\phi_{SBH}$  가 OeV 인 SB-MOSFETs의 On과 Off  $I_D$  비율 ( $I_{ON}$  /  $I_{OFF}$  )이 MOSFETs보다 개선될 수 있음을 보였다.

### INTRODUCTION

장벽 트래지스터 (Schottkybarrier(SB) MOSFETs, SB-MOSFETs)는 최근 기존의 모스펫 (MOSFETs)을 대체할 수 있는 소자로 주목 받고 있다 [1]-[4]. 이는 양쪽 소스/드레인 (S/D)을 높은 농도로 도핑 하는 MOSFETs과는 달리 SB-MOSFETs은 컨택을 사용하기 때문에 상대적으로 기생(parasitic) 저항을 갖고, 특히 채널 길이가 점점 짧아지면서 발생하는 단 채널 효과를 개선 할 수 있다 [5], [6]. 또한, 단 채널에서는 S/D간의 침식 현상 (punch through)으로 누설 전류가 발생하게 되는데, 이를 개선하기 위해 S/D의 두께를 아주 얇게 만들어야 한다. 하지만, 도펀트 (dopant)의 확산 현상 때문에 얇게 만드는 것도 어려울 뿐만 아니라, 저항 증가로 인하여 도핑 농도를 더 크게 해야 하므로 공정에 대한 부담이 커지고 있음을 고려할 때. SB-MOSFETs은 많은 이점을 가지고 있다.

그럼에도 불구하고, SB-MOSFETs은 S/D과 채널의 계면에서 각각 생성되는 쇼트키 장벽 (Schottky Barrier, SB,  $\phi_{SBH}$ ) 때문에 동작전류 ( $I_{ON}$ )가 감소하게 된다 [7], [8]. 그래서 낮은

$V_D = I_DR + V_{ch}$ ,  $(R = R_S + R_D)$

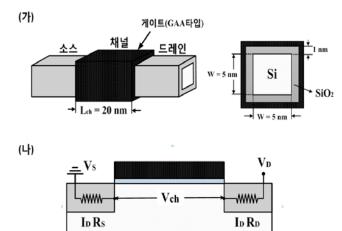

그림 1. (가) 채널 [100] 방향의 실리콘 나노선 트랜지스터의 시뮬레이션 소자 구조. (나) S/D 저항을 고려한 실제적인 레이아웃.

쇼트키 장벽( $\phi_{SBH}$ )을 갖는 금속 물질을 찾거나, 금속과 채널 계면에 도핑을 해주는 도펀트 세그리게이션 (dopant segregation)방법 또는 다양한 게이트 구조를 통한 효율적인 제어가 가능한 소자에 대한 연구가 활발히 이루어지고 있다 [9]-[11].

본 연구에서는 SB-MOSFETs의  $\phi_{SBH}$  에 따른 SB-MOSFETs 특성을 MOSFETs 특성과 비교해보고자 한다. 또한 시뮬레이션 상에서 실제로 고려하지 못하는 S/D 저항을 계산하여 두소자에서의 S/D 길이( $L_{S/D}$ )에 따른 특성 변화를 보도록 하겠다.

**35** 234

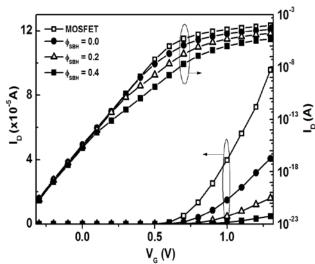

그림 2. SB-MOSFETs 의  $\phi_{SBH}$  을  $0\sim0.4\mathrm{eV}$  까지 변화시키면서 MOSFETs 과 비교한  $I_D-V_G$  특성. 두소자 모두 채널길이 $(L_{ch})=20$  nm, 채널 폭(W)=5 nm.

## SIMULATION APPROACH

본 연구에서 고려한 소자는 그림 1(가)와 같다. 게이트가 나노선을 둘러 싸고 있는 3D 구조의 Gate-All-Around(GAA) 타입이며, 금속 컨택을 사용한 SB-MOSFETs과는 달리 MOSFETs의 경우에는 S/D 영역을 n형  $10^{20} cm^{-3}$  로 도핑 하였다. 채널영역은 두 소자 모두 (intrinsic)이며, 길이( $L_{ch}$ )는 20 nm 이다. 수송방향의 결정구조는 [100] 방향이며, 실리콘 두께와 폭(W)은 모두 5 nm 이고 절연체는 1 nm의 SiO<sub>2</sub> 로 둘러싸여 있다. 양자역학적 시뮬레이션을 위해 유효질량 (Parabolic Effective mass, PEM) 해밀토니안을 구성하여 비 그린함수 (Non-equilibrium Green's function, NEGF)를 가지고 드레인 전류  $(I_D)$ 를 계산하였다.

SB-MOSFETs 에서는 S/D이 금속이기 때문에 저항의 크기가 무시될 만큼 작지만, MOSFETs의 경우에는  $L_{S/D}$ 에 따른 저항 증가로 채널 양단에 가해지는 전압  $(V_{ch})$  은 실제 외부에서 인가한 드레인 전압 $(V_{D})$  보다 더 작게 된다 (그림 1(나)). 본 연구에서 사용한 시뮬레이션은 산란 (scattering)효과가

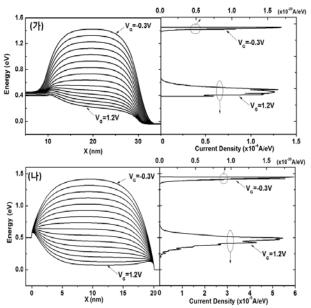

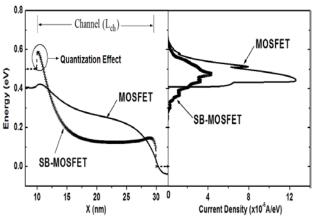

그림 3. (가) MOSFETs 의 게이트 전압  $V_G$ 에 따른 포텐셜과(왼쪽) 전류밀도(오른쪽). (나)  $\phi_{SBH}$  가 0 eV 인 SB-MOSFETs 의 포텐셜과(왼쪽) 전류밀도(오른쪽). 두 소자 모두 채널길이( $L_{ch}$ ) = 20 nm, 채널 폭(W) = 5 nm.

고려되지 않았기 때문에,  $L_{S/D}$  에 따른 저항 특성은 식(1)을 이용하여 계산하였다.

$$V_D = I_D R + V_{ch} \qquad (1)$$

MOSFETs은 시뮬레이션에서 계산된  $I_D - V_D$  결과를 바탕으로 외부전압이  $V_D$  일 때 채널에 실제로 걸리는 전압( $V_{ch} = V_D$ )을 추출하여 S/D 저항(R)을 고려한 실제 드레인 전류를 계산하였다. R은  $\rho L_{S/D}/W^2$  식을 사용한 S/D의 총 저항이며,  $\rho$  는 n형  $10^{20} \, cm^{-3}$  에 대한 저항률이다. SB-MOSFETs에서는 금속이 매우 작은 저항을 가지므로, 전압 강하 없이 채널에  $V_D$  만큼 가해진다고 가정하여, 시뮬레이션에서 나온 결과를 그대로 사용하였다.

#### RESULTS

그림 2 는 SB-MOSFETs 의  $\phi_{SBH}$  을  $0{\sim}0.4{\rm eV}$  로 변화시키면서 계산한 각각의  $I_D-V_G$ 와, 같은 조건에서의 MOSFETs 의 결

36

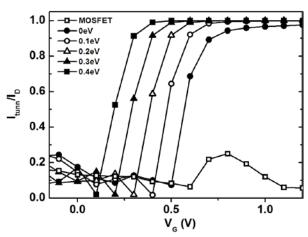

그림 4. MOSFETs과 SB-MOSFETs의  $\phi_{SBH}$  에 따른  $I_{tunn}/I_D$ .  $\phi_{SBH}$ 는 0~0.4eV까지 변화시켰고, 두 소자 모두 채널길이( $L_{ch}$ ) = 20 nm, 채널 폭(W) = 5 nm.

과를 함께 나타낸 것이다. 여기서의 MOSFET 은 S/D 저항을 무시하고 계산하였다. 그림 2 에서 볼수 있듯이,  $\phi_{SBH}$  가 증가할수록 SB-MOSFETs 의  $I_{ON}$ 은 감소하게 되는데, 이는 포텐셜과 그에 따른 전류 밀도를 통해 쉽게 설명할 수 있다. 그림 3 에서와 같이,  $V_G$ =-0.3V 일 때에는 두 소자 모두 전류 밀도가 모두 채널 장벽 위로 형성되고 있음을 볼 수 있다. 이는 열 이온 (thermionic)에 의해  $I_D$  가 결정된다는 것을 의미한다.  $V_G$ =1.2V 일 때에도 MOSFETs 은 열 이온에 의해  $I_D$  가 형성되는데 반해, SB-MOSFETs 은 장벽 밑으로 발생하는  $I_{tunn}$  가 증가했다는 것으로부터 SB-MOSFETs 는  $\phi_{SBH}$  에 따른  $I_{tunn}$  가  $I_{ON}$  을 결정짓는 것으로 볼 수 있다.

그림 4 는 서로 다른  $\phi_{SBH}$ 을 가진 SB-MOSFETs 과 MOSFETs 의  $I_D$ 에 대한  $I_{tunn}$ 비율을 계산한 결과이다. MOSFETs 은 SB-MOSFETs 과 다르게  $V_G$ 에 관계없이  $I_{tunn}$ 에 대한 의존성이 SB-MOSFETs 에 비해 작다는 것을 알 수 있다. 반면에 SB-MOSFETs 은  $V_G$ 가 커짐에 따라  $I_{tunn}$ 의 의존성이 증가하여, 결국에는  $I_{tunn}$ 에 의해  $I_D$ 가 결정되게 된다. 이는 SB-MOSFETs 의 그림 5. 게이트 전압  $V_G$ =1.1V에서 두 소자의 포텐셜과 (왼쪽) 전류밀도 (오른쪽). SB-

MOSFETs 의  $\phi_{SBH}$  는 0 eV 이고, 양자화 효과에 의한 장벽 증가를 나타냄. 두 소자 모두 채널길이 $(L_{ch})$  = 20 nm, 채널 폭(W) = 5 nm.

$\phi_{SBH}$  가 높을수록 전자는 낮은 게이트 전압에서부터 장벽을 느끼게 되어 터널링에 의한비율이 높아지기 때문에 전류 감소를 초래하는 것으로 볼 수 있다. 이러한 이유로  $I_{tunn}$  이 증가하기 이전에는 SB-MOSFETs의 문턱전압이하 기울기 (subthreshold swing, SS)가 MOSFETs과 동일한데 반해, 터널링을 하기시작하면서  $I_{tunn}$  의존성이 커지면서 SS가 감소함을 그림 2 에서도 확인 할 수 있다.

그림 5는 동작 상태 (on-state,  $V_G$ =1.1V)에서 SB-MOSFETs과 MOSFETs의 특성 비교를 위해 포텐셜과 전류 밀도를 함께 그린 그림이다. 주목할 점은 SB-MOSFETs의  $\phi_{SBH}$  가 0eV 이더라도 MOSFETs 보다 적은 전류가 흐른다는 것이다. SB-MOSFETs이라도 터널링 장벽이 없다면 MOSFETs과 유사한  $I_{ON}$ 을 가질 것으로 예측되는데, 실제로는 소자가 작아지면서 나타나는 양자화 효과 (quantization effect)에 의해 0eV 보다 높은 장벽이 형성되기 때문에 이상적인 오믹 접합 (ohmic contact)을 갖는 MOSFETs 보다는 적은 전류 값을 갖게 된다.

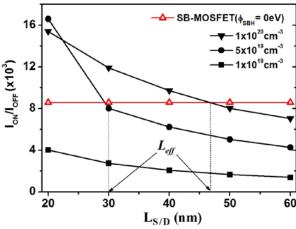

그림 6는 MOSFETs의 S/D 저항을 고려하여  $L_{S/D}$  에 따른 On과 Off 상태의  $I_D$  비율( $I_{ON}/I_{OFF}$ )을 계산한 결과이다.  $I_D$  는 시뮬레이션 결과와 식 (1)을 사용하여 계산하였고  $I_{Off}=10^{-9}A$  로 가정하였다. 외부에서 가한  $V_D=0.5~V$ 는 S/D 이전에서의 전압 강하와 접합 저항을 고려하지 않은 값이다. 그림 6에서 볼 수

그림 6.  $L_{S/D}$  에 따른 MOSFETs 과 SB-MOSFETs 의  $I_{ON}$  /  $I_{OFF}$  .

있듯이,  $L_{S/D}$ 가 길어짐에 따라 저항이 커지므로, MOSFETs의  $V_{ch}$  가 작아지면서  $I_{ON}$   $/I_{OFF}$  가 감소하게 되고  $L_{S/D} = L_{eff}$  이상에서는 전압강하가 거의 없는 SB-MOSFETs이 MOSFETs 대비 더 좋은  $I_{ON}$   $/I_{OFF}$  성능을 보인다는 것을 알 수 있다. 같은  $L_{S/D}$  에서  $L_{e\!f\!f}$  값은 MOSFETs의 도핑농도가 도핑농도에 의해 결정되는데, 높을수록 S/D의 저항률은 감소하기 때문에 전압강하가 적게 일어나게 된다. 그 결과 도핑농도가  $5 \times 10^{19} cm^{-3}$ 일 때에는  $L_{eff}$   $\square$  30 nm 이지만 도핑농도가  $10^{20}cm^{-3}$  로 증가하게 되면 그만큼 S/D의 전압강하에 대한 영향이 감소하기 때문에  $L_{eff}$   $\square$  47 nm 로 그 길이가 증가하는 것을 알 수 있다.

## DISCUSSION

SB-MOSFETs의 성능 향상을 위해서는  $\phi_{SBH}$ 을 작게 만들 수 있는 공정 개발이 요구된다. 현재까지 n형 SB-MOSFETs 기준으로 가장 적은  $\phi_{SBH}$ 는  $0.27 \mathrm{eV}$ 로 알려져 있다. 본 논문에서는 도핑농도  $10^{20} \, cm^{-3}$  기준  $L_{eff}$  47 nm 결과를 얻었지만 외부전극과 S/D의 접합 저항을 고려하면 이 길이는 더 짧아질 수 있다. 이는, 나노 선 구조를 가진 MOSFETs은 S/D의 도핑 농도 향상, 또는  $L_{S/D}$ 의 감소와 같은 방법으로 저항 감소가 필수적이라고 할 수 있다.

#### CONCLUSION

본 논문에서는 SB-MOSFETs의 장벽 높이  $\phi_{SBH}$  을 변화시키면서 MOSFETs과 그 특성을 비교하였다. 나노 선 구조를 가진 SB-MOSFETs은  $\phi_{SBH}$  가  $0 \mathrm{eV}$  인 경우에도 이상적인 오믹 접합을 갖는 MOSFETs 보다 작은  $I_{ON}$  을 갖는다. 하지만 실제적인 S/D 저항에 의한 전압강하를 고려하게되면  $L_{S/D} \geq L_{eff}$  의 조건에서 SB-MOSFETs은 MOSFETs보다 더 좋은  $I_{ON}$  /  $I_{OFF}$  을 가질 수 있고, 도핑농도가 높을수록 더 긴  $L_{eff}$  을 갖는다는 것을 확인 할 수 있었다.

## **ACKNOWLEDGEMENT**

참신한 연구를 할 수 있게 도움을 주신 EDISON 관계자 및 개발자 분들께 감사 말씀 드립니다.

#### **REFERENCES**

- [1] J. Guo and M. Lundstrom, IEEE Trans. Electron Devices **49**, 1897 (2002).

- [2] M. P. Lepselter and S. M. Sze, Proc .IEEE, **56**, 1400–1402(1968).

- [3] J. R. Tucker, C. Wang, and P. S. Carney, Appl. Phys. Lett., **65**, 618–620(1994).

- [4] J. Kedzierski et al., IEDM Tech. Dig., 57-60 (2000).

- [5] A. Cros et al., IEDM Tech. Dig., 663-666(2006)

- [6] S. Poli and M. G. Pala, SISPAD '09. International Conference, 1-4(2009)

- [7] C. Ahn and M. Shin, IEEE Trans. Nanotechnol. **5**, 278–283(2006)

- [8] Atsushi Yagishita et al., Japanese Journal of Appl. Phys. 43, 1713-1716(2004)

- [9] J. L. Padilla et al., IEEE Trans. Electron Devices, **59**, 1320–1327(2012)

- [10] A. Afzalian and D. Flandre, Solid State Electronics, **65**, 123-129(2011)

- [11] M. Shin, IEEE Trans. Electron Devices, **55**, 737–742(2008)

38