# MMC(Modular Multi-level Converter) Topology 및 제어알고리즘 개발에 관한 연구

정종규\*, 홍정원\*, 한병문\*, 박용희\*\*, 명지대학교\*, (주) 효성\*\*

## Study on The Development of MMC(Multi-level Converter) Topology and Control Algorithm

Jong Kyou Jeong\*, Jung Won Hong\*, Byung Moon Han\*, Yong hee Park\*\* Myongji University\*, Hyosung Corp.\*\*

#### **ABSTRACT**

본 논문에서는 최근 직류송전용 컨버터로 많은 관심이 집중되고 있는 MMC(Modular Multi level Converter)에 대해서 소개하고 있다. 대용량 전압원 컨버터로 MMC가 적합한 이유에대해서 설명하고, MMC의 동작원리, SM(Sub Module) dc capacitor voltage balancing 기술, 전체 제어 시스템에 대해 자세하게 설명하고 있다. 제안하는 MMC는 Staircase Modulation 방식으로 사인파형에 가까운 출력전압을 형성하고, Sorting 알고리즘을 구현하여 개별 SM의 커패시터 전압이 균등하게 일정 값을 유지하도록 하였다. 제안하는 MMC의 성능평가를 위하여 PSCAD/EMTDC 프로그램을 이용하여 3상 11 level MMC를 모의하였다.

### 1. 서 론

최근 자기소호가 가능한 IGBT, GTO등의 전력용 반도체 소자의 개발이 가속화되고 있다. 이에 따라 대용량 전압원 컨버터의 개발이 가능하게 되고 이를 FACTS(Flexible AC Transmission System), HVDC(High Voltage Direct Current) Transmission 등에 응용하는 연구가 활발하게 이루어지고 있다. 특히 HVDC분야는 그 동안 대용량에서는 싸이리스터를 이용한 전류원 HVDC시스템이 주를 이루었다. 하지만 대용량전압원 컨버터가 경쟁력을 갖추면서 대용량 HVDC시스템에 적용되는 곳이 늘어가고 있다. 대용량 전압원 HVDC시스템에서 가장 핵심이 되는 기술은 전압원 컨버터의 토폴로지와 모듈레이션 방식이다. 최근 직류송전용 전압원 컨버터로 모듈형 멀티레벨 컨버터에 대한 연구가 활발하게 이루어지고 있다.[1]

본 논문에서는 MMC의 출력파형 고조파 저감 알고리즘과 개별 SM의 직류전압 불평형을 억제하는 알고리즘을 제안하고, 알고리즘의 타당성을 검증하기 위하여 PSCAD/EMTDC 소프 트웨어를 이용하여 3상 11 level MMC의 동작을 시뮬레이션으로 검증하였다.

#### 2. MMC(Modular Multilevel Converter)

### 2.1 MMC 동작원리

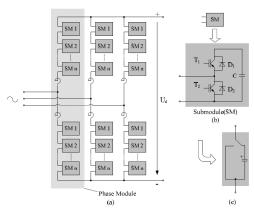

그림 1은 MMC의 회로 구성도이다. MMC의 Phase Module 은 상·하단 arm으로 구성이 된다. 각 arm은 직렬로 연결된 SM(Sub Module)로 구성이 되며, SM은 스위치 상태에 따라서 출력 측 터미널에 커패시터의 전압을 형성하거나 바이패스 동작을 하여 영전압을 형성한다. 만약 상·하단 arm의 각 SM중전압을 형성하는 동작을 하는 개수를 적절하게 조정하면 출력전압의 크기를 제어할 수 있다.

그림 1 MMC와 Sub-Module의 구성도, Sub-Module의 등가모델 Fig. 1 Design of MMC and Sub-Module, Sub-Module's electrical equivalent

## 2.2 출력전압 고조파 저감 알고리즘

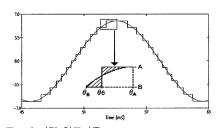

MMC의 출력전압은 각 SM에서 형성하는 전압이 합쳐져서 나타난다. 그림 2는 MMC에서 나타나는 출력전압이 사인에 가까운 파형을 형성함으로서 고조파를 저감하는 방법을 나타낸 것이다. 만약 각 SM의 출력전압의 폭을 적절하게 조절하면 사인에 가까운 출력전압을 얻을 수 있다. [2] MMC의 유·무효전력을 독립적으로 제어하기 위해서는 출력전압의 크기와 위상을 적절하게 조절하여야 한다. 기준 출력전압의 크기가 변함에 따라 고조파 저감 알고리즘이 제대로 동작하기 위해서 아래 수식에 MI(Moduation Index)를 추가하였으며,  $v_{ac}=m_a\sin\theta$ 로 설정하였다.

그림 2 고조파 저감 알고리즘 Fig. 2 Algorithm for harmonic reduction

고조파 저감 알고리즘의 기본원리는 두 개의 빗금 친 부분의 면적이 동일하다면 주어진 SM의 개수로 형성할 수 있는 출력전압의 파형은 최소의 고조파를 함유한다는 것이다. 그러므로 그림 2에서  $\theta_6$ 은 아래의 수식을 통해서 결정할 수 있다. 수식 (1)은 두 개의 빗금 친 면적을 적분을 통해서 구하고 이때 면적이 같다면 두 개의 적분을 비교한 값은 0이 된다.

$$\int_{\Theta_B}^{\Theta_6} (m_a \sin \Theta - B) d\Theta - \int_{\Theta_6}^{\Theta_A} (A - m_a \sin \Theta) d\Theta = 0$$

(1)

수식 (2)는 수식 (1)의  $\theta_6$ 를 좌항에 놓고 정리한 것이다.

$$\Theta_{6} = \frac{A\Theta_{A} \quad B\Theta_{B} + m_{a}\cos\Theta_{A} \quad m_{a}\cos\Theta_{B}}{A \quad B} \quad (2)$$

수식 (2)에서  $\theta_A$ 와  $\theta_B$ 는 수식 (3)을 통해서 구할 수 있다.

$$\Theta_A = \sin^{-1} \frac{A}{m_a} \Theta_B = \sin^{-1} \frac{B}{m_a}$$

(3)

수식 (2)를 일반화 정리하면 수식 (4)와 같다. 여기서 M은 arm을 구성하는 SM의 개수를 의미한다.

$$\Theta_{n} = (n \Theta_{n/M} \quad (n \quad 1) \Theta_{(n-1)/M})

+ M m_{a} (\cos \Theta_{n/M} \quad \cos \Theta_{(n-1)/M})$$

(4)

$$(n=1,2,\ldots,n \ A=\frac{n}{M} \ B=\frac{n-1}{M})$$

## 2.3 Sub-Module 직류전압 불평형 억제 알고리즘

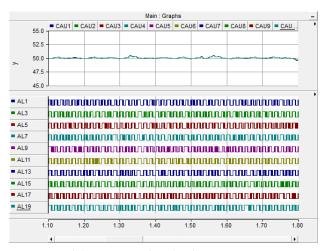

MMC의 phase module은 상·하단 arm으로 구성이 되어 있으며, 각 arm은 SM이 직렬로 연결되어 구성된다. 각 SM은 두개의 IGBT와 직류 커패시터로 구성이 되어 있다. MMC의 SM은 사인에 가까운 출력전압을 형성하기 위해서 적절한 출력전압 폭을 형성해야 하며, 이때 모든 SM의 커패시터 전압크기는 동일한 값을 일정하게 유지해야한다. 만약 각 SM 커패시터의 전압크기가 달라지게 되면 MMC는 사인에 가까운 출력전압을 형성할 수 없게 된다. 그러므로 각 SM 커패시터의 직류전압에 불평형이 발생하지 않도록 이를 억제하는 알고리즘이 필요하다. 본 논문에서는 Sorting Algorithm을 적용하여 제어주기마다 각 arm의 SM 직류 전압크기에 따라 SM의 ON/OFF상태제어를 수행하였으며, 이를 통해 모든 SM의 직류 전압을 일정 값으로 제어하였다. 그림 3은 상단 arm SM 커패시터 전압과 gate pulse이다.

그림 3 상단 arm SM 커패시터 전압과 gate pulse

Fig. 3 Upper arm SM capacitor voltage and gate pulse

#### 2.4 유ㆍ무효 전력제어

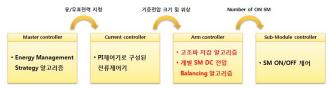

그림 4는 3상 11 level MMC의 전체 제어기 구성과 적용 알고리즘을 나타낸 것이다. 전체제어기는 상·하위 제어기로 구성되어 있으며, 최상위 제어기인 Master Controller는 Energy Management Strategy 알고리즘으로 구성되어 있으면 유/무효 전력의 지령을 출력한다. 하위제어기들은 상위제어기에서 생성한 지령을 받아서 알고리즘에 적용하여 적절한 동작을 수행하도록 하였다.

그림 4 상단 arm SM 커패시터 전압과 gate pulse

Fig. 4 Upper arm SM capacitor voltage and gate pulse

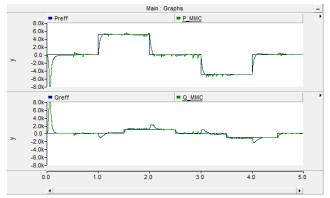

그림 5는 3상 11 level MMC의 유·무효전력제어 동작을 PSCAD프로그램으로 시뮬레이션한 결과파형이다. 유효전력을 5kW에서 5kW로 양방향 제어하였으며, 무효전력은 지상동작과 진상동작을 수행하였다. 또한 시뮬레이션 결과를 통해서유·무효전력의 독립제어를 확인하였다.

그림 5 유.무효전력제어

Fig. 5 Active and reactive power control

#### 3. 결 론

본 논문에서는 모듈형 멀티레벨 컨버터의 동작원리를 알아보고 출력파형의 고조파를 저감하는 모듈레이션 방법과 각 모듈의 직류전압 불평형을 해소하는 알고리즘을 제안하였다. 또한 그 타당성을 PSCAD 소프트웨어를 이용한 시뮬레이션으로 검증하였다.

이 논문은 지식경제부의 에너지인력양성사업의 지원으로 명지대학교 에너지기술인력양성센터를 통해서 수행되었습 니다.

## 참 고 문 헌

- [1] E. Solas, G Abad, J. A. Barrena, A. Carcar, S. Aurtenetxea, "Modelling, Simulation and Control of Modular Multilevel Converter", accepted to EPE PEMC2010

- [2] B. Han, S. Baek, H. Kim, G. Karady, "Dynamic Characteristic Analysis of SSSC Based on Multibridge Inverter", IEEE Transaction on Power Delivery, Vol. 17, NO. 2, April 2002