# 고성능 LDC용 최적 자성소자 개발을 위한 Test Platform

오창열, 김윤성, 이영달, 이병국\* 성균관대학교 정보통신대학

## Test Platform for the Development of Optimized Magnetic Devices in High-Performance LDC

Chang Yeol Oh, Yun Sung Kim, Young Dal Lee, and Byoung Kuk Lee\* College of Information & Communication Engineering, Sungkyunkwan University

#### **ABSTRACT**

본 논문에서는 차량용 저전압 DC DC 컨버터 (Low voltage DC DC Converter, LDC)에 최적화된 자성소자를 개발하기 위한 Test Platform 구축 과정을 제시한다. 현재 연구, 개발된 LDC를 토대로 자성소자 개발에 범용성을 가지는 정격사양을 결정하고 그에 따른 시스템을 구성한다. 또한 시스템에 적용된 위상천이 풀 브리지 (Phase Shift Full Bridge, PSFB) 컨버터에서 자성소자가 미치는 영향을 분석한다. 분석 결과를 기반으로 구성한 시스템에서 안정적인 성능 검증을 위한 자성소자의 적정 설계범위를 제시하고, 범용성을 위해 입출력 변화에 따른 자성소자 설계 요소들의 변화 추이를 제시한다.

#### 1. 서 론

최근 친환경 차량에 대한 연구의 확산으로 xEVs에 적용되는 전장부하가 증가하고 있다. 이로 인하여 차량 내 탑재되는 LDC의 고효율, 고성능화가 요구되고 있다.[11] LDC의 고효율 및 고성능화를 위하여 PSFB와 같은 공진 토폴로지의 적용이 늘어나는 추세이며, 이러한 공진 토폴로지들은 변압기와 같은 자성소자들이 효율 및 성능에 많은 영향을 받는다. 또한 LDC는차량 내 탑재되기 때문에 시스템 전반에서 가장 큰 부피를 차지하는 자성소자의 최적설계가 크게 요구되고 있다.[12]

이러한 자성소자들은 각각의 LDC 시스템이 개발되는 과정에서 최적화되어 적용되지만, 자성소자 개발의 측면에서는 사이즈, 권선 및 재질 등 다양한 요소들을 고려할 필요가 있다. 또한 각각의 시스템에 따라 달라지는 사양에 대응 가능한 자성소자 개발을 위해서 다양한 입출력 조건 및 부하에 대응 가능한 범용 LDC 시스템이 필요하다.

그러므로 본 논문에서는 PSFB가 적용되어 설계된 범용 LDC 시스템을 기반으로 한 고성능 LDC용 최적 자성소자 개 발을 위한 Test Bed를 구성한다. 또한 구성한 시스템에서 자 성소자에 따른 영향을 분석하고, 안정적인 성능 구현을 위한 적정 설계범위를 제시하여 Test Platform을 구축한다.

### 2. 시스템 설계 및 적용

#### 2.1 하드웨어 설계

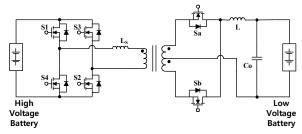

넓은 입출력 조건 및 자성체의 변화에 따른 영향에 강건해 야하는 고성능 범용 LDC를 구현하기 위해서, 그림 1과 같이

그림 1 범용 IDC 시스템 토폴로지

Fig. 1 System configuration of General LDC System

차량용 LDC에 일반적으로 적용되는 풀 브리지 구조와 센터 탭 동기 정류기를 갖는 PSFB 컨버터를 선택한다.[1],[3]

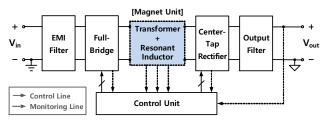

고성능 LDC의 최적 자성소자 개발을 위한 Test Platform은 선택한 토폴로지를 통해 개별 LDC의 다양한 입출력 조건에서 원활하게 동작할 수 있도록 설계되어야 한다. 뿐만 아니라 설계된 자성소자들을 원활히 적용 가능하고, 자성체 이외의 외부영향을 최소화 시킬 수 있는 구조를 필요로 한다. 그림 2는 제안한 시스템의 구조를 나타내며 EMI 필터, PSFB 컨버터 및확장 및 응용이 용이한 독립 자성소자 유닛으로 구성된다.

LDC 시스템은 차량에 실장 되기 때문에 하드웨어의 부피를 최소화하기 위하여 효율과의 트레이드오프를 고려한 100kHz로 스위칭 주파수를 선정한다. 주요 입출력 파라미터는 차량용 배터리의 고 전압화 및 부하인 납축전지의 충전영역을 고려하여표 1과 같이 선정한다.[1]

구성한 하드웨어의 1차 측 풀 브리지는 최대 입력전압 400V에 마진을 두고, 공진 전류의 최대치에 전류 마진을 포함한 600V/47A급 MOSFET를 선정한다. 또한 2차 측 센터 탭동기 정류기에는 출력 전압 최대치의 2배에 마진을 포함하고, 최대 출력 전류를 고려한 40V/180A급 MOSFET를 사용한다.

그림 2 LDC용 자성체 Test Platform 블록 다이어그램

Fig. 2 Block Diagram of Test Platform for Magnetic Devices in LDC

표 1 시스템 파라미터 Table 1 System Parameters

| Parameter | Value [Unit]               | Parameter | Value [Unit]               |

|-----------|----------------------------|-----------|----------------------------|

| 정격 출력     | 2 [kW]                     | 출력 전압     | 12 14.5 [V <sub>dc</sub> ] |

| 입력 전압     | 240 400 [V <sub>dc</sub> ] | 스위칭 주파수   | 100 [kHz]                  |

#### 2.2 자성소자의 영향

Test Platform의 안정적인 성능을 위해서 자성소자가 시스템에 미치는 영향을 고려해야 한다. PSFB 컨버터는 ZVS로 인하여 부하의 범위는 누설 인덕턴스  $L_{lk}$ 와 함께 증가한다.  $L_{lk}$ 의 증가는 변압기를 통해 2차 측으로 전압이 전달되는 유효 듀티  $D_{eff}$ 의 감소로 이어진다. 이러한 관계를 고려하면서 최대 제어를 고려하여 최대 듀티  $D_{MAX}$ 를 0.85로 놓고 변압기의 권선 비  $N_{T}$ 는 식 (1)과 같이 표현된다. (2)0  $V_{RDSON}$ 은 FET에서 발생하는 전압 강하로 스위치의  $V_{RDSON}$ 과 입력 전류를 고려하여  $V_{RDSON}$ 가 장한다. 또한 변압기를 통한 에너지 전달을 위한 자화 인덕턴스는 평균 듀티  $V_{RDSON}$ 와 급플 허용치를 이용하여 식 $V_{RDSON}$ 의 라를 하용치를 이용하여 식 $V_{RDSON}$ 의 다른 한다니어진다.

$$N_{T} = \frac{N_{P}}{N_{S}} = \frac{(V_{in(MIN)} - 2 \times V_{RDSON}) \times D_{MAX}}{V_{OUT} + V_{RDSON}} \tag{1}$$

$$L_{\scriptscriptstyle M} \geq \frac{V_{\scriptscriptstyle IN} \times (1-D_{\scriptscriptstyle AVG})}{\Delta I_{\scriptscriptstyle Lout} \times 0.5} \times f_{\scriptscriptstyle sw} \tag{2}$$

또한 PSFB 제어에 필요한 공진 인덕터  $L_S$ 는 스위치의 기생 커패시터  $C_{OSS}$ 의 에너지를 감소시키면서 이를 이용하여 넓은 부하구간에서 ZVS가 가능하도록 식 (3)으로 표현된다. [3]

$$L_{S} \ge (2 \times C_{OSS}) \frac{V_{in(MAX)}^{2}}{\left(\frac{I_{peak}}{2} - \frac{\Delta I_{Lout}}{2N_{T}}\right)}$$

(3)

## 2.3 자성소자 설계범위

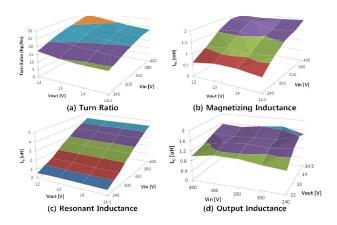

하드웨어의 동작 범위를 토대로 제시한 설계 파라미터들의 변화를 분석하여 Test Bed에 적용 가능한 자성소자의 설계범 위를 제시함으로써 Test Platform을 구축한다. 표 1에 제시한

그림 3 입출력 조건에 따른 설계 파라미터 변화

Fig. 3 Spread of Design Parameter by input & output

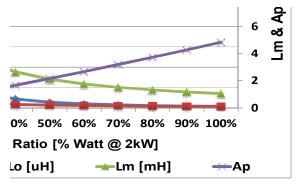

그림 4 부하율에 따른 설계 파라미터 변화

Fig. 4 Spread of Design Parameter by load ratio

입출력 조건의 변화에 따른 주요 설계 파라미터들의 변화는 그 림 3과 같이 확인할 수 있다.

뿐만 아니라 다양한 LDC의 사양에 대응키 위하여 하드웨어의 정격 출력인 2kW (300V/14V) 기준으로 부하의 변동에 따른 자성소자 설계 파라미터 변화를 그림 4와 같이 확인한다. 이를 통해서 각각의 개발 목표에 부합하는 자성소자의 설계 및 구축한 Test Platform에 적용 가능한 범위를 보인다. 또한 이결과를 토대로 주 동작 영역에 최적화된 자성소자의 설계 역시가능하다.

## 3. 결 론

본 논문에서는 2kW급 PSFB가 적용된 범용 LDC 시스템을 기반으로 한 고성능 LDC용 최적 자성소자 개발을 위한 Test Platform 구축에 대하여 기술하였다. 자성소자 Test를 위한 하드웨어 설계를 수행하고, 시스템에 자성소자가 미치는 영향을 분석하였다. 이를 토대로 자성소자 설계 파라미터를 기반으로 적용 가능한 자성소자의 설계범위를 제시함으로 Test Platform을 구축하였다. 주 운전영역을 바탕으로 설계점을 도출하고 다양한 사이즈의 코어 특성이 반영된 자성체 설계를 통해 최적화된 자성체 개발이 가능할 수 있으리라 기대한다.

## Acknowledgment

본 연구는 한국산업기술평가원 지원 하에 수행된 우수제 조기술연구센터사업 (No. 10038825)의 연구결과입니다.

## 참 고 문 헌

- [1] M. Pahlevaninezhad, J.Drobnik, P. Jain, and A. Bakhshai, "A Load Adaptive Control Approach for a Zero Voltage Switching DC DC Converter used for Electric Vehicles," IEEE Trans. Ind. Electron., vol.59, no.2, pp.920 933, Feb. 2012.

- [2] J. G. Lim and S. K. Chung, "Digital Control of Phase Shifted Full Bridge PWM Converter," KIPE, JPE, vol.8 no.3, pp.201 292, Jul. 2008.

- [3 Texas Instruments [Online].

"UCC28950 600W, Phase Shifted, Full Bridge Application Report", Oct. 2010.

http://www.ti.com/litv/ug/sluu421a/sluu421a.pdf