# Cascade Buck-Boost 컨버터의 스위치 듀티와 위상변화에 따른 최적 효율분석

김옥진, 김동희, 김민중, 이병국\* 성균관대학교 정보통신대학

# Optimal Efficiency Analysis on the Cascade Buck-Boost Converter according to the Switch Duty and Phase Variation

Og Jin Kim, Dong Hee Kim, Min Jung Kim, and Byoung Kuk Lee\* College of Information & Communicati on Engineering, Sungkyunkwan University

#### **ABSTRACT**

본 논문에서는 Cascade buck boost 컨버터 토폴로지에서 인덕터 전류 리플 손실을 감소시켜 효율 향상시키는 최적 스위칭 방법을 제시한다. 효율을 높이기 위한 최적 스위칭 방법은 다양한 방식으로 듀티크기와 위상을 변화시켜 인덕터 전류 리플로 인해 발생하는 손실을 비교하여 최소화하는 방식을 채택한다. 또한, 제시된 방법은 100W급 Test bed를 통해 타당성을 검증한다.

## 1. 서 론

화석연료의 고갈로 인해 각광받고 있는 신재생 에너지 분야는 넓은 입출력 범위, 고효율을 만족하는 DC DC 컨버터의 필요성이 증가하고 있다. 승강압의 비절연형 DC DC 컨버터에서는 Cascade buck boost의 사용이 증가하고 있으며, Cascade buck boost를 사용 시 스위치의 On/Off에 따라 입력전류가 들어가는 구간이 달라져 인덕터 전류 리플에 의한 손실도 다양하게 발생한다.

본 논문에서는 다양한 듀티 크기에 따라 달라지는 인덕터전류 리플 손실들을 최소화 하는 방법을 제안한다. 제안한 방법은 입출력 전압 전달비가 1에 가까울 때 스위치가 동시 On되는 구간이 발생하여 인덕터 전류의 큰 상승 또는 하강 기울기를 가질 경우 스위칭의 듀티 크기와 위상을 가변시켜 인덕터전류의 기울기를 완만하게 만들어 전류 리플을 감소시키는 방법이다. 이에 따라 인덕터 전류의 최대치를 감소시켜 효율을증가시킨다. 제안된 방법은 시뮬레이션과 100W급 Test bed를통해 타당성을 검증한다.

# 2. 스위칭 기법 분석

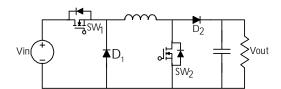

그림 1에는 본 논문의 토폴로지인 Cascade buck boost 컨버터 나타낸다. Cascade buck boost 컨버터 스위칭의 듀티 크기와 위상조건에 따라서 SW1 On, SW2 On, SW1,2 동시 On, SW1,2 동시 Off 구간이 발생하며 구간마다 인덕터 전류 기울기가 달라진다.

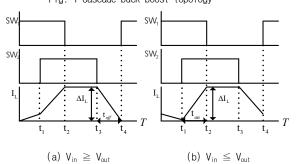

그림 2 (a)와 같이  $V_{in}$ 이  $V_{out}$ 보다 큰 경우에는  $SW_1$  On구간에서는 인덕터에  $V_{in}$ 와  $V_{out}$ 의 차이만큼의 전압이 걸려 인덕터 전류의 기울기가  $SW_{12}$  동시 On이 되는 구간에 비해 상대

그림 1 Cascade buck-boost 토폴로지 Fig. 1 Cascade buck-boost topology

그림 2 스위칭 방법에 의한 인덕터 전류 리플 Fig. 2 Inductor current ripple by switching method

적으로 완만하게 상승하고,  $SW_{1,2}$  동시 On이 되는 구간에서는 전압  $V_{in}$ 이 걸려 인덕터 전류의 기울기가 상대적으로 크게 상승한다.  $SW_2$  On구간에서는 순환전류가 흐르며,  $SW_{1,2}$ 가 동시 Off 되는 경우에는 전압  $V_{out}$ 만큼 기울기가 하강한다. 그림 2 (a)와 반대로  $V_{out}$ 이  $V_{in}$ 보다 큰 경우에는  $SW_1$ 이 On이 된 구간에서  $V_{in}$ 에서  $V_{out}$ 을 빼준 만큼의 전압이 걸리지만 인덕터 전류 기울기는 하강한다 $^{(1)}$ .

인덕터 전류 리플을 감소하기 위해 스위치의 듀티 크기 또는 위상을 가변시켰을 경우를 적용한 전압전달비식은 입출력 전압전달비와 인덕터 전압의 Volt Sec 평형조건을 이용하여 식을 도출하며, 전압 전달비의 식은 입출력전압조건에 따라 두 가지의 식으로 도출한다.

$$\frac{V_{OUT}}{V_{\in}} = \frac{t_1 - t_3 + t_4}{t_2} \ \left( V_{\in} \le V_{OUT} \right) \eqno(1)$$

$$\frac{V_{OUT}}{V_{\in}} = \frac{t_2}{t_1 - t_3 + t_4} \ (V_{\in} \ge V_{OUT}) \tag{2}$$

입출력 전압조건에 따라 도출된 식 (1), (2)와 인덕터의 전류 기울기를 일정하게 가지는 구간을 통해 인덕터 전류 리플 식을 도출한다.  $V_{in}$ 이  $V_{out}$ 보다 큰 경우 그림 2 (a)와 같이 일정하게 하강하는 기울기를 가진 구간인 t3부터 t4까지의 구간을 이용하여 전류 리플을 구한다. 반대로  $V_{out}$ 이  $V_{in}$ 보다 큰 경우에는 그림 2 (b)와 같이 일정하게 상승하는 기울기를 가진 구간인 t1부터 t2까지를 통해 인덕터 전류 리플을 구한다. 식 (3)은 이를 통해 도출된 인덕터 전류 리플 식이다. 여기서 ton,off는 그림 2의 일정한 인덕터 기울기의 시간을 의미한다.

$$\Delta I_{L} = \frac{V_{L} \times t_{on,off}}{L} \tag{3}$$

# 3. 시뮬레이션 및 실험을 통한 검증

## 3.1 입출력 구간이 적을 경우에 나타나는 문제점

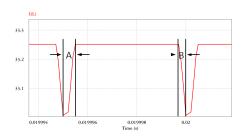

도출한 수식과 시뮬레이션을 통해 나타난 인덕터 전류 리플 값을 확인하는 과정에서 인덕터 전류값이 그림 3과 같이 매우 큰 경우가 발생하였다.

그림 3 인덕터 순환전류 Fig. 3 Inductor Circulating Current

그림 3의 조건은 SW<sub>1</sub>의 듀티는 0.1, SW<sub>2</sub>는 0.9로 도통시켜 며 두 스위치의 위상을 15도를 지연시켜준 시뮬레이션이다. 전류가 들어가는 A구간과 전류가 나오는 B구간이 매우 좁고 순환전류가 흐르는 구간이 매우 큰 경우이다. 필요로 하는 전류를 SW<sub>1</sub>이 도통되는 짧은 시간 안에 모두 인가해야하기 때문에 전류는 급격히 증가한다. 그리고 SW<sub>2</sub>가 도통되는 순환구간에서는 소비하지 않다가 SW<sub>1,2</sub>가 모두 Off가 되는 짧은 시간 안에 저장되어 있던 전류를 모두 방출해야 한다. 이렇게 SW<sub>1</sub>이 매우 작은 경우에는 높은 전류를 가지게 되어 인덕터 전류 최 댓값이 커지므로 SW<sub>1</sub>의 도통구간은 1/3이상 열어주어야 그림 3과 같이 높은 전류가 흐르는 것을 방지할 수 있다.

#### 3.2 실험을 통한 검증

설명한 사실을 검증하기 위해 100W급 Test bed를 통해 실험하였다. 실험은 입력전류 34V, 인덕터는  $34.5\mu$ H, 스위칭 주파수는 50kHz, 스위치는 IPP120N06N을 사용하였다. 또한 그림3과 같은 문제가 발생하지 않도록  $SW_1$ 의 듀티 크기를 1/3이상도통시켜 준 상태 실험을 진행하였다.

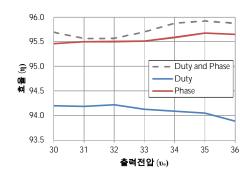

위와 같은 실험 조건으로 Test bed를 구성하여 Yokogawa 사의 WT 3000으로 그림 5의 효율을 측정하였다. 스위칭 듀티의 크기와 위상을 같이 변화시킬 경우 듀티만 가변할 경우와 위상만 가변할 경우보다 효율이 가장 증가한 것을 확인하였다. 이는 인덕터 리플 크기를 적절하게 성형할 수 있기 때문에 인덕터에 흐르는 전류크기와 리플을 줄일 수 있어, 각각의 소자의 전류 스트레스를 크게 줄일 수 있기 때문이다.

(a) 듀티크기 변화

(b) 듀티크기, 위상 변화

그림 4 실험결과

Fig. 4 Experimental results

그림 5 스위칭 크기와 위상에 따른 효율 Fig. 5 Efficiency of conform to Switching Duty, Phase

# 4. 결 론

본 논문에서는 입출력 전압전달비가 1에 가까울 때 인덕터 전류 기울기가 급격한 상승 또는 하강구간을 가지는 영역에서 사용되며, 스위칭의 크기와 위상을 변화시켜 인덕터 전류 리플의 최소화를 통해 효율을 향상시키는 방법을 제안하였다. 100W급 Test bed를 통하여 기존의 방식보다 인덕터 전류 리플의 감소와 증가한 효율 값으로 논문의 타당성을 검증하였으며 이러한 스위칭 방법은 입출력 전압전달비가 1에 가까울 경우에 적용 시에 인덕터 전류 리플 감소와 효율향상을 기대할수 있다.

본 논문은 우수제조기술연구센터사업(10038825)의 연구비 지원에 의하여 연구되었음.

# 참 고 문 헌

[1] X. Ren, X. Ruan, H. Qian, M. Li, Q. Chen "Three Mode Dual Frequency Two Edge Modulation Scheme for Four Switch Buck Boost Converter", *IEEE Transactions On Power Electronics*, Vol. 24, No. 2, pp. 499 509, 2009.