# PCB 설계 SETUP 환경 자동실행으로 L/T 단축에 대한 연구

# 이상호 · 김영길

아주대학교 전자공학과

A study on L/T reduction with the automatic start of SETUP environment designing PCB Sang-ho Lee · Young-gil Kim

#### 요 약

휴대폰 및 카메라 산업의 급속한 발전에 따라 모든 전자 제품이 소형화, 고성능화, 다양화 추세에 따라 PCB도 고집적화, 다층화, 고사양화가 급속히 이루어지고 있다.

현재 계속해서 진화하고 발전하는 디지털 카메라 그 중에서도 DSLR카메라 이외에 소형, 경량화 하는 고객 요구로 부터 탄생한 미러리스 카메라와 하이브리드 디지털 카메라의 시장이 계속해서 증가하고 있다. 그에 고사양, 저전력, 고성능 부품에 따라 PCB설계 난이도가 점차 증가하고 설계 L/T이 오래 걸리고 있다.

본 논문에서는 디지털 카메라 개발기간 및 제조기간 축소에 적용되는 PCB설계 L/T 단축에 대한 방법을 제안한다.

#### **ABSTRACT**

According to the rapid development of cell phone and camera industry, all of electronic products obtain small-size, high-performance and variety. Therefore, PCB also obtains high-integration, multi-layers and high-specification rapidly. Among the digital cameras which are continuously evolved and developed, the market of mirror-less camera and hybrid digital camera is continuously increased because of the customer's request for small-size and weight lightening, except for DSLR camera. Therefore, the difficulty of PCB design is gradually increased and design L/T is longer according to the high-specifications, low-current and high-performance components.

This thesis suggests the method to reduce L/T for PCB design applied to the reduction of digital camera's developing period and manufacturing period.

키워드 PCB 설계, DSLR 카메라 Key word PCB design, DSLR camera

## 1. 서 론

최근 PCB 산업은 2000년대 이후로 통신용 기기, IT장비, 멀티미디어 기기, 네트워크 장치 뿐만 아니라 자동차, 항공기, 가전, 군용등 모든 전자 관련 산업 분야에 필수적인 산업으로 자리매김 하고 있다.

특히 컴퓨터 및 반도체 산업의 급속한 발전에 따라서 모든 전자 제품이 소형화, 고성능화, 고기능화의 추세에 따라서 PCB제품도 그에 따라

고집적화, 미세화, 다층화등 급격히 변화하고 있다. 모든 전자제품의 제조산업의 핵심기술인 PCB설계 기술은 다양한 제품 종류에 따라서 높은 기술수준이 요구되고 있으며 신제품 출시개발기간이 과거와 다르게 빠르게 단축되고 있다. 이에 각 제품군으로 고급 설계 엔지니어들의 확보가 기업 및 PCB제품의 경쟁력 확보를 위해자리 매김한지 오래가 되었으며 PCB설계 난이도가 점차 증가하고 있는 추세이다. 이에 본 논문에서는 디지털 카메라 전체 개발기간 축소에

적용되는 PCB설계 L/T 단축에 대한 방법을 제 시하고자 한다.

### Ⅱ. 본 론

본론에서는 PCB 설계 Process에 대해 설명하 도록 하고 가장 Load가 오래 걸리는 Routing 작업 단축에 대한 방법을 다루도록 하겠다.

그림1. SYMBOL등록

2-1. Symbol 등록 단계는 회로도의 가장 기본이 되는 부품을 도식화하여 세계 공통적으로 이용할수 있도록 등록하는 작업이다. 각 소자에 맞게 Pin수 등록과 도형을 그린 후에 Pin과 도형과 Mapping을 작업을 하는 단계이다.

그림2. 부품등록

2-2. 부품등록 단계에서는 실제 전자 소자 부품을 Catalogue Spec에 맞게 등록하는 작업이다. 각 부품에 맞게 Pin의 가로 세로 사이즈 기입과 실제 부품 높이와 부품 영역에 맞게 작업을 하는 단계이다.

그림3. 회로도 작성

2-3. 회로도 작성 단계에서는 Symbol등록 단계와 부품등록 단계를 한 후에 작업 하는 단계로 각 Symbol연결과 Net name구성 및 Net 연결 작업, 회로도 Error 체크와 Netlist 추출, 각소자 값 변경등 회로에 대한 모든 작업을 하는 단계이다.

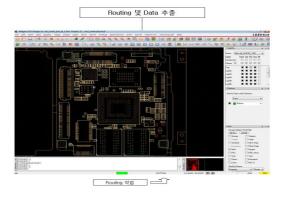

그림4. Routing 및 Data 추출

2-4. Rouing 및 Data 추출 단계에서 부품 배치, Net연결, Gerber Data 추출, 전체 Error체크등 PCB 설계시 가장 시간이 많이 걸리고환경설정이 가장 많은 단계이다.

여기서 가장 L/T이 오래 걸리는 Routing작업 환경설정을 자동화하여 설계 L/T을 단축 시키는 방법을 나타 내고자 한다.

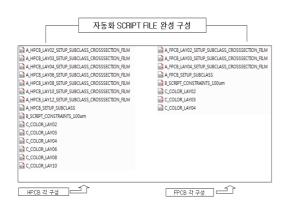

첫 번째로 각 충별 지정이다. 2층, 4층 6층 등 어떤 층이 신규작업으로 될지 모르기 때문에 미리 Setting하고 각 충별 View Layer등을 설정하고 불 필요한 Laer를 삭제하여 설계자가 작업하기 쉽게 Script으 구현하는 것이다.

두 번째로 각 층별 작업 이후 각 환경설정이다. Design의 단위 및 View의 편한 시각적용, 글자 크기 지정, 비속성 라인 두께등 지정하여 Script로 구현한다.

세 번째로 Net의 Constraint의 속성인 Electrical, Physical, Spacing, Same Net Spacing등을 미리 각 충별에 맞게 설정하여 Script로 구현한다.

마지막으로 설계 시작 전 무분별하게 부품, Net, 외형등 여러 가지 Color를 충분히 보기 편하게 구별할 수 있도록 휴먼 Error와 작업 Loss 방지하고자 각 충별 Color를 Script로 구현한다.

그림5. Routing 자동화 Script File 구성도

# Ⅲ. 실험 결과

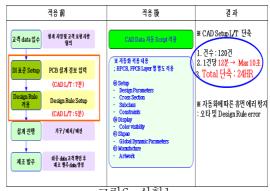

본 논문에서는 PCB설계 L/T 단축을 구현하기 위하여, 삼성전기 제조 CAM 부서와 협업에 데 이터 취합을 하고 최적화 실험을 해 보았다.

그림5와 같이 자동 설정한 Script을 Allegro CAD Tool 시스템에서 구동되었으며, 시간 테스트를 위하여 관련 모델은 제조 및 당사를 이용하였다.

그림6 실험1 항목으로는 CAD Setup, Display, Shape, Manufacture로 4 가지이며, 동일 조건 Computer, CAD Software, CAD 환경으로 시각 측정 방식을 구현하였다.

그림6. 실험1

그림6과 같이 자동화 항목 Load확인 결과 적용 전(12분)과 적용 후(10초)로 Script를 통한설계 Lead Time이 단축되는 것을 알수 있다.

그림7 실험2 항목으로는 ECSetDCF, Relative Propagation Delay, 회로도 Net Name 통일 3가지이며, 동일 조건 Computer, CAD Software, CAD 환경으로 시각 측정 방식 을 구현하였다.

그림7. 실험2

그림7과 같이 자동화 항목 Load확인 결과 1~6번 항목까지 각 240분, 1분, 360분등 Script를 통한 설계 Lead Time이 단축되는 것을 알수 있다.

추가적으로 이러한 자동화 환경 설정으로 인한 시스템 검증으로 휴먼 에러를 Zero에 가깝게 구 현할수 있으며, 고객에게 신뢰를 줄 수 있는 Data를 확보할 수 있다.

### IV. 결 론

Setup 환경설정을 각 파트별 설정하여 Script File을 각 원하는 환경으로 Setting하여 File을 구성하였다. Script File을 Load하여 작업하고 자 하는 PCB 설계시 원하는 작업 Routing에 맞는 기능을 통하여 설계자가 수동으로 사용하지 않고 자동으로 설정 구현하여 설계 Lead Time 단축이 검증되었다.

### 참고문헌

- [1] 미디어브리지, 디지털 카메라 매거진 DCM

- [2] Allegro PCB Designer 김종습, 김무현,

### 저자소개

이상호(Sang-ho Lee)

약력 전자공학과 학사

※관심분야: 디지털 카메라, LCD MoulePCB설계

김영길(Young-kil Kim)

1978. 고려대학교

전자공학과 공학학사

1980. 한국과학기술원

산업전자공학과 공학석사

1984. ENST(프랑스) 공학박사

1984.~현재 아주대학교 전자공학과 교수

※관심분야: 마이크로프로세서응용, 의료공학,

Embeded System