# 디지털 방송 시스템을 위한 효율적인 LDPC 복호기 설계

\*장수현, \*\*서정욱, \*\*김현식, \*\*이연성, \*정윤호 \*한국항공대학교, \*\*전자부품연구원 \*{shjang, yjung}@kau.ac.kr

# Efficient LDPC Decoder for Digital Vedio Broadcasting Systems

\*Soohyun Jang, \*\*Jeongwook Seo, \*\*Hyunsik Kim, \*\*Yeonsung Lee, and ,\*Yunho Jung \*School of ETCE, Korea Aerospace University \*\*KETI (Korea Electronics Technology Institute)

## 요약

In this paper, an area-efficient architecture of LDPC Decoder is proposed for DVB (Digital Video Broadcasting) 2.0 systems. The proposed LDPC Decoder was designed in hardware description language (HDL) and implemented with Xilinx Virtex-5 FPGA. With the proposed architecture, the number of slices for the decoder is 56122 and the number of block RAM is 135.

#### 1. 서론

최근 유럽의 디지털 방송규격인 2.0 계열의 차세대 물리계층은 DVB-T2/S2/C2 (지상파/위성/케이블)로 총 3가지의 전송 방식으로 구성되어 있다. 이들 DVB 2.0 물리계층 송수신 규격의 주된 목적은 이세 가지의 서로 다른 전송 방식의 물리계층 전송 규격을 최대한 공유하는 것이다. 따라서, 위의 세가지 전송방식에 대한 가변 수신 기술은 차세대 지상파, 위성, 케이블 방송의 거대한 시장을 선점할 수 있는 핵심기술로 부각되고 있다 [1].

DVB 2.0 물리계층의 송수신 규격에서는 방송 시스템임을 감안하여, 높은 오류 정정 효과를 위해 BCH (Bose Chaudhuri Hocquenghem) 코드와 LDPC (Low Density Parity Check) 코드를 결합한 Concatenation FEC (Forward Error Correction) 기법을 사용하고 있으며, FEC 블록의 길이에 따라 64800 비트의 normal 프레임과 16200 비트의 short 프레임으로 구분된다 [2].

LDPC 코드는 Gallager가 제안한 선형 블록 부호로써, DVB 2.0 시스템 규격에서는 R(Code Rate)에 따라 패리티 검사 행렬을 M by N 사이즈로 정의한다. 여기서 N은 프레임 길이 이며 M은 N-(R\*N)으로 정의된다. LDPC 복호연산은 패리티 검사 행렬에 의해 이루어지며, check 노드의 행 연산과 variable 노드의 열 연산 간의 반복 되는 복잡한 연산으로 오류 정정 능력을 향상시킨다. 크게 최적의 성능을 보이는 Sum-Product 알고리즘과 표 1에 정리된 것과 같이 하드웨어 구현 복잡도가 낮은 Min-Sum 알고리즘으로 나눌 수 있다. 하지만 이런 높은 오류 정정 효과를 보장하는 LDPC 코드는 부호어 길이가 길어질수록 복호기의 하드웨어 복잡도가 급격히 증가하여 실시간 하드웨어 구현

에 어려움이 있다. 이에, DVB 2.0 시스템 규격에서는 긴 부호어에 의한 복호기의 하드웨어 복잡도 문제를 해결하기 위해, extended IRA(Irregular Repeat Accumulate) LDPC 코드를 이용한다 [3]. eIRA LDPC 코드를 이용하여, 긴 부호어 길이를 가지는 DVB 2.0 시스템에서도 부분 병렬 복호를 통해 하드웨어 복잡도를 상당히 낮출 수 있다.

표 1. Min-Sum 알고리즘

| Step | Min-Sum Algorithm                                                                                                                                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | for $t = 1$ : maxiteraiton                                                                                                                                                                                                  |

| 2    | for $i = 0,1,,n-1$ , initialize $L(q_{ij})$ for which $h_{ij} = 1$                                                                                                                                                          |

| 3    | Check Node Update: $L(r_{ji}) = \left(\prod_{i' \in V_{j \vee i}} \alpha_{i'j}\right) \cdot \min_{i' \in V_{j \vee i}} \beta_{i'j}, \begin{cases} \alpha_{ij} = sign(L(q_{ij})) \\ \beta_{ij} = abs(L(q_{ij})) \end{cases}$ |

| 4    | $Variable\ Node\ Update: L(q_{ij}) = L(c_i) + \sum_{j' \in C_{i \setminus j}} L(r_{j'i})$                                                                                                                                   |

| 5    | $Decision Variable Update : L(Q_i) = L(C_i) + \sum_{j \in C_i} L(r_{ji})$                                                                                                                                                   |

| 6    | $if (t = max iteration) \rightarrow hard - decision :$ $\hat{c_i} = \begin{cases} 1 & \text{if } L(Q_i) < 0 \\ 0 & \text{elsewhere} \end{cases}, (for i = 0, 1,, n-1)$ $end$                                                |

| 7    | end                                                                                                                                                                                                                         |

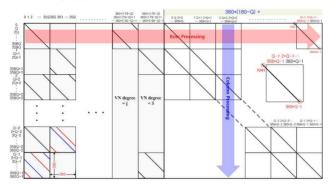

따라서, 본 논문에서는 부분 병렬 복호가 가능한 eIRA LDPC 코드의 특성을 바탕으로 그림 1과 같이 360 기본 단위의 부 행렬로 구성된 패리티 검사 행렬로 재구성하여 분할된 부 행렬 단위로 효율적인부분 병렬 복호를 수행한다 [3]. 또한 DVB 2.0 시스템의 세가지 전송모드를 모두 지원가능하며, 효율적인 부분 병렬 복호 메커니즘을 통한 저복잡도 특성을 갖는 LDPC 디코더의 최적 하드웨어 구조 설계 결과를 제시한다. 여기서, 그림 1은 패리티 검사 행렬에서 1의 성분을 대각선으로 표시하였다.

그림 1. 부분행렬 기반의 변형된 패리티 검사 행렬

### 2. 제안된 LDPC 디코더의 HW 구조 설계 및 구현 결과

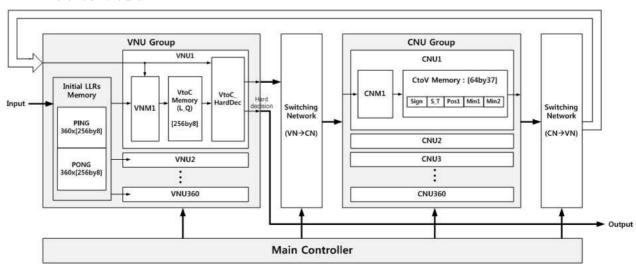

그림 2에서 보듯이, 제안된 LDPC Decoder는 크게 Initial LLRs Processing Module (ILPM), VNU Group Module (VNUGM), CNU Group Module (CNUGM), Switching Network Module (SNM), 그리고 Main Controller로 구성된다. 우선, ILPM에서는 8 bit 단위로 입력되는 intrinsic information 값을 메모리에 저장하게 되고, 반복 복호시마다이 intrinsic information 값을 VNM에 읽어주는 역할을 수행한다. VNUGM과 CNUGM은 Min-Sum 복호기법에 기반하여 각 노드 별 업데이트 연산이 수행되며, 반복 복호를 위해 업데이트된 값을 저장하고 읽기 위해 각각의 로컬 메모리를 가지는 구조이다. SNM은 코드율에 따라 정의되는 edge 연결 방식에 따라, VN과 CN 사이에 메시지를 전달하는 기능을 수행한다. 마지막으로 정해진 최대 반복 횟수의 복호 과정이 완료되면 VtoC\_HardDec 블록에서 결정변수 값을 hard-decision하여 최종 출력한다.

제안된 구조를 적용한 LDPC 디코더는 Verilog-HDL로 설계한 후, Xilinx Virtex-5 XC5VLX330 FPGA에 기반하여 구현되었으며, 표 2는 구현 결과를 보여준다. 그 결과 제안된 구조는 VLX330 FPGA 보드에 약 27%의 slices와 135개의 Block RAM으로 구현 가능함을 확인할 수 있었다.

표 2. 제안된 LDPC 디코더의 FPGA 기반 구현 결과

| LDPC Decoder   | Slices      | Block RAM |

|----------------|-------------|-----------|

| Complexity (%) | 56122 (27%) | 135 (47%) |

#### 3. 결론

본 논문에서는 DVB 2.0 시스템용으로 부분 병렬 복호가 가능한 eIRA LDPC 코드의 특성을 바탕으로 360 기본 단위의 부 행렬로 구성된 패리티 검사 행렬로 재구성해 부 행렬 단위로 효율적인 부분 병렬복호 메커니즘을 통한 저복잡도 특성을 갖는 LDPC 디코더의 최적 하드웨어 구조 설계를 제시하고 구현 및 검증하였다. 제안된 LDPC 디코더의 구조는 차세대 DVB 2.0 시스템에서 활용할 수 있는 최적의 구조로 판단된다.

#### ACKNOWLEDGMENT

본 논문에 사용된 CAD Tool은 IDEC으로부터 지원 받았음.

#### 참고문헌

- [1] 강민구, 백종호, 서정욱, "DVB-C2 시뮬레이터 설계 연구" 한국인 테넷정보학회 제 11권 제2호, pp. 21-27, 2010년, 6월.

- [2] ESTI EN 302 755 V.1.1.1: Digital Video Broadcasting(DVB); Frame structure, channel coding and modulation for a second generation digital terrestrial television(DVB-T2), Sept. 2009.

- [3] C. S. Park, S. W. Kim, and S. Y. Hwang "Design of a Low-area High-throughput LDPC Decoder Using Shared Memory Banks for DVB-S2," IEEE Transactions on Consumer Electronics, Vol. 55, No. 2, pp. 850-854, May 2009.

그림 2. 제안된 LDPC 디코더의 블록 다이어그램