PDP를 위한 SPIDER(Sustainer with Primary sided Integration of DC/DC converter and Energy Reconvery circuit)의 구현 및 시간분할 제어방식

신용생, 박재성, 한상규, 홍성수, 노정욱 국민대학교 전력전자 연구소

Time division control method and implementation of SPIDER(Sustainer with Primary sided Integration of DC/DC converter and Energy Reconvery circuit) for PDP

Yong-Saeng Shin, Jae-Sung Park, Sang-Kyoo Han, Sung-Soo Hong, Chung-Wook Roh Kookmin University Power Electronics Center

### **ABSTRACT**

본 논문에서는 시간 분할 제어방식을 적용한 PDP 전원-구동 통합 시스템을 제안하였다. 제안 시스템은 하나의 전력변환회로를 시간에 따라 다르게 동작시킴으로써, 전원공급기능과무효전력회수기능을 수행한다. 따라서 기존 방식인 전원회로와구동회로를 별개로 사용하는 것에 비해 소자수 및 부피를 줄일수 있으므로 저가형에 매우 적합하다. 본 논문에서는 기존 및제안 시스템의 비교 분석과 실험을 통하여 제안 시스템의 특징및 동작을 검증한다.

# 1. 서 론

고화질 디지털 방송 시대를 맞이하여 PDP(Plasma Display Panel)는 LCD TV 와 더불어 평판형 디스플레이 시장의 양대축을 이루고 있다. PDP는 자발광의 특성을 가지고 있기 때문에 LCD 대비 휘도 및 응답속도가 빠르고, 대형화에 유리한 장점을 가지고 있지만, 최근 LCD TV의 대형화가 급속히 진행되고 LED TV시장이 급성장함에 따라 평판형 디스플레이 시장에서의 입지가 심각하게 위협되는 수준에 이르고 있다. 따라서 관련업계에서는 이를 극복하기 위한 많은 연구를 수행하고 있으며, 특히 원가저감을 통해 시장경쟁력을 확보하려는 노력을 많이 하고 있다[1].

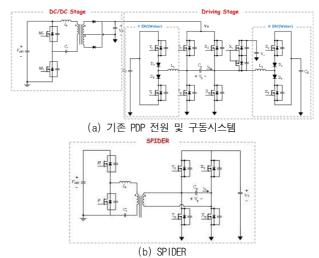

기존 PDP 모듈은 크게 영상을 표시하는 패널, 전원 공급을 위한 전원회로부, 패널구동전압을 X. Y 전극에 인가하기 위한 구동회로부 등으로 나뉜다. 이러한 방식은 패널의 화면표시를 위해 적어도 두 번 이상의 전력 변환(전원회로/구동회로)을 거 치므로, 소비전력이 증가하고 저가의 PDP 구현에 한계가 존재 하는 문제가 있다. [2]는 이러한 문제를 해결하기 위하여 전원 회로부와 구동회로부가 통합된 SPIDER(Sustainer with Primary sided Integration of DC/DC converter and Energy Recovery circuit)를 제안하였으며, 이는 기존 전원회로부의 정 류다이오드 및 구동회로부의 X-Y 전력회수부가 제거될 수 있 으므로 저가의 PDP에 적합한 장점을 갖는다. 하지만 SPIDER 는 Sustain Pulse의 수가 적은 경우 유지전원(Vs)의 제어가 어 려운 단점이 있는데, 실제 PDP는 명암비를 높이고, 소비전력을 최소화 하기 위한 APC(Automatic Power Control)기능을 사용 함으로써, 화면조건에 따라서 유지전원(Vs)의 제어가 잘 이루 어지지 못한다. 따라서 본 논문에서는 이러한 문제점을 극복하기 위한 시간분할 제어방식을 제안한다.

그림 1 기존 PDP 시스템 및 SPIDER Fig. 1 Conventional PDP System and SPIDER

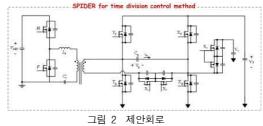

Fig. 2 Proposed circuit

#### 2. 시간분할제어

현재 상품화 되고 있는 PDP의 대부분은 ADS 구동방식을 사용하고 있다. 이는 기본적으로 CRT에서 1개의 화면에 해당하는 1TV-field를 8~11개의 sub-field로 분리하고, 다시 각각의 sub-field를 Reset 구간/Address 구간/Sustain 구간으로 나누어 각 구간에서의 구동전압을 X, Y 전국에 인가하는 방식이다. 이때 기존의 전원공급기능은 전원회로부에 의해 전 구간동안 이루어지며, 무효전력회수기능은 구동회로부에 의해Sustain 구간 동안만 이루어진다. 즉, PDP는 전원공급기능과무효전력회수기능이 필요한데, 기존 방식은 이를 위한 각각의회로가 따로따로 존재함으로써 저가의 PDP를 구현하는데 한계가 존재한다. 반면, 본 논문에서 제안하고 있는 시간분할제어란

하나의 전력변환회로(SPIDER)만을 사용하여 전원공급기능과 무효전력회수기능 수행하기 위하여, Address 구간과 Sustain 구간의 제어를 다르게 하는 방식이다. 제안회로의 구성은 그림 2와 같으며, 변압기 1차측은 기존 SPIDER와 마찬가지로 2개의 스위치(R, F)로 구성되어 있으며, 2차측은 4개의 Sustain 스위치(Ys, Yg, Xs, Xg)와 2개의 Path 스위치(Xr, Xf)가 추가되어 있는 구조이다.

#### 1.1 Address 구간

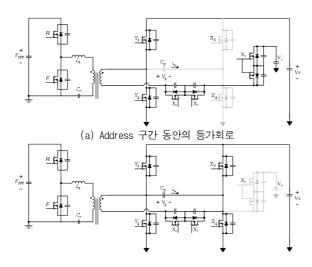

Address 구간동안 제안회로는 그림 3(a)와 같은 등가회로를 갖는다. 이때 제안회로는 2차측이 Voltage Doubler Rectifier로 구성된 LLC converter로 동작하여, 주파수 제어를 통해 전원공급기능을 수행한다. 기존 PDP 시스템의 Ve전압이 약 Vs/2 이므로, 이를 이용하여 정류단 회로를 추가하지 않으면서도 Voltage Doubler Rectifier의 구현이 가능한 장점이 있다.

#### 1.2 Sustain 구간

Sustain 구간동안 제안회로는 그림 3(b)와 같은 등가회로를 갖는다. 이때 제안회로는 변압기의 누설인덕턴스와 패널 캐패 시턴스의 공진을 통하여 무효전력회수기능을 수행한다.

(b) Sustain 구간 동안의 등가회로 그림 3 등가회로 Fig. 3 Equivalent circuit

### 3. 실험결과

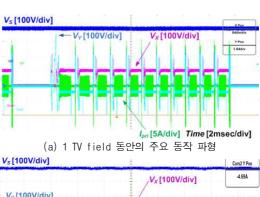

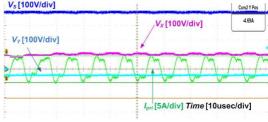

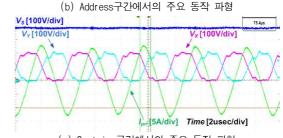

다음은 본 논문에서 제안된 시간분할제어방식이 적용된 SPIDER의 타당성을 검증하기 위한 시작품 제작 및 실험이다. 제안회로의 제어단은 저가형 PWM IC인 TL494 하나만을 사용하여 구현이 가능하며, 이를 이용하여 Address 구간에는 주파수 제어, Sustain 구간에서는 시비율 제어가 가능하다. 실험에 사용된 패널은 삼성 SDI社 의 42 인치 HD PDP 를 사용하였으며, 변압기 턴 비는 3:1, 자화인덕턴스는 160uH, 누설인덕턴스는 20uH, 공진캐패시터는 12nF 이다. 그림 4는 Full White Pattern에서의 주요 동작 파형을 나타내고 있다. 그림에서 알수 있듯이 1TV-field는 총 11개의 sub-field로 이루어져 있으며, 앞에서 설명한 것처럼 Address 구간동안에는 전원공급을위한 LLC converter 동작을 확인할 수 있고, Sustain 구간동안에는 무효전력회수기능을 통한 Sustain 스위치(Ys, Yg, Xs, Xg)의 영전압 스위칭 동작을 확인할 수 있다.

(c) Sustain 구간에서의 주요 동작 파형 그림 4 각 부 주요파형 Fig. 4 Measured waveforms

## 4. 결 론

본 논문에서는 저가의 PDP구현을 위하여, 시간분할 제어 방식을 적용한 SPIDER를 제안하였다. 이는 하나의 전력변환회로(SPIDER)만을 사용하여 전원공급기능과 무효전력회수기능수행하기 위하여, Address 구간동안에는 주파수 제어를 하며 Sustain 구간동안에는 시비율 제어를 하는 방식이다. 제안방식은 기존 전원회로부의 정류다이오드 및 구동회로부의 X-Y 전력회수부가 제거될 수 있을 뿐 아니라, 제조공정이 간소화되는 장점을 갖는다. 이를 확인하기 위하여 42인치 HD PDP를 위한시작품을 제작하여 실험하였으며, 실험결과 제안된 회로는 저가형 PDP에 매우 적합함을 확인하였다.

본 연구는 삼성전기(주)의 연구비 지원과 지식경제부 및 정보통신 연구진흥원의 대학 IT연구센터 지원사업의 연구 결과로 수행되었음 (NIPA-2010-C1090-1021-0005)

# 참 고 문 헌

- [1] Jae-Sung Park, Yong-Saeng Shin, Sung-Soo Hong, Sang-Kyoo Han, and Chung-Wook Roh, "Sustainer with Primary sided Integration of DC/DC converter and Energy Recovery circuit for AC PDP", 2010 전력전자학 술대회

- [2] F. S. Kang, J. H. Park, "Circuit composition of integrating power supply with sustainer of PDP TV." 한 국해양정보통신학회, 추계종합학술대회, pp.242-245, 2007