# 차세대 웨이퍼 생산시스템을 위한 클러스터 툴 디스패칭 알고리즘 개발

허선\*, 이현\*, 박유진\*\*

\*한양대학교 산업경영공학과

\*\*중앙대학교 경영학과

e-mail: hursun@hanyang.ac.kr

# Development of Cluster Tool Dispatching Algorithm for Next Generation Wafer Production System

Sun Hur\*, Hyun Lee\*, Eugene Park\*\*

\*Department of Industrial and Management Engineering, College of Engineering Sciences, Hanyang University

\*\*Department of Business Administration, College of Social Sciences, Chung-Ang University

요 호

차세대 반도체 공정인 450mm 웨이퍼 생산 환경의 가장 큰 특징은 반도체 생산의 전 공정에 대한 완전 자동화이다. 이러한 완전 자동화는 작업자의 공정개입을 불가능하게 하고 개별 웨이퍼의 중요도를 크게 증가시키며 전체 반도체 생산 공정에 대한 견고한 디스패칭 시스템을 필요로 한다. 또한, 차세대 반도체 공정의 디스패칭 시스템은 개별 웨이퍼에 대한 실시간 모니터링과 데이터 수집이 가능해야 하며, 수집된 반도체 공정의 정보를 반영한 실시간 디스패칭이 가능해야 한다. 본 연구에서는 차세대 반도체 환경인 450mm 웨이퍼 생산 환경에서 중요한 역할을 하는 클러스터 툴에 대해 분석하고 클러스터 툴에서 웨이퍼의 작업순서를 결정할 수 있는 디스패칭 알고리즘을 제안한다.

### 1. 서론

반도체 산업에서 웨이퍼의 크기는 10년을 주기로 1.5 배씩 확대되어 왔으며 이는 반도체 산업의 지속적인 수익성 향상과 산업성장의 기반이 되어왔다. 현재 차세대 반도체 환경의 구현을 위한 노력으로 300mm Prime과 450mm Wafer Transition 프로그램이 진행 중 이다. International Semiconductor Manufacturing Initiative(ISMI)의 주도하에 생산성을 향상시킨 차세대 반도체 생산환경의 구현을 위해진행되고 있는 이러한 프로그램들은 궁극적으로 웨이퍼당 비용감소와 사이클 타임의 감소를 목표로 하고 있다.

차세대 반도체 공정의 가장 중요한 이슈이자 차세대 반도체 공장의 핵심 요구사항은 완전자동화(Full Automation)의 실현이다. 반도체 공정의 특성상 작업자의 개입을 최소화하는 것이 생산성의 증대에 직접적으로 연관되어 있고 웨이퍼 크기의 증가에 따라공장 내에서의 웨이퍼 이동과 개별 프로세스에서의

작업자 개입이 어려워질 것으로 예상된다. 그러므로 이러한 반도체 공장의 완전자동화는 차세대 반도체 공정의 실현을 위해 반드시 선행되어야 한다.

완전자동화와 함께 차세대 반도체 공정의 실현을 위해서는 견고한 디스패칭 기법의 개발이 필요하다. 완전자동화가 구현된 반도체 공장에서는 작업자의 개입이 제한되기 때문에 작업 프로세스의 견고한 디 스패칭 방법이 반드시 제시되어야만 한다. 또한 성 공적인 반도체 공장의 완전자동화 실현을 위해서는 다수의 공정을 하나의 장비에 집약시킨 클러스터 툴 (Cluster Tool)과 자동화된 웨이퍼 이송장치가 매우 중요하다. 기존의 반도체 공장은 생산량을 최대화하 기 위해 배치단위(FOUP)의 프로세스로 구성되었으 나 웨이퍼의 크기가 200m에서 300mm로 증가함에 따라 개별 웨이퍼 단위로 프로세스를 구성하는 Single Wafer Processing(SWP) 기술이 등장하였다. SWP에서는 개별 웨이퍼의 저장 및 운송시간을 줄 이는 것이 중요하며 이를 위해 챔버(Chamber) 내에 서 공정이 이루어지는 하나의 장비, 즉 클러스터 툴

을 도입하게 된 것이다.

차세대 반도체 공정에서는 대부분의 공정에 다양한 형태의 클러스터 툴이 적용되어 차세대 반도체 공장의 구현에 더욱 중요한 역할을 할 것으로 예상된다. 그러므로 본 연구에서는 차세대 반도체 공정에서 중요한 역할을 담당하는 클러스터 툴의 특성과구조를 분석하고 클러스터 툴에서의 웨이퍼 작업순서를 결정하는 디스패칭 알고리즘(Dispatching Algorithm)을 제안한다.

#### 2. 클러스터 툴과 관련연구

클러스터 툴은 운송로봇과 고정밀도 클린환경 플랫폼이 기계적으로 결합되고 통합되어 있는 형태의 장비로서 공정에 따라 구성되는 다수의 모듈들로 구성되어 있다. 이러한 클러스터 툴은 최근 반도체 칩생산 Fab에서 매우 중요한 역할을 하고 있다. 현재클러스터 툴은 photolithography, etching, CVD(Chemical Vapor Deposition), PVD(Physical Vapor Deposition), cleaning, thermal processing, photoresist strip 등 반도체 Fab의 거의 모든 공정에 적용되고 있다.

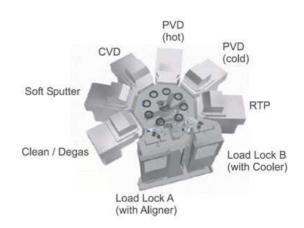

클러스터 툴은 다수의 공정이 하나의 장비에 통합 되어 있기 때문에 저비용, 고효율을 보장할 수 있다. 그림 1은 증착(Deposition) 공정에 필요한 챔버들로 구성된 클러스터 툴을 나타내고 있다. Load Lock A 는 클러스터 툴로 FOUP을 로드하는데 사용되며 각 웨이퍼가 챔버로 진입하기 전에 웨이퍼의 위치를 맞 춰주는 역할을 한다. 증착공정 클러스터 툴에서의 첫 번째 공정인 Clean/Degas 챔버는 cleaning 공정 을 수행하고 필요에 따라 Soft Sputter 챔버에서 etching 공정을 수행한다. 증착공정은 웨이퍼 레시피 (Wafer Recipe)에 따라 CVD, PVD 챔버에서 수행된 다. 마지막으로 필요에 따라 짧은 시간 내에 웨이퍼 온도를 원하는 온도에 맞춰야 하는 RTP(Rapid Thermal Processing) 챔버의 공정을 수 행한다. 모든 공정이 완료된 후에 웨이퍼는 Load Lock B로 이송되고 필요한 온도 수준으로 냉각된다.

[그림 1] 증착공정 클러스터 툴

반도체 칩 생산 환경에서의 클러스터 툴 사용은 통합되지 않은 다른 장비에 비해 공정상의 많은 이 점을 가지고 있다. 기본적으로 민감한 공정을 통합 하고 클러스터 툴 내에서 다양한 환경변수들을 컨트 롤하는 것은 수율과 공정능력 면에서 매우 효율적이 다. 이러한 "mini- environment"는 공정 컨트롤을 용이하게 하고 결함(Defect)을 유발하는 요인들을 제 거함으로써 오염가능성을 줄일 수 있게 해주며 자동 화된 장비에 의한 자동화 공정을 구현함으로써 많은 단계의 공정에서 작업자의 간섭을 줄일 수 있게 해 준다. 또한 대다수의 공정이 이송장치(Transportation Equipment)와 함께 하나의 장비에 통합되 어 있기 때문에 Fab 측면에서 작업공간대비 생산성 을 크게 향상시킬 수 있다.

클러스터 툴은 장비 내에 공정에 따라 구성되는 다수의 챔버를 가진다. 클러스터 툴의 모델링은 수시로 변화하는 웨이퍼 흐름(Wafer Flow)을 반영하고, 공정 후 챔버 내에서의 체재시간을 분석 할 수있어야 하며, 챔버의 재진입(Re-entrant) 공정을 고려할 수 있어야 한다.

Srinivasan[1]은 클러스터 툴의 스케줄링을 위한 방법론으로 페트리넷 모델링을 사용하였다. 이는 엔 지니어로 하여금 반도체 공정상에서 웨이퍼의 흐름 을 이해하는 데에 도움을 주고 장비를 구성하는 다 양한 서브시스템의 복잡한 상호작용을 이해하여 생 영향을 산량의 분석하는데 도움을 주었다 Zuberek[2]은 시간 페트리넷 모델을 이용하여 클러 스터 툴을 모델링하고 클러스터 툴 내에서의 운송로 봇의 형태인 단일 로봇암(Single Robot Arm)과 듀 얼 로봇암(Dual Robot Arm)의 성능을 비교 분석하 였으며 챔버의 재진입 공정을 고려한 웨이퍼 라우팅 모델과 다양한 웨이퍼 프로세싱에 대한 연구를 수행

하였다. Kim 등[3]의 연구에서는 엄격한 시간제약이 존재하는 공정에서의 클러스터 툴 스케줄링 문제를 다루었으며 이들 공정에서 시간제약으로 발생할 수 있는 품질문제를 해결하기 위한 시스템적 방법을 제 안하였다. Lee와 Lee[5]의 연구는 다양한 재진입 웨이퍼 흐름이 존재하는 단일 로봇암 클러스터툴에 대한 스케줄링 문제를 다루었고 페트리넷 모델링 방법을 이용하여 장비동작행태(Tool Operational Behavior)를 모델링하는 방법을 개발하였다. 또한, 최적의 장비동작순서(Tool Operation Sequence)와 스케줄, 사이클타임을 결정할 수 있는 혼합정수계획법모델을 개발하였다.

Kim과 Lee[6]의 연구에서는 모듈 내에서의 웨이퍼지연 제약조건을 만족하는 장비동작스케줄이 존재함을 증명하고 Time Constrained Decision Free Discrete Event System의 schedulability를 정의하는 시스템적 방법을 개발하였다. Wu와 Zhou[7]는 트랙시스템(Track System)에 대한 Real-time Deadlock Free Scheduling 방법으로서 CTROPN(Colored Timed Resource Oriented Petri Net) 모델을 제안하고 실시간 시스템에서 데드락(Deadlock)을 방지할수 있는 휴리스틱 스케줄 생성 룰을 제안하였다.

Mathias Dummler[8]는 반도체 산업에서의 클러스터 툴에 대한 소개와 클러스터 툴 사용에 따른 이점, 성능 모델, 스케줄링 방법 및 이슈 등을 소개하였다. Yves Crama와 Joris van de Kludert[9]는 장비간 이동을 단일 로봇암으로 처리하고 장비 체재시간이 미리 정의된 기간으로 구성되는 Robotic Flow Shop Scheduling 문제를 다루었다. 또한 최소 사이클 타임을 가지는 feasible scheduling을 찾는 것이 strongly NP-comlete임을 증명하였다.

이러한 클러스터 툴의 디스패칭 방법과 관련된 연구들은 디스패칭의 실시간처리가 요구되는 차세대 반도체 환경에는 적합하지 않고 웨이퍼의 챔버 내 체재시간 제약을 고려하지는 않았다. 따라서 본 연 구에서는 클러스터 툴의 실시간 디스패칭이 가능한 알고리즘을 제안하고자 한다.

#### 3. 클러스터 툴 디스패칭 알고리즘

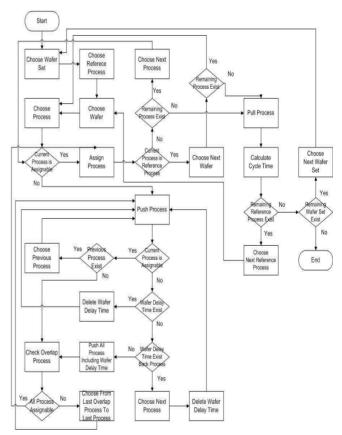

클러스터 툴에서의 최소 사이클 타임을 목적으로 하는 디스패칭 문제는 strongly NP-complete이다[9]. 그러나 차세대 반도체 환경에 적용되는 클러스터 툴 의 디스패칭 알고리즘은 클러스터 툴 장비에 도착하 는 FOUP의 스케줄을 실시간으로 도출할 수 있어야 하고 웨이퍼가 챔버 내에 머무르는 시간제약을 만족시킬 수 있어야 한다. 따라서 본 연구에서는 polynomial time에 제약조건을 만족하는 최소 사이클 타임의 웨이퍼 작업순서를 도출할 수 있는 클러스터 툴 디스패칭 알고리즘을 제안하고자 한다. 그림 2는 이러한 클러스터 툴 디스패칭 알고리즘을 설명하고 있다.

클러스터 툴 디스패칭 알고리즘은 가능한 웨이퍼 작업순서를 모두 고려하여 사이클 타임을 계산하고 이 중 가장 짧은 사이클 타임을 가지는 웨이퍼 작업 순서를 디스패칭 결과로 도출한다. 디스패칭 알고리 즘의 흐름은 표 1과 같다.

여기서 Push Process란 선택된 프로세스가 기존에 배치된 프로세스로 인해 배치될 수 없는 경우 배치가능한 시간대를 찾기 위해 작업을 뒤로 미루는 것을 의미한다. 또한 Pull Process는 각 공정의 유휴시간을 제거하기 위해 각 공정을 앞으로 당겨주는 것을 말한다. 클러스터 툴 디스패칭 알고리즘의 계산량은 웨이퍼 개수를 M, 공정의 수를 K이라고 했을 때 O(M!K)이다.

[그림 2] 클러스터 툴 디스패칭 알고리즘

[표 1] 클러스터 툴 디스패칭 알고리즘의 흐름

| No | Algorithm                                      |

|----|------------------------------------------------|

| 1  | 가능한 모든 웨이퍼 작업순서 선정                             |

| 2  | 선택된 경우의 웨이퍼 작업순서에 따른 웨이퍼 우선순위<br>결정            |

| 3  | 기준이 되는 레퍼런스 공정 선택                              |

| 4  | 웨이퍼 우선순위에 따라 작업순서 결정                           |

| 5  | 웨이퍼 작업시간과 웨이퍼 지연시간을 포함하여 작업을<br>배치             |

| 6  | 겹치는 작업은 가능한 시간대로 재배치(Push Process)             |

| 7  | 모든 웨이퍼의 작업이 배치되면 각 공정의 유휴시간을 제거(Pull Process)  |

| 8  | 모든 공정을 레퍼런스 공정으로 선택한 경우 다음 웨이퍼<br>작업순서의 경우를 선정 |

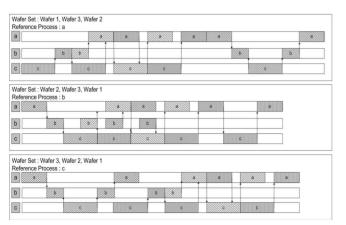

그림 3은 클러스터 툴 디스패칭 알고리즘을 통해 도출된 웨이퍼 작업순서의 예제 결과를 나타내고 있다. 예제는 세 장의 웨이퍼와 세 종류의 프로세스를 가정하였으며 각 프로세스의 작업처리시간과 프로세 스별로 가능한 웨이퍼 지연시간은 표 2와 같다.

[표 2] 디스패칭 알고리즘 예제 파라메타

| Process | Processing time | Wafer Delay |

|---------|-----------------|-------------|

| a       | 3분              | 1분          |

| b       | 2분              | 1분          |

| С       | 4분              | 1분          |

그림 3에서 웨이퍼 작업순서가 웨이퍼 1, 웨이퍼 3, 웨이퍼 2이고 레퍼런스 공정이 a인 경우가 사이클 타임이 가장 길고 웨이퍼 2, 웨이퍼 3, 웨이퍼 1 이고 레퍼런스 공정이 b인 경우가 사이클 타임이 가장 짧은 것을 알 수 있다.

[그림 3] 클러스터 툴 디스패칭 알고리즘 예시

본 연구에서 제안한 클러스터 툴 디스패칭 알고리 즘은 차세대 반도체 환경의 요구사항인 클러스터 툴 의 실시간 디스패칭 알고리즘을 제공하고 웨이퍼의 챔버 체재시간의 제약조건을 만족하는 최소 사이클 타임의 웨이퍼 작업순서를 제공한다.

#### 4. 결론

차세대 반도체 환경에서 반도체 공정의 완전자동화가 중요해짐에 따라 클러스터 툴의 역할이 크게증가하고 클러스터 툴의 효과적인 디스패칭 방법이요구되고 있다. 이에 본 연구에서는 클러스터 툴의특성 및 제약조건을 분석하여 실시간 디스패칭이 가능한 디스패칭 알고리즘을 제안하였다.

본 연구에서 제안한 디스패칭 알고리즘은 클러스터 툴 장비에 웨이퍼 FOUP이 도착한 이후 실시간으로 웨이퍼 작업순서를 결정할 수 있으며 웨이퍼가챔버 내에 머무를 수 있는 시간 제약을 고려하였다. 추후 polynomial time에 최적 솔루션을 제공할 수 있는 개선된 클러스터 툴 디스패칭 알고리즘에 대한연구가 필요하다.

## 참고문헌

- [1] R. S. Srinivasan, "Modeling and Performance Analysis of Cluster Tools Using Petri Nets," *IEEE Transaction on Semiconductor manufacturing*, Vol. 11, No. 3, pp.394–403, 1998

- [2] Wlodek M. Zuberek, "Timed Petri Nets in Modeling and Analysis of Cluster Tools," *IEEE Transaction on Semiconductor Manufacturing*, Vol. 17, No. 5, pp.562–575, 2001.

- [3] Ja-Hee Kim, Tae-eog Lee, Hwan-yong Lee, Doo-byeong Park, "Scheduling Analysis of Time-constrained Dualarmed Cluster Tools," *IEEE Transaction on Semiconductor Manufacturing*, Vol. 16, No. 3, pp521-534, 2002

- [4] M. H. Matcovschi, C. Mahulea, O. Pastravanu, "Petri Net Toolbox for MATLAB," 11th Mediterranean Conference on Control and Automation MED '03, Rhodes, Greece, 2003.

- [5] Hwan-yong Lee, Tae-eog Lee, "Scheduling Single-armed Cluster Tools with Reentrant Wafer Flows," *IEEE Transaction on Semiconductor Manu- facturing*, Vol. 19, No. 2, pp.226-240, 2006.

- [6] Ja-Hee Kim, Tae-eog Lee, "Schedulability Analysis of Time-constrained Cluster Tools with Bounded Time Variation by an Extended Petri Net," *IEEE Transaction on Semiconductor Manufacturing*, Vol. 5, No. 3,

- pp.490-503, 2008.

- [7] Naiqi Wu, MengChu Zhou, "Real-time Deadlock-free Scheduling for Semiconductor Track Systems Based on Colored Timed Petri nets," OR Spectrum, Vol. 29, pp.421-443, 2007.

- [8] Mathias Dummler, "Modeling and Optimization of Cluster Tools in Semiconductor Manufacturing", Ph.D. dissertation, University of Wuerzburg, 2004.

- [9] Crama. Y, van de Klundert, "Robotic Flowshop Scheduling is Strongly NP-complete", Ten Years LNMB, W.K. Klein Haneveld, O.J. Vrieze and L.C.M. Kallenberg (eds.), CWI Tract 122, Amsterdam, The Netherlands, pp. 277–286, 1997.