# LDO 레귤레이터의 PSRR 특성개선

유재영\*, 방준호\*, 유인호\*, 이우춘\* 소병문\* 김송민\* \*전북대학교 IT응용시스템공학과 e-mail:jaeyoung1-@jbnu.ac.kr

# The PSRR improvement of the LDO Regulator

\*Jae-Young Yu, \*Jun-Ho Bang, \*In-Ho Ryu, \*Woo-Choun Lee, \*Byung-Moon So \*Song-min Kim

\* Dept of IT Applied System Engineering, Chonbuk National University

요 약

본 논문에서는 LDO레귤레이터의 PSRR을 향상 및 전압가변 조정이 가능한 능동 Replica LDO 레귤레이터를 설계하였다. 일반적인 레귤레이터의 PSRR과 회로의 안정성 확보를 위해서 사용된 Replica회로의 경우, 안정된 동작을 유지하기 위해서는 DC 매칭이 이루어져야 한다. 본 논문에서는 능동 Replica LDO회로를 제안하였다. 제안된 회로는 CMFB회로에 의하여 DC 전위의 매칭이 이루어지도록 하였으며, 레귤레이터의 출력전압도 일정한 범위내에서 조정이 가능하다. 또한 HSPCIE시뮬레이션 결과, 제안된 능동 Replica LDO회로의 PSRR특성이 기존 LDO구조에 비하여 좋은 결과을 얻을 수 있음을 확인하였다.

## 1. 서 론

디지털과 아날로그 회로의 고 집적화가 가능해 지면서, 동일한 칩상에서 구현될 수 있게 되면서 집적회로의 소형 화와 경량화에 따른 저저압 저전력화에 대한 연구가 계속 되고 있다. 또한 휴대전화, 무선 센서 네트워크, 의료센서, 노트북 컴퓨터등 이동식 전자시스템들은 크고, 작은 배터 리들에 의해 그 동작전원을 얻고 있으며, 장비들은 이러한 구조에 따라 같은 전력으로 얼마나 많은 동작시간을 지속 할 수 있는지 즉 전력소모를 얼마나 줄일 수 있느냐가 그 시스템의 성능을 좌우하게 되었다.[1] 배터리에서 오는 전 압은 변환 효율이 좋은 DC-DC 변환기를 통하여 원하는 전압으로 공급한다. DC-DC 변환회로 중에서도 입력과 출 력전압의 차이를 최대한 적게 하면서, 안정된 전압을 만들 어주는 LDO(Low dropout) 레귤레이터가 많이 사용되고 있다[2] LDO레귤레이터가 고주파 동작시, 공급전원에 의 한 잡음도 광대역에서 발생하게 되므로 광대역 범위내에서 공급전원 잡음에 대한 제거율, 즉 PSRR특성을 최대한 높 은 값으로 확보해야 한다. 그러나, 고주파에서 공급전원 잡 음을 제거하기 위해서는 부하 캐패시터 CL과 큰 부하 전류 공급을 해서 사용된 PMOS에서 발생하는 캐패시터에 의하

여 저주파에서 근접한 두 개의 극점이 발생하여 위상마진 이 나쁘게 되고 안정성에도 문제가 생긴다[3]. 그래서, 두 극점 P1과 P2를 간격을 넓혀 위상마진 충분히 확보하기 위한 방법으로 Miller RC 보상법을 사용하게 되는데, 이 경우 에러 증폭기의 대역폭을 낮추게 되어 중간 주파수 대 역의 PSRR이 나쁘게 된다. 이때도 CL을 증가시켜, 안정성 및 PSRR을 좋게하는데, 소형 고집적화 SOC제작을 위해서 CL의 크기는 제한되어지므로 이 방법도 한계가 있다. 이러 한 부분을 보완하기 위한 또 다른 방법으로 Replica회로를 이용한 방법이 있다. 이 방법은 에러 증폭기와 출력의 Pas s 트랜지스터 사이에, 출력단과 같은 크기의 유사 출력단 을 형성하여 주는 것인데 이 방법으로 LDO레귤레이터의 동작속도를 개선하고 중간대역에서 PSRR특성을 개선할 수 있다. 그러나 이 경우 출력단과 유사 출력단간의 DC전 압의 매칭이 필요한데 본 논문에서는 Replica LDO레귤레 이터의 DC 매칭을 위한 새로운 방법을 제안하고자 한다. 2장에서 일반적인 Replica LDO레귤레이터를 그리고 3장에 서는 제안한 방법에 대하여 간단히 논하고 4장에서 결론을 맺었다.

#### 2. Replica LDO Regulator

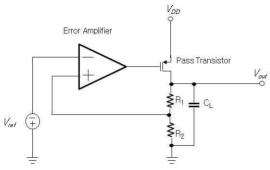

[그림 1] 일반적인 LDO레귤레이터

기본적인 구조의 LDO 레귤레이터의 회로도는 그림 1과 같다. LDO레귤레이터는 에러증폭기(Error Amplifier), 기준 전압회로와 파워트랜지스터, 저항, 커패시터로 구성된다. LDO의 출력전압은 파워 트랜지스터(PT)로 사용된 PMOS에 의해서 전압강하되어 출력된다. 이 경우 가장 큰 문제점은 중간 주파수에서 PSRR이 나쁘다는 것이며 이문제점을 해결하기 위해서는 CL이 커야한다. PSRR이 나빠지지 않는 극점을 구해보면 식(3)과 같다[4]-[6]

$$\frac{V_{ref}}{V_{DD}} = \frac{R_L/(R_L + r_0)^* (1 + s/\omega_a)}{(1 + s/\omega_0)(1 + s/\omega_a) + A_a A_0}$$

(1)

$$p1 = \sqrt{\omega_0 \omega_a (1 + A_a A_o)} \tag{2}$$

$$\omega_0 < \frac{\omega_a}{1 + A_a A_a} \tag{3}$$

극점이 영점보다 작기 위한 조건으로, 위 수식의 조건으로는 C<sub>L</sub>이 커야 한다는 것을 알 수 있다.

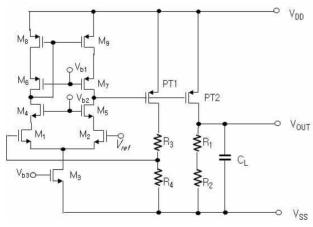

[그림 2] Replica LDO 레귤레이터

그림 2는 Replica LDO 레귤레이터 구조이다. 에러 증폭

기로는 1단 캐스코드 증폭기가 사용되어 졌고 출력단에 PT1 및 R3와 R4로 구성된 Replica회로가 추가로 구성되었다. Replica회로는 출력과 같은 크기 및 구조로 설계되지만부하캐패시터는 연결되지 않는다. 이 경우, 에러 증폭기로인가되는 출력의 궤환 신호는 Replica회로로 부터 얻어지는데, 결과적으로 궤환동작 신호후 레귤레이션 동작 속도가 개선될 수 있으며 PSRR특성이 개선된다. 이때 Replica LDO 레귤레이터의 특성은 식(4)~(5)와 같다.

$$\frac{V_{ref}}{V_{DD}} = \frac{R_L/(R_L + r_0)(1 + s/\omega_r)(1 + s/\omega_a) + A_a(s_oA_r - s_rA_o)}{[(1 + s/\omega_r)(1 + s/\omega_a) + A_rA_a](1 + s/\omega_o)} \tag{4}$$

위식에서  $S_oA_r = S_rA_o$  이라면

$$\frac{V_{ref}}{V_{DD}} = \frac{R_L/(R_L + r_0)(1 + s/\omega_r)(1 + s/\omega_a)}{[(1 + s/\omega_r)(1 + s/\omega_a) + A_rA_a](1 + s/\omega_o)}$$

(5)

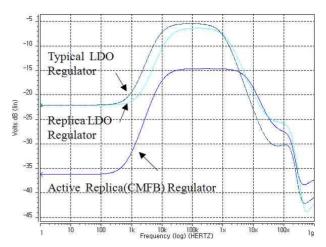

일반적인 레귤레이터보다, Replica 회로를 쓸 경우,  $C_L$ 을  $1/(1+A_aA_o)$ 배 감소시킬 수 있다. 그림 3은 Replica LDO레귤레이터 PSRR특성을 보여 주고 있다.[7]-[8]

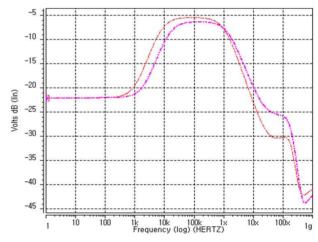

[그림 3] Replica LDO레귤레이터 PSRR특성

특성에서 보이는 것과 같이 Replica LDO레귤레이터가 일반적인 구조에 비하여 중간주파수 대역(200KHz~1MHz)대역에서 좋은 PSRR특성을 얻을 수 있음을 확인할 수 있다. Replica LDO레귤레이터가 안정된 동작을 유지하기 위해서는 출력단과 Replica회로의 DC 매칭이 이루어져야 한다. 본 논문에서는 Replica LDO레귤레이터의 DC매칭을 위한 출력단을 설계하여 3장에 나타내었다.

### 3. 능동 Replica LDO 레귤레이터 설계

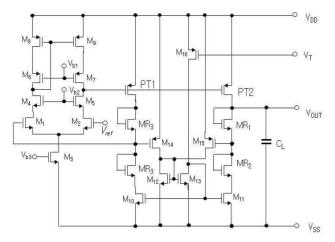

그림 4는 본 논문에서 설계한 능동 Replica LDO레귤레이터이다.

[그림 4] 설계된 Active Replica LDO 레귤레이터

제안된 능동 Replica LDO레귤레이터의 특징을 요약하면 다음과 같다. 첫째, 저항을 트랜지스터 다이오드로 대체하였고 둘째, 트랜지스터 다이오드로 구성된 양쪽 단자의 DC레벨을 맞추기 위해 동상모드 피이드백(CMFB)회로를 구성하였으며, 마지막으로 특징으로 동상모드 전압을 이용하여 레귤레이터 출력 전압을 조정할 수 있도록 하였다. 그림 4에서 트랜지스터 MR1~MR4는 저항을 모의한 것이며, M10~M16은 CMFB회로를 나타낸 것이다. 이때 M16의 게이트 단자 VT에 의하여 레귤레이션 출력 전압을 조정할 수 있다. 그림 5에 능동 Replica LDO레귤레이터의 DC출력 특성 결과를 보여준다.

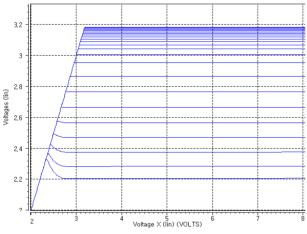

[그림 5] 능동 Replica LDO레귤레이터의 DC출력 특성

그림 5는 VT값을 0.3~2.5까지 변환하였을 때, 입력전압을 1~10V까지 가변입력하였을때 DC출력 특성으로써 각각 2.2V에서부터 3.1V까지 일정한 값을 유지함을 알 수 있다. 또한 제안된 능동 Replica LDO레귤레이터의 PSRR특성이 기존의 일반적인 LDO구조와 Replica 구조에 비하여좋은 결과을 얻을 수 있는데 PSRR특성을 시뮬레이션한결과를 그림 6에 나타내었다.

[그림 6] 능동 Replica LDO레귤레이터의 PSRR

#### 4. 결 론

본 논문에서는 LDO레귤레이터의 PSRR을 향상 및 가 변전압 조정이 가능한 능동 Replica LDO 레귤레이터를 설 계하였다. 일반적인 LDO 레귤레이터의 PSRR과 회로의 안정성을 좋게 하기 위해 사용되는 Replica LDO 레귤레이 터의 경우, 안정된 동작을 유지하기 위해서는 출력단자의 DC레벨이 같은 전위로 유지되어야 한다. 본 논문은 출력 측에 CMFB회로를 추가함으로써, DC전위를 일정한 값으 로 유지하도록 하였다. 또한 출력 측에 DC전압을 일정한 대역내에서 가변될 수 있도록 하였다. 뿐만아니라 본 논문 에서 설계된 CMFB를 가진 능동 LDO레귤레이터의 PSRR 값은 일반적인 LDO 레귤레이터와 Replica LDO 레귤레이 터에 비하여 좋은 특성을 얻을 수 있음을 확인하였다. 으 며 이 가변되는 것을 확인 할 수 있었다. 본 논문에서 설 계한 능동 Replica LDO 레귤레이터의 출력전위 가변특성 과 우수한 PSRR특성은 레귤레이터의 응용성을 확장할 것 으로 기대된다.

#### 참고문헌

- [1] Hoi Lee "A Design of Low-Power Analog Drivers Based on Slew-Rate Enhancement Circuits for CM OS Low-Dropout Regulators", IEEE. J. Solid-state Circuit, 2005.

- [2] Al-Shyoukh, Lee, Perez, "A Transient-Enhanced Low-Quiescent Current Low-Dropout Regulator", IEEE JSSC, 2007.

- [3] Carvajal, J. "The Dlipped Voltage Follower a useful cell for Low-Power Circuit Design" IEEE Trans. Circuits and System. 2005.

- [4] R.J.Milliken, "Fully On-Chip CMOS Low-Dropout Voltage Regulator" IEEE Trans. Circuit Syst-I, 2007

- [5] Vahid Majidzadeh, A Fully On-Chip LDO Voltage Regulator for Remotely Powed Cortical Implants" IEEE j. Solid Circuit, 2009.

- [6] Kim. "Analog IC term project Dinal Report Regulated Replica-Regulator" 2010.

- [7] K.N.Leung, "A Capacitor-Free CMOS Low Dropout Regulator" IEEE Trans. Circuit 2003.

- [8] s.k. Lau, "A Low-Dropout Regulator for SoC With Q-Reduction" IEEE J.Solid-state Circuit, 2007.