# 질화갈륨 소자를 이용한 DPD용 Amplifier Pallet 개발

오성민\*, 박정훈\*, 조삼열\*, 이재훈\*\*, 임종식\*\* \*(주)알에프에이치아이씨 \*\*순천향대학교 e-mail: smoh@rfhic.com

# Design of Amplifier Pallet for DPD Using Gallium Nitride Device

Seongmin Oh\*, Jung-Hoon Park\*, Samuel Cho\*, Lee Jaehoon\*\*, Jong-Sik Lim\*\* \*RFHIC CORPORATION \*\*SOONCHUNHYANG UNIVERSITY

요 약

본 논문에서는 고 효율 및 고 출력 특성을 가지는 질화갈륨(GaN) 소자를 이용하여 WiMAX 및 LTE System에 사용될 수 있는 DPD용 Pallet Amplifier를 제작하였다. 제작된 Pallet Amplifier는 Pre-drive로써 저 전류의 MMIC를 채택하고, Drive 단과 Main 단에 15W 급과 30W 급의 질화갈륨 소자를 사용 하였으며, 추가적인 효율 개선을 위해 PCB상에 Doherty Structure를 적용함으로써 보다 높은 효율을 구현하였다. 제작된 Pallet Amplifier는 음 전원 Bias 제어 회로, 온도에 따른 Gain 보상회로, Sequence 회로 및 Main 전원 Drop에 따른 보호 회로를 구현하였다.

WiMAX Signal을 이용한 Modulation Power 10Watt Test에서 약 36.8~38.3%의 Pallet 효율과 DPD Solution인 TI GC5325SEK DPD Board 사용 시 ACLR은 약 46dBc 이상을 가지는 것으로 측정되었다. 본 논문에서 제작된 Pallet Amplifier는 Upper Band와 Lower Band로 나누어 제작되었던 기존 Pallet Amplifier와 달리 하나의 Pallet Amplifier로 2496~2690MHz에서 모두 사용하면서 종전에 사용되고 있는 Pallet Amplifier에 비해 Size가 최소 10% 이상 축소되어 효율 및 크기 면에서 종전 Pallet Amplifier보다 큰 이점을 갖는다.

### 1. 서론

최근 정보통신과 이동통신 분야의 급속한 발전에 따른 통신기기의 수요 증가와 전 세계적으로 환경문제가 Issue가 되는 가운데 통신 시스템을 구성하는 RF 부품들은 고 집적화 및 고 성능화, 고 효율화의 중요성이 점점 크게 대두되고 있다.

이러한 RF 부품들의 변화에 따라 Amplifier 분야에서 역시 제품 개발에 있어 고 집적화와 고 효율화에 초점을 맞추어 개발되고 있다.

Amplifier를 구성하는 부품 중에서 효율 특성에 가장 큰 영향을 끼치는 부품은 단연 반도체 소자이다.

Amplifier에 사용되는 반도체 소자의 경우 제 1세대인 규소(Si) 반도체 소자에서부터, 제 2세대인 갈륨비소(GaAs) 반도체 소자와 제 3세대인 질화갈륨(GaN; Gallium Nitride) 반도체 소자가 있으며, 새로운 반도체 소자가 개발되면서 보다 향상된 출력과

전력 특성을 개선해 왔다.

이중 제 3세대인 질화갈륨 반도체 소자는 높은 온도에서도 고속 및 고 출력 특성을 내는 것이 가능하며, 높은 항복 전압과 높은 포화 전자 속도 특성 및절연파괴 내성으로 좁은 면적에서 저 전력으로 고출력을 얻을 수 있기 때문에, 현재 널리 사용되고있는 Silicon 기반의 LDMOS (Laterally Diffused Metal Oxide Semiconductor) 소자에 비해 Amplifier구성에 공간적인 측면과 효율적인 측면에서 이점을가지고 있다. 따라서 질화갈륨 반도체 소자는 기존반도체 소자에 비해 고 집적화와 고 효율화에 적합한 소자라 할 수 있다.

본 논문에서는 고효율 소자인 질화갈륨 반도체 소자와 가장 기본적인 2-Way Doherty Structure를 이용하여 고 집적화, 고 효율화된 Pallet Amplifier를 제작하고 Test 하였다.

#### 2. 본론

# 2.1 질화갈륨 반도체 소자의 Packaging

질화갈륨 반도체 소자의 기본 Cell인 Die 형태 자체로는 Amplifier에 바로 적용하는 것이 실제적으로 상당한 어려움이 있기 때문에 Packaging 공정으로 통하여 일반적으로 사용하는 Package 된 Transistor의 모습을 갖추어야 한다. 또한 Package 된 Transistor는 Amplifier 구성의 용의성과 소자 보호라는 장점을 가질 수 있다.

질화갈륨 반도체 소자는 앞서 서론에 설명한 바와 같이 단위 면적 당 높은 출력과 높은 동작 온도 실 현이 가능하기 때문에 사용 중인 다른 반도체 소자 들에 비해 소형화된 Package의 사용이 용이하다.

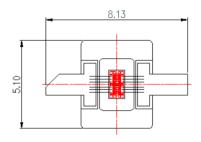

본 논문에서 제작된 Pallet Amplifier에 사용된 질화갈륨 반도체 소자는 미국 Cree 사의 8Watt 급 출력과 30Watt 급 출력을 갖는 질화 갈륨 반도체 소자로써, (주)RFHIC에서 Packaging 공정을 통해 다음과 같은 크기에 Package를 진행 하였다.

[그림 1] 질화갈륨 반도체 소자의 Package Layout

Package된 8Watt 급 및 30Watt 급의 질화갈륨 반도체 소자는 LDMOS나 다른 동급 출력의 다른 Package에 비해 60% 이하의 크기를 가지며 상당히 좁은 면적에서도 동작에 어려움이 없다. 이는 질화갈륨 반도체 소자가 기존의 다른 반도체 소자에 비해 소형화에 유리함을 단적으로 보여준다.

질화갈륨 반도체 소자의 Active Model을 사용하여 Circuit Simulation Tool 인 Agilent사의 ADS를 통해 Packaging 된 Transistor의 Simulation과 그에 따른 PCB External Matching Simulation을 진행하고, 그 결과를 바탕으로 PCB를 제작 검증 하였다.

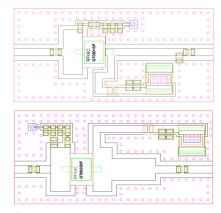

특성 검증용으로 사용된 PCB는  $\&prec{6}$ r = 3.5, H = 0.765mm, T = 0.035mm, tanD = 0.002 인 Taconic 사의 RF35 기판을 사용 하였으며, 검증용으로 제작된 PCB의 Layout은 아래 [그림 2]에 나타내었고, 그에 따른 Test 결과는 아래 [표 1]에 나타내었다.

[그림 2] Package External Matching PCB Layout

[표 1] 질화갈륨 반도체 소자 Package의 RF 특성

| Test Frequency  | 8 Watt 급 | 30 Watt ∃ |

|-----------------|----------|-----------|

| [2.6GHz]        | Package  | Package   |

| Voltage         | 30 V     | 30 V      |

| IDQ Setting     | 230 mA   | 300 mA    |

| Gain            | 16.4 dB  | 14.8 dB   |

| Peak Power      | 40.5 dBm | 45.65 dBm |

| Current         | 505 mA   | 1.496 A   |

| Peak Efficiency | 74.1 %   | 79.9 %    |

[표 1]의 Test 결과를 통하여 Packaging 되어 PCB에 결합된 질화갈륨 반도체 소자가 가지는 효율은 약 70%를 상회하는 것으로 측정되었으며, 이는 LDMOS 및 현재 사용되고 있는 다른 반도체 소자들이 대다수 50%대의 효율을 가지는 것을 감안할때 월등히 높은 수치임을 알 수 있다.

#### 2.2 Doherty Structure

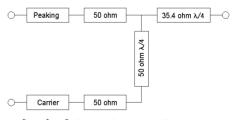

Amplifier 개발에서 효율을 향상시키는 방법 중에서 Doherty Structure는 가장 간단한 구조이면서 구성이 용이하고 효율 개선 효과가 좋아 개발자에 의한 선호도가 높다. 본 논문에서 제작된 Amplifier는소형화에 중점을 두어 기본이 되는 2-Way Doherty 방식을 채택하였으며, 그 구조는 다음 [그림 3]과 같다.

[그림 3] Basic Doherty Structure

[그림 3]에서 나타낸 2-Way Doherty 구조는 Carrier Amplifier가 Saturation 되는 시점에서 Peaking Amplifier가 Turn On 되면서 출력 전력이 Combine 되는 구조로써 Carrier Amplifier의 Saturation 되는 출력 전력이 증대되어, 최대 효율을 유지하게 함으로써 효율을 개선하는 구조이다.

[그림 3]은 2-Way Doherty Structure와 30Watt 급의 Packaging된 질화갈륨 소자를 이용한 검증용 PCB의 Layout 이다.

제작된 PCB는 앞서 사용한 PCB와 동일한 PCB를 사용하였으며, 측정된 RF CW 특성 결과를 다음 [표 2]에 나타내었다.

[그림 3] 구현된 Doherty 구조의 PCB Layout

[표 2] 구현된 Doherty 구조의 RF 특성

| Test Frequency  |         | 30Watt 급 질화갈륨 소자를 이용한 |  |

|-----------------|---------|-----------------------|--|

| [2.6GHz]        |         | Doherty Structure     |  |

| Volt            | age     | 30 V                  |  |

| IDQ Setting     | Carrier | 300 mA                |  |

|                 | Peaking | -4.5V                 |  |

| Peak Power      |         | 48.52 dBm             |  |

| Current         |         | 3.652 A               |  |

| Peak Efficiency |         | 81.34 %               |  |

Packaging 된 30Watt 급 질화갈륨 반도체 소자보다 Packaging 된 30Watt 급 질화갈륨 소자와 Doherty Structure를 적용하여 Total 60Watt 급으로 구현한 것이 낮은 출력 측에서 좋은 효율을 가졌으며, 약 35dBm 출력에서는 최대 10% 정도의 효율이 개선되었고 정격 출력 10Watt에서는 약 6.5% 정도의 효율이 개선되었다.

# 2.3 Pre-Drive 구성

Pallet Amplifier을 제작함에 있어 Drive Amplifier 와 Main Amplifier만으로 구동하기에는 높은 Input Power를 필요로 하기 때문에 추가적으로 Pre-Drive 단을 구성하여 적은 Input Power로 동작할 수 있는 환경을 구축해 주어야 한다.

본 논문에서 제작된 Pallet Amplifier는 RFHIC 사의 P1dB 20dBm 급의 AP410(SOT-89 Type)과 Sirenza 사의 1W 급 SZA-2044(4\*4 QFN Type)를 사용하여 Pre-Drive를 구성하였다.

제작된 Pre-Drive 단의 RF Modulation 출력 특성 은 아래 [표 3]에 나열하였다.

앞서 설명한 8Watt 급 질화갈륨 반도체 소자와 30Watt 급 질화갈륨 반도체 소자의 Gain을 통하여 Power Budget을 유추하면 [표 3]에 측정된 17dBm 은 Pre-Drive로써 충분한 출력을 갖는다.

[표 3] 구현된 Pre-Drive 단의 RF 특성

| Test Frequency [2.6GHz] |          | Pre-Drive 단 |          |  |

|-------------------------|----------|-------------|----------|--|

| Volta                   | age      | 5 V         | V        |  |

| IDQ Setting             | AP410    | 40 mA       |          |  |

|                         | SZA-2044 | 260 mA      |          |  |

| Total                   | Gain     | 38.4        | dB       |  |

| ACLR @ 17dBm            |          | -5.27MHz    | +5.27MHz |  |

| [WiMAX 20MHz Signal]    |          | 46.6dBc     | 46.3dBc  |  |

| Current @ 17dBm         |          | 300 mA      |          |  |

# 2.4 Bias Sequence

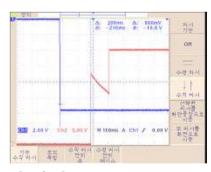

질화갈륨 반도체 소자는 Gate에 음(-)전원을 사용하는 소자이다. 만약 Gate에 음전원이 인가되지 않은 상태에서 Drain 전압이 인가될 경우 질화갈륨 반도체 소자가 Damage를 입거나 상황에 따라 소손될 가능성이 있기 때문에 음전원에 적합한 Bias 회로와 Bias를 순차적으로 인가하기 위한 Sequence 회로를 사용해야 한다. 제작된 Pallet Amplifier는 FET 및 OP-AMP등을 이용하여 Sequence 회로를 구현 하였으며, 그에 따른 Bias Sequence Timing은 다음 [그림 4]로 측정 되었다.

[그림 4] Bias Sequence Timing

Main 전원 인가 시 Gate에 인가되는 전압은 -12V 가량으로 선 입력되며, 약 200ms Delay 이후 Drain 전압이 인가되어 전원 인가 오류에 의한 소자 Damage 및 파손을 피할 수 있다.

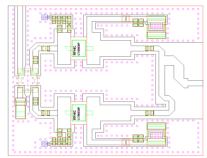

### 2.5 Amplifier Pallet 제작

앞서 나타낸 결과들을 바탕으로 실제 Amplifier

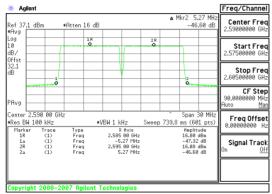

Pallet을 제작하고 제작된 Pallet의 RF 특성 및 DPD Test 결과를 [표 4] 및 [그림 5]에 나타내었다.

| 田 | 4] | 구현된 | Pallet | Amplifier의 | RF | 특성 |

|---|----|-----|--------|------------|----|----|

|---|----|-----|--------|------------|----|----|

| Test Frequency [2496~2680 MHz] |             | Pallet Amplifier   |           |

|--------------------------------|-------------|--------------------|-----------|

| Voltage, IDQ                   | Pre-Drive   | 5 V 300mA          |           |

|                                | Drive, Main | 30 V 620mA         |           |

| Total Small Signal Gain        |             | 61.4 dB            |           |

| ACLR @ 40dBm                   |             | -5.27MHz           | +5.27MHz  |

| WiMAX 2FAPAR 8.0               |             | ≥ 26.3dBc          | ≥ 25.5dBc |

| DPD ACLR @ 40dBm               |             | -5.27MHz           | +5.27MHz  |

| WiMAX 2FA PAR 8.0              |             | $\geq$ 46.8dBc     | ≥ 46.3dBc |

| Current Consumption@ 40dBm     |             | $0.74A \sim 0.76A$ |           |

| Efficiency @ 40dBm             |             | 36.9% ~ 38.3%      |           |

\*\* DPD Solution: TI GC5325SEK DPD Board

[그림 5] 2590MHz DPD Test 결과

[그림 6] 제작된 Pallet Amplifier

#### 3. 결론

본 논문에서는 차세대 소자로 주목받고 있는 고효율의 질화갈륨(Gallium Nitride) 반도체 소자를 Packaging 공정을 통하여 Transistor로 구현하였으며, 구현된 Transistor와 추가적인 효율 개선을 위해 Doherty Structure를 적용하여 WiMAX 및 LTE System에서 적용될 수 있는 고 효율 및 Size Reduce 된 Pallet Amplifier를 제작하였다.

제작된 Pallet Amplifier은 Small Signal Gain

61.4dB와 -17dB 이하의 Input Return Loss를 가지며, WiMAX 10Watt 출력에서 36.9~38.3%의 고 효율과 25dBc 이상의 ACLR 특성을 나타내었다.

또한 TI GC5325SEK DPD Board 적용 시에는 46.3dBc 이상의 ACLR 특성을 나타내었다.

실제 제작된 Pallet Amplifier의 크기는 130\*80\* 18.8mm(Cover 포함)으로 WiMAX 2496~2680MHz 대역을 모두 사용할 수 있으며, 기존에 Upper Band, Lower Band로 나뉘어 사용 중인 타사의 동급 출력의 Pallet Amplifier와 비교하여 볼 때 최소 10% 이상의 크기가 절감 되었다.

제작된 Pallet Amplifier는 WiMAX 및 LTE등의 System 구성 시에 효율 및 공간 활용 면에서 큰 이점을 가질 수 있을 것으로 기대된다.

#### 참고문헌

- [1] 오성민, 임종식, 이용호, 박천선, 박웅희, 안달 "질화갈륨 고출력 트랜지스터 패키지의 성능 최적화", 한국 산학 기술학회 논문지, 제9권, 제3호, pp. 649-657, 2008.

- [2] 오성민, "질화갈륨 고출력 소자의 성능 최적화에 관한 연구", 순천향대학교 공학석사학위논문, 2008.

- [3] 이종욱, "AlGaN/InGaN HEMTs의 고성능 초고주 파 전류 특성", 한국 전자파학회 논문지, 제15권, 제8호, pp. 752-758, 8월, 2004.

- [4] 이상학, "질화갈륨 소재 및 소자관련 기술동향", 한국과학기술정보연구소 연구보고서, 12월, 2003.

- [5] 김재곤 김지연 이동헌 김종헌, "고 출력 고 이득 2 단 도허티 전력증폭기의 설계", 한국 전자파학회 논 문지, 제17권, 제11호, pp. 1030-1039, 11월, 2006.

- [6] 홍용의 양승인, "3-Way Doherty 증폭기의 선형 성 및 효율 개선에 관한 연구", 한국 전자파학회 논문지, 제17권, 제2호, pp. 124-128, 2월, 2006.

- [7] 김재형, "Doherty Amplifier의 선형성 향상", 한 국항공대학교 공학석사학위논문, 2008.

- [8] STEVE C. CRIPPS, "RF Power Amplifiers for Wireless Communications", Artech House, 1999.

- [9] GUILLERMO GONZALEZ, "Microwave Transistor Amplifiers Analysis and Design" Prentice Hall, 1997.