# PI 기판에 전사된 단결정 실리콘 박막의 유연 신뢰성

# Reliability of single crystal silicon film transferred on PI substrate

\*은경태 <sup>1</sup>, <sup>#</sup>좌성훈 <sup>1</sup>, 황우진 <sup>1</sup>, 최현주 <sup>2</sup>, 김재현 <sup>2</sup>

\*K. T. Eun<sup>1</sup>, <sup>#</sup>S. H. Choa(shchoa@snut.ac.kr)<sup>1</sup>, W. J. Hwang<sup>1</sup>, H. J. Choi<sup>2</sup>, J. H. Kim<sup>2</sup>

<sup>1</sup> 서울산업대학교 NID 융합대학원, <sup>2</sup>한국기계연구원 나노융합기계연구본부

Key words: Silicon film, Bendability, Stretchability, Transfer Printing

# 1. 서론

최근 유연 전기전자 소자에 대한 연구가 활발히 진행 되고 있다. 가령 OLED, e-paper, skin 센서 등이 있다. 이러한 소자를 제작하는 기술도 다양하게 제시되고 있으 며 잉크젯 프린팅, 그라비어(gravure) 프린팅 기술, 롤투 롤 프린팅 기술 등 매우 다양한 방법이 제시되고 있다. 이러한 기술은 유기재료를 기반으로 하는 기술로서 유연 성과 저가격 등의 이점이 있다. 그러나 이러한 유기재료 를 기반으로 하는 기술은 실리콘을 기반으로 하는 기존 의 반도체 기술에 비하여 아직까지 전기적 특성 및 신뢰 성 측면에서 매우 열악한 실정이며, 상용화에 이르기 까 지는 여러 난제를 극복해야 되는 문제가 있다. 이러한 문제에 대한 하나의 대안으로서 기존의 나노 및 마이크 로 스케일의 실리콘 소자를 유연 폴리머 기판에 부착하 여 유연성을 갖게 함과 동시에 실리콘 소자가 갖는 기존 의 여러 장점은 그대로 유지하고자 하는 기술이 활발히 연구되고 있으며, 이러한 기술을 transfer printing 기술이 라고 한다. Transfer printing 기술은 Rogers 그룹[1]에서 처음 개발이 되었고, TFT 소자[2], RF 소자, LED 소자 및 Image 센서[3] 등 다양한 소자들이 이 기술을 이용하 여 제작된 바 있다. Transfer printing 기술을 적용함에 있 어서 해결해야 될 문제는 실리콘이나 SiO<sub>2</sub> 와 같은 무기 재료들은 매우 brittle 하여 약 1%의 변형률 (strain)에도 쉽게 파괴된다는 것이다. 이런 문제점을 해결하기 위하 여 wavy 패턴을 적용하여 stretchability 를 개선하고, 약 5%의 인장 변형에도 신뢰성이 확보됨을 보였다. 그러나 유연소자는 인장 변형 보다는 굽힘 변형에 대한 신뢰성 이 더 중요하다. 단결정 실리콘 박막은 brittle 한 재료로 서 연신율은 약 0.82% 이다[4]. 그러나 단결정 실리콘을 마이크로/나노 두께의 박막으로 thinning 할 경우 유연성 이 증가하게 된다. 본 논문에서는 나노 두께의 단결정 실리콘 박막을 transfer printing 기술을 이용하여 폴리머 기판에 부착시킨 후 굽힘 및 인장 시험을 통하여 단결정 실리콘 박막의 flexibility 와 stretchability 의 개선 효과를 연구하였다.

# 2. 단결정 실리콘 박막의 제작 및 전사

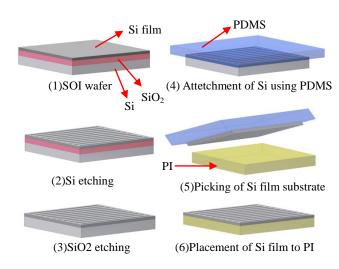

본 논문에서는 유연 기판으로 전사된 단결정 실리콘 박막의 유연 신뢰성을 측정하기 위해 Fig. 1 과 같이 단결 정 실리콘 박막의 제작, 전사공정을 진행하였다. 전사공정을 용이하게 하기 위하여 SOI (silicon on insulator) 웨이퍼의 400nm 두께를 가지는 SiO<sub>2</sub> 층을 buffer layer로 이용하였다. 200nm 두께의 Si 박막층에 홀 지름 10um, 홀 피치 50um 의 홀 타입 패턴과 너비 5um, 길이 95um 의 stripe 타입 패턴을 각각 설계하여 RIE 공정을 이용하여에칭 하였다. 실리콘 박막의 크기를 각 10×10mm 로 하여 다이싱 한 후 전사 공정을 위하여 SOI wafer 를 49% HF에 담구어 buffer layer인 SiO<sub>2</sub>를 wet 에칭 하였다. 제작된 실리콘 박막의 전사는 PDMS (poly-dimethylsiloxane) stamp 를 이용하여 진행하였다. 유연기판의 재료는 두께 50um, 크기 20×20mm 의 PI(polyimide)를 사용하였다. PI

와 실리콘 박막 사이의 접착제는 NOVA 61 UV adhesive 를 사용하였다. Fig. 2 는 PI 기판에 전사된 홀 타입 단결정 실리콘 박막의 SEM 사진 이미지를 보여주고 있다.

Fig. 1 Fabricating and printing method of crystal Si film

Fig. 2 SEM image of single crystal silicon film on PI substrate

#### 3. 단결정 실리콘 박막의 유연 신뢰성

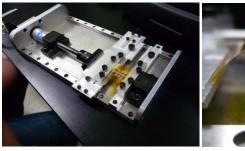

본 연구에서는 PI 기판 위에 전사된 단결정 실리콘 박막의 유연 신뢰성을 확인하기 위하여 굽힘 시험과 인장시험을 각각 진행하였다. PI 기판에 전사된 실리콘 박막을 Fig. 3 에 나타내어진 것과 같이 자체 제작한 신뢰성장비에 장착한 후 시험을 실시하였다. 실리콘 박막의 측정은 광학 현미경을 이용하여 실리콘 박막의 형상을 관

찰하는 방식으로 진행하였다. 본 연구에서는 굽힘 반경 및 굽힘 시 발생하는 인장률을 Rogers 그룹[5]에서 제안 한 다음 식을 적용하여 계산하였다. 시험 시 인장 및 굽 힘 속도는 0.02mm/s 로 진행하였다.

$$R_{\text{nom}} = \frac{L}{2\pi\sqrt{\frac{dL}{L} - \frac{\pi^2 h_s^2}{12L^2}}}$$

(1)

$$\varepsilon_{\text{nom}} = \frac{h_{\text{s}}}{2R_{\text{nom}}} \tag{2}$$

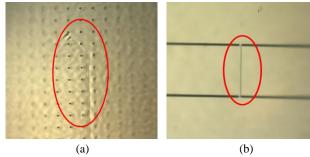

Table 1 은 굽힘 시험 및 인장 시험 결과 수치를 나타내고 있다. 굽힘 시험 결과 홀 타입의 경우 곡률 반경이 7.5mm 에서 크랙이 발생하였으며, 이 때 실험을 중단하였다. Fig. 4 는 단결정 실리콘 박막의 크랙 발생 형상을 광학 현미경으로 촬영한 이미지이다. 크랙은 홀 부위에서 발생하기 시작하였다. 이 때의 인장률은 0.33%로 계산되었다. Stripe 타입 실리콘 박막의 크랙은 7.4mm 부근으로 홀 타입과 비슷한 곡률 반경 지점에서 나타났다.홀 타입과 stripe 타입의 미세 패턴에서 과도한 응력이 발생하여 크랙이 발생한 것으로 판단된다. 또한 인장테스트를 진행한 결과 홀 타입은 기판의 인장률 1.8%에서 크랙이 발생하였고, stripe 타입은 인장률 0.5%에서 크랙이 발생하였다.

Fig. 3 Bending, stretching test machine

Fig. 4 Fracture image using optical microscope (a) hole type, (b) stripe type

Table 1 Bending and stretching test result

| Fracture point |                |                   |

|----------------|----------------|-------------------|

|                | Bending Radius | Stretching Strain |

| hole type      | 7.5mm          | 1.8%              |

| stripe type    | 7.4mm          | 0.5%              |

## 4. 토론

한국 기계연구원의 실험 결과[4]에 의하면 단일 silicon 박막의 인장 변형률이 약 0.8%에서 파괴가 발생하였다. 한편, 본 연구에서 사용한 유연기판에 전사된 홀 타입의실리콘 박막은 1.8%에서 파괴가 되었다. 이 결과를 적용하여 보면 유연 기판으로 전사된 Si 박막은 유연기판 및접착제의 영향을 받을 수 있기 때문에 기판의 인장률이 0.8% 이상으로 증가되었다고 판단된다. 가령 폴리머 기판과 실리콘 박막의 사이의 접착제의 완충작용으로 인하여, 기판의 변형률이 실리콘 박막으로 완전히 전달되지못하였기 때문이라고 판단된다. 반면 stripe 타입은 기판의 인장 변형률이 0.5%일 때 크랙이 발생하였다. Stripe 타입의 브릿지의 크기는 3×5um 로 매우 작기 때문에 작은 인장 변형률에도 불구하고 크랙이 발생하여 실리콘 박막의 stripe 형상에 크랙을 유발하였다고 판단된다.

굽힘 시험의 경우 Rogers 그룹[5]의 data 에 의하면 PET 박막에 전사된 Si 100nm 두께 샘플의 굽힘 시험을 보면 인장률이 약 0.8%에서 파괴가 되었다. 반면 본 연구에서 진행한 실리콘 박막은 굽힘 반경 7.5mm, 인장률 0.33%에서 파괴가 일어났다. 이러한 원인은 본 연구에서 사용한 실리콘 박막의 경우 홀 및 브릿지에서 스트레스가 집중되어 0.33%의 작은 인장률에서 파괴가 되었다고 판단된다.

# 5. 결론

본 연구에서는 PI 기판에 전사된 단결정 실리콘 박막의 유연 신뢰성에 굽힘 및 인장 실험을 진행하였다. 홀타입과 stripe 타입의 크랙은 굽힘 곡률 반경 7.5mm 정도에서 크랙이 발생하였다. 인장시험의 경우 홀 타입은 1.8%에서, stripe 타입은 0.5%에서 크랙이 발생하였다. 크랙의 발생은 홀 타입 박막의 홀 부분, stripe 타입 박막의 브릿지 부분에서 발생 하였다. 실리콘 박막의 홀 및 브릿지 부분에서 집중적인 응력이 발생하여 크랙이 발생한 것으로 판단된다. 유연 박막의 신뢰성을 높이기 위해서는 미세 홀 타입이나 브릿지 구조는 가급적 피하는 것이 바람직하다고 판단된다.

#### 후기

본 연구는 지식경제부, 산업원천기술개발산업의 일환인 "3 차원 멀티스케일 구조물 제작기술 개발"의 지원에 의한 것입니다.

# 참고문헌

- 1. D, Kim, et al., "Stretchable and Foldable Silicon Integrated Circuits," Science, 200, 507-511, 2008.

- J.-H. Ahn, H.-S. Kim, K.J. Lee, Z. Zhu, E. Menard, R.G. Nuzzo and J.A. Rogers, ""High Speed, Mechanically Flexible Single-Crystal Silicon Thin-Film Transistors on Plastic Substrates,"" IEEE Electron Device Letters, 27(6) 460-462, 2006.

- 3. S, Park, et al., "Printed Assemblies of Inorganic Light-Emitting Diodes for Deformable and Semitransparent Displays", Science, 325, 977-981, 2009.

- 4. 이상주, 한승우, 김재현, 이학주, "단결정 실리콘 박막의 미소인장 물성 평가," 한국정밀공학회 추계학술대회, 45-49, 2009.

- S-I, Park, et al., "Theoretical and Experimental Studies of Bending of Inorganic Electronic Materials on Plastic Substrates, Adv. Funct. Mater, 18, 2673–2684, 2008