# 240\*320 TFT-LCD의 컨트롤러 하드웨어 설계

성광주\*·하창수\*\*·최병윤\*\*\*

\*동의대학교 컴퓨터공학과 석사과정

\*\*\*동의대학교 컴퓨터공학과 박사과정

\*\*\*동의대학교 컴퓨터공학과 교수

## Hardware Design of 240\*320 TFT-LCD Controller

Kwang-Ju Sung\* · Chang-Soo Ha\*\* · Byeong-Yoon Choi\*\*\*\*

\*\*\*\*\*\*\*Dongeui University

E-mail: \*reuben2932@hanmail.net, \*\*systemonchip@daum.net, \*\*bychoi@deu.ac.kr

### 요 약

본 논문에서는 최근 모바일장치에서 널리 사용되는 TFT-LCD를 제어 할 수 있는 컨트롤러를 하드웨어로 구현하고 FPGA로 검증한 내용을 기술한다. TFT-LCD 컨트롤러는 red, green, blue의 픽셀 정보와 동기화 할 수 있는 Hsync, Vsync 신호를 출력하고 TFT-LCD에 각 픽셀의 RGB 값이 나타나게 된다. 하드웨어 기술 언어로는 verilog-hdl을 사용하였고, 모델심 소프트웨어를 통하여 시뮬레이션을 확인하고 Xilinx FPGA를 통해 올바른 동작을 검증하였다. 프레임 버퍼는 FPGA안에 블록램의 형태로 구성하여 TFT-LCD에 이미지 파일이 출력되도록 설계 하였다.

## **ABSTRACT**

This paper describes hardware design and FPGA verification of TFT-LCD controller used in mobile devices widely. TFT-LCD controller outputs pixel's color information red, green, blue and Hsync, Vsync synchronization signals. We used verilog-hdl to describe TFT-LCD controller and simulated it using modelsim software and verified it's exact operation on Xilinx FPGA. Framebuffer made up Block RAM form in FPGA and TFT-LCD displayed image file.

#### 키워드

TFT-LCD, 컨트롤러, FPGA, 블록램

## 1. 서 론

TFT-LCD(Thin Flim Transistor-Liquid Crystal Display)는 디스플레이 기술의 발달로 모바일장치에서 컴퓨터의 모니터, 대형 TV에 이르기까지 널리 사용되고 있는 디스플레이 장치이다.

본 논문은 TFT-LCD 컨트롤러 하드웨어를 구현하는 방안에 대해 기술한다. 컴퓨터그래픽 파이프라인에서 래스터 변환 후 얻어지는 프래그먼트가

프래그먼트 테스트 이후 프레임버퍼에 기록되게 된다. 프레그먼트 연산이 끝난 상황이라 가정하고 디스플레이를 위해 Raw 형태의 이미지파일을 사 용하여 TFT-LCD에 디스플레이 할 수 있도록 하 였다. 사용한 장비는 휴인스사의 VIP-2000 개발 보드이며 VIP-2000은 240\*320 해상도를 가지는 TFT-LCD를 제공한다. 프레임버퍼 역할을 위해 VIP-2000에서 제공하는 Xilinx VERTEX 4 FPGA 안에 블록램을 구현하여 프레임버퍼의 역할을 할 수 있게 하였고 TFT-LCD의 수평 및 수직 동기화 신호에 따라 블록램의 내용이 TFT-LCD에 나타나 게 된다.

#### Ⅱ. 본 론

#### 1. TFT-LCD 동작

VIP-2000 개발 보드에서는 LPC3600A 타이밍 제어 모듈과 LTS350Q1-PE1 고급 LCD 패널을 사 용하는 3.5" TFT-LCD 모듈이 장착되어 있다.

LPC3600A는 RGB신호와 수평, 수직 동기화를 위한 Hsync, Vsync 등의 타이밍 제어를 통해 디 스플레이 가능하게 한다.

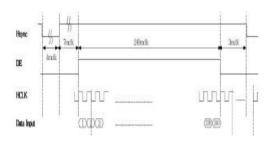

그림 1,2는 LTS350Q1-PE1 모델 수직 타이밍 다이어그램과 수평 타이밍 다이어그램이다.

사용하는 TFT-LCD는 프레임 단위로 이미지를 출력한다. 프레임은 여러 개의 라인으로 이루어졌 으며 가로 240픽셀, 세로 320라인으로 구성되어 있다. 기본적으로 RGB 데이터의 전송은 행 단위 로 시작되고 Hsync 신호에 의해 동기화된다. 그 리고 수평 동기화 단계인 Porch(Vsync가 일정 시 간 2H)기간에서 low를 유지한 후 Back Porch(porch 직후)단계로 진입하고 이 기간 동안 Vsync가 high값을 유지하게 된다. Back Porch이 후에 DE(Vsync, Hsync가 high일 때)가 high가 되면 RGB 데이터가 행 단위로 전송이 되고 이 때 TFT-LCD에 RGB 데이터의 내용이 디스플레이 된다. 이 기간 동안은 Vsync가 high로 유지되어 있어야한다. 이미지 전송이 끝난 후 Front Porch(Porch 앞 3H 기간)는 일정시간 동안 Vsync를 유지해야한다.

그림 1. 수직 타이밍 다이어그램

그림 2. 수평 타이밍 다이어그램

제공되는 TFT-LCD의 클록의 입력 주파수는 표 1와 같이 5MHz~20HMz 사이에 동작이 가능하도 록 설계가 되어 있다. 본 논문에서는 VIP-2000 개 발 보드의 메인 클록 주파수가 24MHz이다.

TFT-LCD 동작을 위해 내부적 분주기로 분주시켜 사용하였다.

표1. LPC3600A의 주요 신호에 대한 동작 주파수

| Signal        | Description      | Symbol           | Min | Тур | Max | Unit |

|---------------|------------------|------------------|-----|-----|-----|------|

| MCLK          | Frequency        | 1/T <sub>c</sub> |     | 5   | 20  | MHz  |

|               | High level width | Тон              | 3   | 6   | -   | ns   |

|               | Low level width  | Tcı              | 3   |     |     | ns   |

| INPUT<br>DATA | setup time       | Tos              | 3   | -   |     | ns   |

|               | hold time        | T <sub>DH</sub>  | 3   | *   |     | ns   |

| DE            | setup time       | Tes              | 3   |     |     | ns   |

|               | hold time        | Тен              | 3   |     |     | ns   |

#### 2. TFT-LCD 컨트롤러 모듈 설계

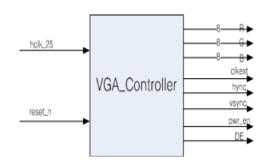

그림 3은 TFT-LCD를 제어 할 수 있는 컨트롤 러의 블록도이다. VIP-2000 개발 보드의 메인 클 록 주파수를 분주시켜 clkext 신호를 통해 TFT-LCD에 들어가도록 구현하였다.

그림 3. VGA 컨트롤러 블록도

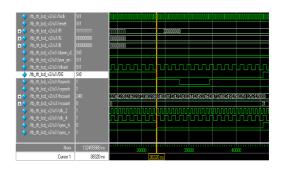

그림 4. 모델심 시뮬레이션

그림 4는 verilog hdl로 설계된 컨트롤러의 정확한 동작을 확인하기 위하여 모델심을 통해 시뮬레이션을 수행한 검증 화면이다. 시뮬레이션을 통해 올바른 동작을 하고 있음을 확인할 수 있었

다. 그림 2의 수평 타이밍 다이어그램을 참고하여 파형을 분석하면 hcount가 240이 된 후 hcount가 243이 될 때까지 Hsync가 high를 유지하는 Front Porch단계, hcount가 243~246동안 Hsync를 low로 유지하는 Porch단계, 그리고 hcount가 247이되면서 Hsync가 high가 되며 Back Porch로 진입하는 것을 확인할 수 있다. Hsync, Vsync가 동기화 될 때, DE 신호가 high가 되며 TFT-LCD에 프레임버퍼에 있는 RGB 데이터들이 출력되는 것을확인할 수 있다.

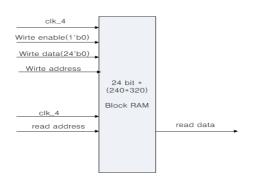

#### 3. Frame buffer 구현

TFT-LCD 화면에 디스플레이 하기 위해서는 프레임버퍼 상에 RGB 화소의 값이 기록 되어 있어야한다. 본 연구에서는 JPEG, BIT 이미지파일보다 쉽게 RGB 값을 얻기 위하여 Raw 형태의 이미지파일을 사용하였다. 그리고 Raw 이미지 파일을 FPGA 구현 소프트웨어가 해석할 수 있는 스트링으로 변환하기 위하여 c언어를 사용한 변환프로그램을 구현하였다. 변환된 데이터의 내용을 Xilinx ISE에서 제공하는 Coregen을 통하여 그림 5와 같은 듀얼 포트를 갖는 블록램을 구현 하였고 블록램의 데이터가 TFT-LCD 컨트롤러를 통해 TFT-LCD에 출력된다.

그림 5. Dual Port Block RAM 블록도

Xilinx ISE 합성 툴을 통하여 구현된 컨트롤러와 블록램을 합성하였고 합성 결과 동작주파수는 119.87MHz이며 사용 면적은 표 1과 같다.

표 2. 구현된 회로의 합성 결과

| Slices     | 622/49152 (1%) |

|------------|----------------|

| Flip Flops | 55/98304 (0%)  |

| LUTs       | 286/98304 (0%) |

| RAMBs      | 104/240 (43%)  |

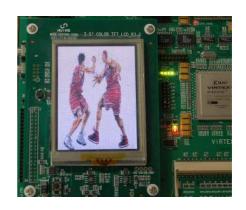

VIP-2000 개발 보드에서 TFT-LCD를 구동하기 위하여 핀 번호를 지정 후 Xilinx ISE에서 제공하 는 iMPACT 프로그램을 이용하였다. 만들어진 mcs파일과 비트파일을 JTAG을 통하여 FPGA에 다운로드하여 FPGA에서 동작화면을 확인 할 수 있었다. 그림 6은 프레임버퍼상의 이미지가 TFT-LCD에 디스플레이 되는 화면이다. TFT-LCD 컨트롤러에 의해 RGB의 픽셀 정보와 동기화 할수 있는 Hsync, Vsync를 출력하고 TTF-LCD에 정확히 디스플레이 되는 것을 확인할 수 있었다.

그림 6. TFT-LCD 동작 화면

## Ⅲ. 결 론

본 논문은 240\*320 해상도의 TFT-LCD를 제어할 수 있는 컨트롤러를 구현하는 것이 연구의 목적이다. 디스플레이 기술의 발달로 인해 널리 사용되는, TFT-LCD의 동작원리를 이해하고 이 후 블록램을 통하여 TFT-LCD에 디스플레이 할 수 있는 방안에 대해 알아볼 수 있었다. 구현한 TFT-LCD 컨트롤러는 고속으로 동작 가능하며 적은 면적을 차지하므로 모바일 장치에 적용할 수 있을 것으로 판단된다.

#### 참고문헌

- [1] 송태훈, 김재석, "ARM926EJ-S Core를 이용 한 SoC 설계 및 임베디드 리눅스 활용" 홍릉과학 출판사 ,pp.295~333 ,2006

- [2] 이강, "VERILOG 2001 디지털시스템설계", pp.267~290, 2009

- [3] LTS350Q1-PD1 DATASHEET

- [4] Verification IP AMBA Platform User's Guide\_v2.0, Huins, inc.