# 위성 DMB의 CDMA 수신기를 위한 메모리 기반 Prefilter 구조

강형주\*

\*한국기술교육대학교

Memory-Based Prefilter Architecture for a CDMA Receiver of Satellite-DMB

Hyeong-Ju Kang\*

\*Korea University of Technology and Education

E-mail: hjkang@kut.ac.kr

## 요 약

CDMA는 IS-95, WCDMA, 위성DMB 등 다양한 표준에 사용되고 있는 통신 방식이다. 그러나, CDMA 방식에서는 근본적으로 다중 접속 간섭(MAI)를 피할 수 없어서 adaptive filter인 prefilter 같은 간섭 제거 기법이 요구된다. 본 논문에서는 CDMA 수신기에서 필수적인 prefilter의 면적을 줄이기 위해 메모리 기반 구조를 제안한다. 일반적인 adaptive filter는 레지스터로 구현하는 것이 면적을 줄이는 방법이나, prefilter는 그 기능의 특이성으로 인해 메모리 구조를 사용하는 것이 면적을 더 줄이는 방법임을 본 논문에서는 보일 것이다. 실험 결과, 통상적인 prefilter에서 레지스터에 기반한 구조에 비해 10%정도 면적을 줄일 수 있었다.

#### **ABSTRACT**

CDMA has been used widely in communication standards like IS-95, WCDMA, and Korea-Japan Satellite-DMB. Since CDMA has a multiple access interference (MAI) problem, a CDMA receiver requires an interference cancellation scheme like prefilter, a kind of adaptive filter. This paper proposed a memory-based prefilter architecture to reduce the area of a prefilter. An adaptive filter is usually implemented with registers for area reduction, but memory-based architecture leads to a less area for a prefilter due to its functional characteristics. Experimental results show that memory-based architecture reduces the area by around 10% in common prefilters.

### 키워드

CDMA, multiple access interference, prefilter

# 1. 서 론

CDMA는 IS-95, WCDMA, 위성DMB와 같은 많은 통신 표준에서 사용되고 있다. CDMA에서는 다중 접속 간섭(MAI) 문제를 피할 수 없어서, CDMA 수신기는 보통 이를 해결하기 위해 간섭제거기를 가지고 있다.[1,2] 간섭 제거기에는 여러가지가 있으나, 그 중에서 prefilter라 불리는 adaptive filter를 rake 앞에 두는 prefilter-rake 구조를 가장 많이 사용한다.

Prefilter의 기능이 다중 경로에서 오는 간섭을

제거하는 것이므로 이에 따라 prefilter의 특성도 결정된다. Prefilter의 중앙 탭은 주 경로에 해당하며, 다른 탭들은 제거하고자 하는 다중 경로에 해당한다. 그러므로, filter의 길이는 제거하고자 하는 다중 경로와 주 경로 사이의 거리에 의해 결정된다. 그리고, 계수가 0이 아닌 tap(active tap)의 개수는 제거하고자 하는 다중 경로의 개수에의해 결정된다. 보통 다중 경로는 성기게 분포하므로 active tap의 개수는 filter의 길이에 비해 매우 작다. 그리고, 다중 경로의 분포는 시간에 따라 변하므로 active tap의 위치도 역시 변한다.

Filter에는 delay-line이라 불리는 일련의 tap에 데이터를 저장한다. 이 delay-line은 filter의 다른 부분에 비해 연구가 많이 되지 않았는데, 그 이유는 delay-line의 면적이 상대적으로 작고, filter가 bandwidth를 많이 요구하므로 register 이 외에는 구현할 방법이 없었기 때문이다. 메모리 구조는 보통 충분한 bandwidth를 제공할 수 없기 때문에, 데이터율이 매우 낮은 filter에서, overclocking 비율을 많이 올린 상태에서만 이용되어 왔다.

그러나, prefilter에서는 active tap의 개수가 적기 때문에 delay-line 부분이 상대적으로 많은 면적을 차지한다. 그러나, prefilter의 delay-line에 대한 연구는 없었으며, active tap의 개수가 적은 adaptive filter에 대한 연구도 active tap의 위치결정 알고리즘에 집중되어 왔다. [3]

본 논문에서는 prefilter에 알맞은 메모리 기반 delay-line 구조를 제안한다. 대역폭이 부족한 문제는 같은 데이터를 여러 메모리에 복사해 넣어서 해결했다. 면적을 비교한 실험 결과를 통해 메모리 기반 구조가 레지스터 기반 구조에 비해 면적이 더 적음을 보일 것이다.

이 논문은 다음과 같이 구성되어 있다. 2장에서는 prefilter의 전체 구조에 대해 논하며, 3장에서는 제안하는 delay-line 구조에 대해 설명할 것이다. 4장에서 실험결과를 제시하고, 5장에서 결론을 맺을 것이다.

#### II. Prefilter 전체 구조

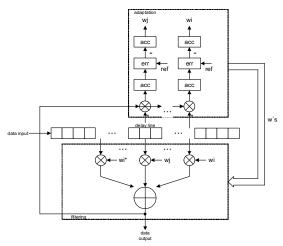

Prefilter는 adaptive filter로써, 일반적인 구조는 그림 1과 같이 filtering, adaptation, delay-line의 세 부분으로 나뉜다. Prefilter로 들어온 입력은 delay-line을 거치고, 이 데이터를 이용해서, adaptation부분에서 계수의 값을 결정하며, filter부분에서 실재 filtering을 한다. Prefilter의 계수들은 conjugate-symmetric한 성질을 가지고 있고, active tap 역시 대칭이다. 중앙 탭은 보통 존재하고 항상 active하므로, tap의 개수와 active tap의 개수를 2N+1과 2M+1이라고 표시해도 된다.

### Ⅲ. 제안하는 Delay-line 구조

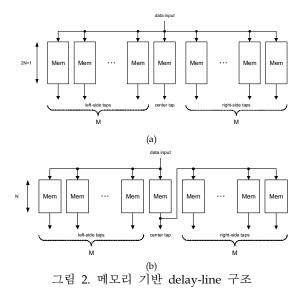

이 장에서는 이 논문에서 제안하는 delay-line 구조에 대해 논의할 것이다. 앞서 언급했듯이, 메모리 기반 구조는 메모리의 port 수가 제한됨에따라 대역폭이 작다는 문제점이 있다. 이를 해결하기 위해 그림 2와 같은 메모리 복사 방식을 사용하였다. Filter로 들어온 데이터는 여러 개의메모리에 동시에 써지며, 각각의 메모리는 자신에게 할당된 active tap에 데이터를 공급한다. 이 경우, delay-line의 면적은 메모리의 개수와 면적에의해 결정된다.

그림 1. Prefiler 전체 구조

메모리의 면적은 폭과 길이에 의해 결정된다. 메모리의 길이는, 어느 tap도 active가 될 수 있으 므로, 그림 2(a)와 같이 2N+1로 보일 수도 있다. 그러나, prefilter의 symmetric 성질을 이용하면, 이 길이를 줄일 수 있다. Symmetric 성질에 따르 면, active tap 중 절반은 중앙 탭 기준으로 왼쪽 에 존재하며, 이들에 해당하는 메모리들은 길이가 N이면 충분하다. 중앙 탭은 길이가 N+1인 메모 리로 지원할 수 있다. 중앙 탭에서 오른쪽에 있는 나머지 절반의 active tap들은, 해당하는 메모리들 의 입력을 중앙 탭의 메모리에서 가져옴으로써, 메모리의 길이를 N으로 줄일 수 있다. 결과적으 로 그림 2(b)와 같이 길이가 N인 메모리들만으로 구성할 수 있다. 중앙 탭은 길이가 N+1인 메모리 가 필요하나, 모든 메모리를 같은 길이로 맞추기 위해, 중앙 탭에 대한 메모리의 길이를 N으로 하 고 F/F을 하나 더 사용한다.

| N M Total area Delay line area Total area De | lay line area Total area Delay line area   |

|----------------------------------------------|--------------------------------------------|

|                                              | iay iilie alea Totai alea Deiay iilie alea |

| 192 10 1,072,315 485,251 1,007,987           | 421,055 0.940 0.868                        |

| 256 10 1,221,121 634,070 1,058,573           | 471,640 0.867 0.744                        |

| 384 10 1,519,968 932,925 1,160,580           | 573,635 0.764 0.615                        |

| 192 15 1,454,455 603,191 1,431,926           | 580,108 0.985 0.962                        |

| 256 15 1,637,345 786,039 1,501,439           | 649,663 0.917 0.827                        |

| 384 15 2,006,011 1,154,767 1,641,677         | 789,939 0.818 0.684                        |

표 1. 기존 구조와 제안하는 구조의 면적 비교

그림 3. OCR이 2일 때의 메모리 동작

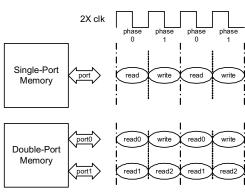

메모리의 개수는 하나의 메모리가 몇 개의 active tap을 지원할 수 있는가에 달려 있으며, 이는 overclocking 비율(OCR)에 따라 결정된다. OCR이 2이면 하나의 데이터 마다 두 cycle을 메모리를 읽고 쓰기 위해 사용할 수 있다. Single port 메모리의 경우, 그림 3과 같이, 두 cycle 중한 cycle은 메모리에 쓰기 위해 사용되므로 오직한 cycle만 메모리의 tap 데이터를 읽기 위해 사용할 수 있다. 즉, 2M+1개의 active tap을 지원하기 위해서는 2M+1개의 메모리가 있어야 한다.

Double port 메모리를 사용한다면, OCR이 2일 때, 하나의 데이터 당 4번의 읽기/쓰기 동작이두 cycle 동안 가능하다. 그림 3과 같이, 1번의 쓰기 동작과 3번의 읽기 동작을 수행한다고 하면, 2M+1개의 active tap을 지원하기 위해서 [(M+1)/3] + [M/3]개의 메모리가 필요하다. Double port 메모리 한 개의 크기가 single port 메모리의 두 배임을 고려하면, 메모리 전체 면적은 single port 메모리로 구성할 때 보다 약 2/3로 줄어든다. Port의 개수가 많은 메모리를 사용할수록 면적을 더 줄일 수 있으나, 실제로는 보통 double port 메모리까지만 사용할 수 있다.

# Ⅳ. 실험 결과

기존의 레지스터 기반 구조와 제안하는 메모리 기반 구조의 면적을 표 1에서 비교하였다. 위성 DMB에서 널리 이용되는, N = 192, 256, 384와 M = 10, 15인 prefiler들에 대해 비교하였다. OCR은 2일 때를 가정했으며, UMC Faraday 0.13um 라이브러리를 이용해서 Synopsys DesignCompiler로 합성하였다. 표에서 제시한 값은 NAND gate의 개수로 변환한 값이다.

실험 결과를 보면, delay line 면적의 경우 최대 38%로 면적을 줄일 수 있음을 알 수 있다. Delay line의 면적이 filter 전체 면적의 절반에 가까우므로, filter 전체 면적으로 보면 최대 19%로줄일 수 있다. 그리고 면적 감소 비율은 N이 클수록, 즉 prefilter의 면적이 클수록, 더 커짐을 알수 있다.

### V. 결 론

이 논문에서는 CDMA의 수신기에 사용되는 prefilter의 면적을 줄일 수 있는 구조를 제안하였다. 보통 filter들은 delay line을 register로 구현하나, prefilter의 특수한 성질들을 이용하면 memory에 기반한 저면적의 구조로 구현할 수 있다. 실험 결과를 통해, 위성 DMB에 사용되는 일반적인 prefilter의 경우, 최대 19%로 면적을 줄이는 효과가 있음을 알 수 있었다.

### 참고문헌

[1] K. Hooli, et al., "Performance evaluation of adaptive chip-level channel equalizers in WCDMA downlink," IEEE International Conference on Communications, vol. 6, pp. 1974-1979, June 2001.

[2] K. Hooli, et al., "Chip-level channel equalization in WCDMA downlink," EURASIP Journal on Applied Signal Processing archive, vol. 2002, pp. 757-770, Jan. 2002.

[3] J. H. Park, et al., "An efficient equalizer architecture using tap allocation memory for HDTV channel," IEEE International Workshop on System-on-Chip for Real-Time Applications, pp. 343-349, Jul. 2003.