# H.264 on-chip encoder 를 위한 programmable processor 성능 향상

이진용, 김경원, 허인구, 박상현, 김용주, 백윤흥 서울대학교 공과대학 전기컴퓨터 공학부

e-mail: {jylee, kwkim, igheo, shpark, yjkim}@optimizer.snu.ac.kr, ypaek@snu.ac.kr

# Performance Improvement of the programmable processor designed for H.264 on-chip encoder

Jinyong Lee, Kyungwon Kim, Ingoo Heo, Sanghyun Park, Yongjoo Kim, Yunheung Paek School of Electrical Engineering, Seoul National University

#### 요 약

H.264 부호기의 on-chip 상의 구현방법으로는 성능에 중점을 둔 ASIC (application specific integrated circuit) 기반의 접근 방식과 ASIC 보다 성능은 떨어지나 일반성과 유연성에 중점을 둔 ASIP (application specific instruction set architecture) 기반의 설계 방식이 연구되어 왔다. 우리는 영상 압축 응용 범위 내에서는 일반성 및 유연성을 잃지 않으면서도 기존에 문제시 되던 ASIP 의 성능은 대폭 개선할 수 있는 ISA 와 micro architecture 를 제안하고 구현한 바 있다. 본 논문의 핵심적인 기여는 이 ASIP의 추가적인 성능 개선이다.

#### 1. 서론

H.264는 최신의 비디오 압축 부호화 표준으로 [1] 보안 카메라와 같이 H.264 encoder가 on-chip으로 점차 구현되는 응용 영역이 확대되고 Encoder의 설계 방법은 ASIC (application specific integrated circuit) 기반과 ASIP(application specific instruction set architecture) 기반으로 나뉘게 되는데 ASIC기반의 설계는 성능과 전력 소모, 비용 등의 측면에서 뚜렷한 장점을 보이나 유연성 부족에 따른 NRE(non-recurring engineering) cost의 증가와 time-to-market에 대한 불리함이 외면하기 어려운 한계로 지적된다. 대안으로 ASIP 기반의 설계 방법이 제시되고 있는 추세이며[4], [10], [11], 우리가 [2]에서 제안한 ISA와 micro-architecture의 구현 역시 이러한 추세를 따르고 있다.

일반적인 ASIP instruction들의 granularity가 word-level인 반면 우리가 기존에 제안한 ASIP은 2차원의 논리적 메모리를 가정하고 4x2 행렬을 처리의 기본 단위로 삼아 성능을 크게 향상시켰다. 다만 2차원 메모리의 특정 위치에 접근하는 방식에 불필요한 오버헤드를 가지고 있었는데 이번 연구에서 이를 보완하였다.

이어지는 순서는 다음과 같다. 우선 2장에서 기본적인 배경 이론과 기존 연구가 간단하게 언급된다. 3장에서 우리가 [2]에서 제안한 ISA와 micro-architecture가 소개된다. 4장에서는 그 ISA 및 micro-architecture의 한계가 언급되고 본 논문의 핵심 기여가 설명될 것이다.

#### 2. Related work

그림 1 디지털 이미지의 표현

그림 1 은 디지털 이미지의 정량적 표현을 설명하고 있다. 픽셀의 속성을 나타내는 정수 성분의 행렬로 디지털 이미지가 표현되며 동영상 압축 부호화의 관건은 이러한 행렬들의 효과적인 압축이다.

기존 연구는 크게 ASIC 기반[5-8]과 ASIP 기반으로 나눠볼 수 있다.[4],[10],[11]

ASIC 기반이 저전력, 성능 및 비용 측면에서 강점이 있음은 분명하나, 유연성의 부족에 따른 NRE 비용의 증가와 time-to-market 의 불리함이 단점으로 지적되고 있다.

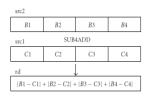

그림 2 는 ASIP 기반 연구의 전형을 보여주는데 낮은 granularity 가 유연성은 보장해 주지만 대상 application 을 동영상 부호화 응용으로 한정할 경우, 지나치게 일반적이어서 추가적인 성능 저하가 뒤따르게 된다.

# 그림 2 ASIP 기반 연구의 granularity, [11]에서

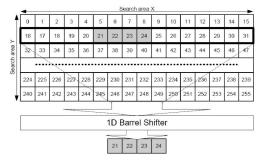

그림 32차원 메모리, 참고문헌 [9]

| В0 | BO | B0 | B0 | В0 | B0 | BO | BO |

|----|----|----|----|----|----|----|----|

| B1 |

| BO | BO | BO | B0 | В0 | BO | BO | B0 |

| B1 |

| B0 | BO | BO | В0 | В0 | BO | BO | В0 |

| B1 |

| B0 | BO | BO | B0 | В0 | BO | BO | B0 |

| B1 |

그림 42차원 메모리의 뱅크 분할

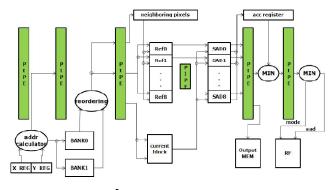

그림 5 micro architecture

# 3. 우리가 제안한 ISA와 micro-architecture

우리가 [2]에서 제안한 연구의 핵심은 논리적으로 메모리가 2차원 행렬로 보일 수 있도록 abstraction을 제공하고, SAD(Sum of Absolute Difference)의 계산을 4x2 행렬 단위로 한 사이클에 처리함으로써 속도 향상을 가져오는 것이다.

그림 3은 2차원 메모리의 개념과 근저의 구현을 나타내고 있다.[9] 우리는 [9]의 방법을 그대로 따르되, 그림 4와 같이 bank를 2개로 분리하여 x, y 두 개의 레지스터가 가리키는 위치에서 4x2 block을 한 사이클에 로드 할 수 있는 방법을 제안하였다. (그림 5) x, y 레지스터는 범용 레지스터를 소스로 하여 한 사이클에 로드된다. [2]의 방식에서는 다음 위치의 4x2 block을 처리하기 위해 x, y 레지스터를 새롭게 업데이트 해야 한다는 한계가 있다.

# 4. Load\_to\_x\_y의 개선 및 결론

Macro block은 16x16 단위이다. 이 매크로블록은 4x2 크기의 행렬들로 분할되어 접근된다. 이때 x, y의 stride는 임의의 값이 아니라 각각 4와 2이다. 따라서 16x16 크기의 매크로블록을 부호화 하기위해서 블록 단위의 계산을 수행하는 명령어에 추가로 각각 2비트와 3비트를 사용하면, 매번 x, y 레지스터를 업데이트 할 필요가 없다. 우리가제안한 ISA는 16 bit이고, 4x2 블록 단위 명령어는 10개 이하이므로 최대 5비트의 추가는 큰 오버헤드가 되지 않는다.

### 참고문헌

- Draft ITU-T Recommendation and Final Draft International Standard of Joint Video Specification (ITU-T Rec. H.264/ISO/IEC 11496-10 AVC), Mar. 2003.

- [2] 김경원, H.264 encoder 를 위한 programmable processor 개발, 서울대학교 공학석사학위 논문, 2009

- [3] <a href="http://www.videolan.org/developers/x264.html">http://www.videolan.org/developers/x264.html</a>

- [4] Marco Raggio, Massimo Bariani, Ivano Barbieri, Davide Brizzolar, "H.264 implementation on SIMD VLIW cores", STreaming Day 2007

- [5] C. W. Ku, C. C. Cheng, G. S. Yu, M. C. Tsai, and T. S. Chang, ""A high-definition H.264/AVC intra-frame codec IP for digital video and still camera applications," " IEEE Trans. Circuits Syst. Video Technol., vol. 16, no. 8, pp. 917–928, Aug. 2006.

- [6] D.-W. Li, C.-W. Ku, C.-C. Cheng, Y.-K. Lin, and T.-S. Chang, "A 61MHz 72K gates 1280x720 30FPS H.264 intra encoder", in Proceedings of the IEEE International Conference on Acoustics, Speech, and Signal Processing (ICASSP '07), vol. 2, pp. 801-804, Honolulu, Hawaii, USA, April 2007.

- [7] Y.-W. Huang, B.-Y. Hsieh, T.-C. Chen, and L.-G. Chen, "Analysis, fast algorithm, and VLSI architecture design for H.264/AVC intra frame coder", *IEEE Transactions of Circuits and Systems for Video Technology*, vol. 15, no. 3, pp. 378-401, 2005.

- [8] C.-C. Cheng, C.-W. Ku, and T.-S. Chang, "A 1280x720 pixels 30 frames/s H.264/MPEG-4 AVC intra encoder", Proc. IEEE International Symposium on Circuits and Systems, May. 2006.

- [9] MB Haverkamp, G Kuzmanov, S Vassiliadis, "Implementing 2D memory buffers for MPEG", PRORISC 2003

- [10] Kim, S. D., Lee, J. H., Hyun, C. J., and Sunwoo, M. H. 2006. "ASIP approach for implementation of H.264/AVC". In Proceedings of the 2006 Conference on Asia South Pacific Design Automation (Yokohama, Japan, January 24 27, 2006). with EDA Technofair Design Automation Conference Asia and South Pacific.

- [11] Zheng Shen, Hu He, Yanjun Zhang, and Yihe Sun, "A Video Specific Instruction Set Architecture for ASIP design", Hindawi Publishing Corporation, VLSI Design, Volume 2007, Article ID 58431, 7 pages

## Acknowledge

본 연구는 교육과학기술부/한국과학재단 우수연구 센터육성사업(R11-2008-007-01001-0), 지식경제부 출연 금으로 ETRI, SoC 산업진흥센터에서 수행한 ITSoC 핵심설계인력양성사업, 서울시 산학연 협력사업(10560), 2009 년도 정부(교육과학기술부)의 재원으로 한국과학재단의 국가지정연구실사업(No.2009-0083190)의 지원을 받아 수행되었습니다.