# 지역 버퍼를 활용한 부분 태그 캐시 구조

곽종욱\*, 전영태\*\*

\*영남대학교 컴퓨터공학과

\*\*LG전자 DM 연구소 MAS 그룹 e-mail:kwak@ynu.ac.kr

# Low-Power Partial Tag using Locality Buffer

Jong Wook Kwak\* and Young Tae Jeon\*\*

\*Department of Computer Engineering, Yeungnam University

\*\*MAS Group, DM R&D Center, LG Electronics

#### 요 약

내장형 시스템 시장의 확대는 시스템의 전체 성능 향상뿐만 아니라 전력 소모량을 줄이는 것도 고려하게 만들었다. 특히 시스템 내부적으로 많은 비중을 차지하는 캐시 시스템의 전력 소모량을 줄이는 것은 내장형 시스템 설계의 중요한 주제 가운데 하나로 부각 되었다. 본 논문에서는 태그 압축을 통한 저전력 캐시의 구현을 제안한다. 제안된 기법은 지역성이 높은 내장형 응용 프로그램의 특징을 활용한 것으로, 지역 버퍼와 태그 압축 비트를 활용하는 새로운 형태의 저전력 캐시용 태그 압축 기법이다. 모의실험 결과, 본 논문에서 제안된 기법은 시스템의 전체적인 성능 감소 없이, 기존 모델 대비 최대 27%, 평균 18%의 캐시 에너지 감소를 보였다.

#### 1. 서론

내장형 시스템에서 실행되는 응용 프로그램들은 실행 패턴의 높은 예측성과 동일한 메모리 접근 패턴을 가지는 지역성의 특징을 가진다. 이러한 특징은 해당 시스템의 에 너지 소비나 성능을 최적화할 수 있는 추가적인 기회를 제공한다. 내장형 시스템에서의 응용 프로그램 수행은 몇 개의 메모리 지역들로 나눠지며, 각각의 지역들은 메모리 영역의 작은 부분을 접근하게 된다. 이러한 사실은 단지 소수개의 태그 비트의 사용으로도 캐시의 접근에 있어서 충분하다는 것을 의미한다[1]. PowerStone 벤치마크에서, 사용되는 태그 비트 수의 변화에 따른 캐시의 적중률을 살펴보면 단지 5개 안팎의 태그 비트를 비교하는 것만으 로도 충분한 캐시 적중률을 얻을 수 있다는 것을 알 수 있다[2]. 특히 또 다른 연구에서는, 극단적으로 0개의 태그 비트를 사용한다 하더라도 2% 이하의 비교적 적은 성능 감소를 야기한다는 사실도 보고하고 있다[3]. 본 논문에서 는 이상의 사실을 바탕으로, 내장형 시스템에서의 응용 프 로그램들은 메모리를 참조할 때 높은 지역성에 의한 좁은 범위의 메모리 접근 분포 특성을 가진다는 사실을 이용해 캐시 메모리 시스템에서의 태그 부분에서 소비되는 에너 지를 줄일 수 있는 효율적인 방법을 제안한다.

# 2. 지역 버퍼를 활용한 부분 태그 캐시 구조

그림 1은 본 논문에서 사용될 캐시 접근 주소 형태를 나타낸다. n은 주소 비트, b는 오프셋 비트, s는 인덱스 비트, th와 tl은 각각 태그 비트들의 상위, 하위비트들의 크기를 나타낸다.

(그림 1) 캐시 접근 주소

암영이 넣어진 th는 응용 프로그램의 지역성을 나타내게 된다. 지역성이 높게 나타날수록 th는 길어지고 tl은 짧아진다. 태그 압축 캐시에서는 tl만 사용하게 되고 비트수가 줄어든 만큼 에너지를 절약할 수 있다. 나머지 th는 별도의 레지스터에 저장되는데, 본 논문에서는 이를 지역버퍼(locality buffer)라 한다.

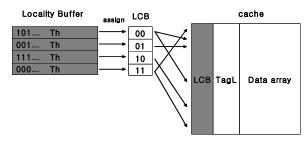

그림 2에 제시되어 있는 지역버퍼는 몇 개의 라인을 가지고 있고, 그 개수에 따라 할당되는 지역 압축 비트 (LCB)가 결정된다. 이로써 비교되는 태그는 지역 버퍼에 쓰이는 비트를 제외한 나머지 하위 비트들과 지역 압축 비트들을 더한 것이 되고 그만큼의 태그를 적게 쓰기 때문에 에너지 소모를 줄일 수 있게 된다.

(그림 2) 지역 버퍼

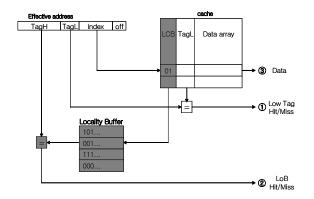

(그림 3) 저전력 부분 태그 캐시 구조

태그 압축 캐시의 동작은 그림 3과 같다. 먼저 색인 (index)으로 캐시를 접근하게 된다. 이 때 태그 비교는 하위의 부분태그로 행해지며, 접근 실패가 되면 기존 캐시의실패처럼 동작한다. 이후 외부 메모리에서 올바른 값이 오면 해당 라인을 갱신한다. 하위태그 비교가 적중되었다면해당라인의 지역 압축 비트를 보고 지역버퍼를 접근하게된다. 그 다음, 지역버퍼에 저장된 값과 상위태그를 비교해서 성공 여부를 가린다. 성공되었다면 비로소 접근했던캐시의 값은 유효하게 되고 캐시접근은 끝나게 된다. 반대로 실패가 되면 나머지 지역 버퍼에 같은 값이 있는지 살펴보게 된다. 같은 값을 찾게 되면 캐시의 값은 유효하며해당 캐시라인의 지역압축비트만 바꿔주면 된다. 나머지지역 버퍼에도 원하는 값이 없었을 경우에는 캐시의 모든라인을 참조하여 교체과정을 진행한다.

### 3. 모의 실험 및 성능 분석

본 논문의 검증을 위해서, 슈퍼스칼라 프로세서의 사이클 수준 시뮬레이터인 SimpleScalar ARM 버전을 사용하여 모의실험을 실시하였다. SimpleScalar ARM 버전은 기존의 SimpleScalar 시뮬레이터에 ARM 바이너리로 컴파일된 프로그램을 실행하기 위해 ARM ISA(Instruction Set Architecture)의 지원이 가능하도록 개조되었다[4]. 또한, 전력소모량의 측정을 위해서 CACTI 3.0을 사용하였으며, 0.18um 기술을 가정하였다[5]. 본 논문에서의 벤치마크 프로그램은 EEMBC를 참고하여 만든 공개용 벤치마크인 MiBench를 사용한다[6].

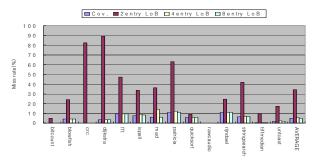

(그림 4) 지역 버퍼수에 따른 접근 실패율

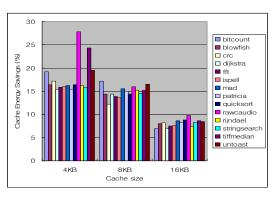

그림 4는 지역버퍼의 엔트리 수에 따른 실패율을 나타 낸다. 지역 버퍼의 엔트리 수가 늘어나면 그 자체로 하드 웨어적 오버헤드가 될 뿐만 아니라 그만큼 캐시라인마다 저장되는 지역압축비트의 수도 늘어나게 된다. 이럴 경우, 성능저하는 없더라도 전력소비의 효율성은 감소한다. 따라 서 적절한 지역버퍼 엔트리 수의 결정은 중요하다. 그림 4 에서 나타나듯이 지역버퍼의 엔트리 수가 4개일 때는 기존 캐시에 비해 약 0.8%의 차이를 보이며 8개일 때는 약 0.08%의 차이를 보인다. 즉 4개의 지역버퍼를 사용하는 것이 바람직하다고 판단된다. 그림 5는 캐시의 크기에 따른 전력소모량을 나타낸다. 캐시의 크기가 4KB일 때 최대 27%, 평균 18%의 전력량을 줄일 수 있었으며, 8KB와 16KB의 캐시에서도 평균 13%와 9%의 전력량을 줄일 수 있었다.

(그림 5) 캐시의 크기에 따른 전력 소모량

### 4. 결론 및 향후 연구 방향

본 논문에서는 캐시 태그 압축을 통한 소비 전력 감소 방안을 제안하였다. 제안된 기법은 높은 지역성을 보이는 내장형 프로그램들의 특성을 이용하며, 전체 태그를 사용 했을 때보다 성능의 감소 없이 최대 27%, 평균 18%의 캐 시 에너지를 줄일 수 있었다.

## 참고문헌

- [1] D. Patterson et al., "Computer architecture: a quantitative approach" (Morgan Kaufman, 2007, 4th Ed.)

- [2] A. Malik et al., A Lower power unified cache architecture providing power and performance flexibility. ISLPED. 2000

- [3] A. Malik et al., "A Lower Power Unified Cache Architecture Providing Power and Performance Flexibility," ISLPED, 2000, pp. 241~243

- [4]. SimpleScalar LLC, http://www.simplescalar.com/

- [5] P. Shivakumar et al., "An integrated cache timing, power and area model", Tech. Report, Compaq Western Research Lab, Palo Alto, CA, 2001/2

- [6] M. Guthaus et al. "MiBench: A free, commercially representative embedded benchmark suite", IEEE International Workshop on Workload Characterization, 2001. WWC-4. 2001, pp. 3~14, Dec. 2001