# Phase Shift Full Bridge Converter for Sever Power using a New Separated Leakage Inductor Winding (SLW) Method

Kyu-Min Cho, Young-Do Kim, In-Ho Cho and Gun-Woo Moon

Department of Electrical Engineering and Computer Science, KAIST 373-1 Guseong-Dong, Yuseong-Gu Daejeon 305-701, Korea

#### **Abstract**

A new transformer winding method is proposed in this paper. Generally, PWM ZVS topologies use a leakage inductor to achieve ZVS operation. However, the leakage inductance of the transformer is not often enough to meet ZVS condition. Therefore, an additional leakage inductor is necessary, which causes large core loss because high input voltage is applied to the additional leakage inductor during a short commutation period. In this paper, a new separated leakage inductor winding (SLW) method is proposed. With the proposed winding method, a leakage inductor and a transformer can be combined in one ferrite core. Therefore, size and core loss of the additional leakage inductor can be reduced. Experimental results demonstrate that the proposed winding method can achieve a significant efficiency improvement in a 1210.8W (12V, 100.9A) prototype converter.

#### 1. Introduction

Sever computer technologies has been dramatically developed in past decades. There are two factors which lead this development. One is expanded consumer market. Developments of semiconductor technologies lead cost reduction of sever computer systems. As a result, anyone who consider to use sever computers can buy it with reasonable expense. The other is increased data size. As data which the company has to process is increased, even small company also needs sever computer. Based on these factors, many sever computer types such as tower types, rack types and blade types are introduced. Among these, blade type sever is very popular because of its scalability.

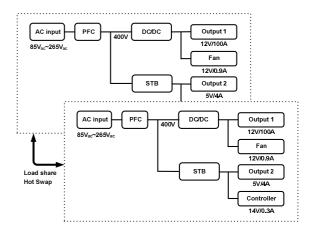

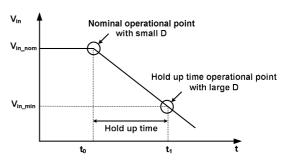

Fig. 1 shows the block diagram of the sever power system. It is consisted of EMI filter, power factor correction circuit (PFC), DC/DC converter, stand-by circuit, fans and micro processor. DC/DC converters of the sever power system have to satisfy following three requirements. First, high input voltage operation is required. As the restriction on the harmonic distortion such as IEC 61000-3-2 is getting strict, PFC circuits are mandatory to all electronic appliances. Since typical PFC circuits adopt boost type converters, the output voltage of the PFC circuit is about 400V when universal ac input (85V<sub>ac</sub>~265V<sub>ac</sub>) is applied. It makes it difficult to apply forward converter or push-pull converter to sever power system. Second, low output voltage and large output current are required. To reduce the power consumption, most of the processors are operated with low input voltage. Total power is also increasing to meet various needs of users, which induces large output current. Therefore, synchronous rectifiers (SRs) are necessary. Third, the output voltage has to be maintained for 20ms when AC input line is turned off, which is called hold up time. Fig. 2 shows the operating point of DC/DC converters of the sever power system. Therefore, it has to be operated with small duty ratio in nominal state to satisfy the hold up time. It makes it

Fig. 1 Block diagram of the sever power system

Fig. 2 Operational point by hold up time

difficult to apply half bridge converters for sever power system.

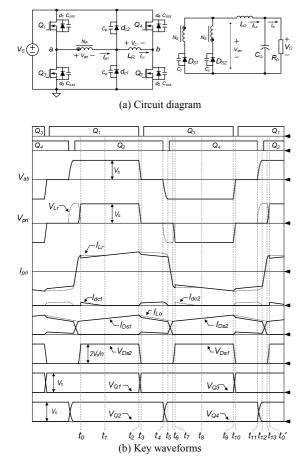

For these reasons, full bridge type converters are mainly used in sever power systems. Fig. 3 shows the most attractive phase shift full bridge (PSFB) converter which has primary clamp diodes to reduce the voltage ringing of SRs. This circuit has two big merits as follows. First, the additional resonant inductor guarantees ZVS operation of lagging leg switches. Second, two clamp diodes in primary side separates the additional resonant inductor from voltage ringing mechanism of SR when commutation period of SRs is finished. Therefore, it is possible to use SRs with low voltage stress and low on resistance. On the other hand, the additional resonant inductor increases size, cost and core loss.

In this paper, a new separated leakage inductor winding (SLW) method is proposed. The proposed winding method can combined the additional leakage inductor and transformer in one ferrite core. Therefore, it can reduce size and core loss of the additional leakage inductor. The theoretical analysis, design and experimental results are presented to confirm the validity of the proposed SLW method

Fig. 3 PSFB with primary clamp diode

### 2. Proposed SLW method

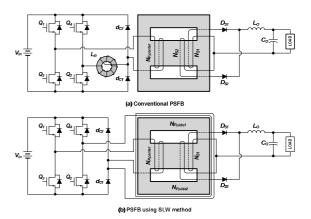

Fig. 4 shows the conventional PSFB converter and the proposed PSFB converter using SLW method. Generally, the conventional PSFB used toroidal core as an additional resonant inductor as shown Fig. 4. The core loss of the magnetic component is composed of three parts which are hysteresis loss, eddy current loss and excess eddy current loss. According to recent research performed by Waseen A. Roshen [1], an abrupt voltage variation like rectangular waveform makes large eddy current loss and excess eddy current loss compared to sinusoidal waveforms. The ratio can be express as follows:

$$\frac{P_{c}^{square}}{P_{c}^{sin}} = \left\{ \frac{A}{8\pi\rho} (4fB_{o})^{2} \frac{1}{D} \right\} / \left\{ \frac{A}{16\pi\rho} (2\pi fB_{o}) \right\} = \frac{8}{\pi^{2}D} \tag{1}$$

$$\frac{P_{ex}^{square}}{P_{ex}^{sin}} = \left\{ 3.5 \sqrt{\frac{2\pi A\alpha n_{o}}{\rho}} (fB_{o})^{3/2} \right\} / \left\{ 8 \sqrt{\frac{A\alpha n_{o}}{\rho}} (fB_{o})^{3/2} \frac{1}{\sqrt{D}} \right\}$$

$$= \frac{4}{3.5} \sqrt{\frac{2}{\pi}} \frac{1}{\sqrt{D}}$$

(2)

where  $B_o = \frac{V_o}{2\pi fNA}$

From (1) and (2), it can be seen that eddy current loss is dominant loss in the additional resonant inductor. Generally, the additional resonant inductance is designed small as possible if it could guarantee the ZVS operation. As a result, the commutation period in which the input voltage is applied to the resonant inductor becomes very short. It makes about 7 times larger core loss in the resonant inductor compared to core loss which is measured with sinusoidal voltage in a datasheet. That is the reason that the additional resonant inductor is bulky in the commercial power

Fig. 4 Conventional PSFB and proposed PSFB using SLW method

conversion system.

The proposed SLW method makes additional resonant inductor using outer side of transformer. It has no flux link with primary winding and secondary winding because magnetic flux meets at right angle to each other. Therefore, inductance made by outer side wining is independently operated like a bar type inductor. An additional resonant inductor made by SLW method has a large area of cross section. Therefore, it has very small eddy current loss and excess eddy current loss even if rectangular voltage applies to the resonant inductor.

# 3. Design Consideration of PSFB using SLW Method

To validate the characteristics of the proposed transformer winding, design equation are derived with the sever power system specification as follow:

• input voltage Vin :  $400V_{dc}$

• Output voltage V<sub>o</sub>: 12V, 100.9A

• Maximum output power  $P_{o,max}$ : 1210.8W

• Switching frequency fs: 86kHz

• Input Capacitor C<sub>in</sub>: 990uF

• Hold up time thold-up: 20ms

## A. Maximum input voltage during the hold up time, $V_{in,min}$

Sever power system has to satisfy the hold up time in which the output voltage is maintained for 20ms when AC input line is turned off. Therefore, voltage of the input capacitor is operated as the input source of DC/DC converter when AC input line is turned off. Therefore, the DC/DC converter of sever power system has wide input variation although it has power factor correction circuit. The input voltage variation can be expressed as follows:

$$V_{in,\text{min}} = \sqrt{V_{in,nom}^2 - \frac{2P_o \times t_{hold-up}}{\eta \times C_{in}}}$$

It is assumed that the input capacitor is 990uF and hold up time is 20ms. The DC/DC converter has to regulate output voltage with 0.5 duty ratio at 328V input voltage.

#### B. Turn ratio of the transformer, $n=N_p/N_{sx}$

When the minimum input voltage is applied, sever power system is operated with maximum duty ratio. Therefore, turn ratio of the transformer,  $n=N_p/N_s$  can be expressed as follows:

$$n = \frac{N_p}{N_o} = \frac{2V_o}{D_{max}V_{in min}} \tag{3}$$

#### C. Additional resonant inductor

For the convenience of design, the ripple current of the magnetizing inductor is assumed to zero. From Fig. 2, the ZVS condition can be expressed as  $(L_{lkg} + L_R)i_{Lr}^2(t_2) \ge 2C_sV_{in}^2$  and can be rewritten as follows:

$$i_{Lr}(t_2) \ge \sqrt{\frac{2C_s}{L_{lkg} + L_R}} V_{in}$$

It is assumed that the output capacitance of power switch, Cs is 780nF. To achieve the ZVS operation at half load condition,  $L_{\rm lkg} + L_{\rm R}$  is selected to 10uH.

$\tilde{T}$ able 2 shows the resonant inductance which is made by SLW method. It can be seen that the measured inductance is proportional to  $N^2$ . Outer turns are selected to 5.75 turns to meet ZVS operation at 60% load condition.

#### 4. Experimental Results

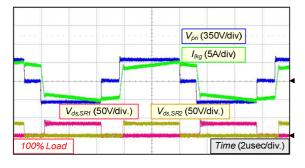

Based on the design equation in the preceding section, a prototype of 12V, 1200W converter is constructed using the components as shown in Table 2. Fig. 5 shows the experimental waveforms of the primary side of the transformer and it clearly verifies the ZVS operation of all switches. Fig. 8 shows the voltages and gate signals of SRs. Since it has clamp diodes in primary side of the transformer, only leakage inductor of transformer can affect the voltage ringing of SRs as described in the preceding section.

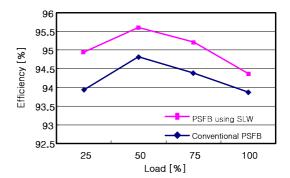

Fig. 6 shows the efficiency of the proposed converter and difference of power loss between the proposed converter and conventional converter. As can be seen in Fig. 6, the proposed SLW method can obtain 0.5% higher efficiency than conventional PSFB. This high efficiency indicates the proposed transformer winding method can dramatically reduce the core loss of the additional resonant inductor.

# 5. Conclusion

This paper presented a new transformer winding method. The additional resonant inductor is necessary to achieved ZVS operation in ZVS PWM topologies. However, it has large core loss and large size because high voltage is applied to it during very short commutation period. The proposed winding method can combine transformer and additional resonant inductor on one magnetic core. Therefore, it can reduce core loss, size and cost of the additional leakage inductor. The experimental results of a 1210.8W (12V, 100.9A) prototype converter shows the validity of the proposed transformer winding method. Therefore, the proposed transformer winding method is very effective for all ZVS PWM topology using additional resonant inductor.

Fig. 5 Key experimental waveforms

Fig. 6 Efficiency comparison with load variation

Table 1. Used component list

| Outer turns | Inductance | Outer turns | Inductance |

|-------------|------------|-------------|------------|

| 0.75        | 250nH      | 4.75        | 4.27uH     |

| 1.75        | 790nH      | 5.75        | 6.07uH     |

| 2.75        | 1.56uH     | 6.75        | 8.25uH     |

| 3.75        | 2.8uH      | 7.75        | 10.81uH    |

Table 2. Used component list

| Table 2. Osed component list                                                   |            |  |  |

|--------------------------------------------------------------------------------|------------|--|--|

| Switching frequency (fs)                                                       | 86kHz      |  |  |

| Primary switches                                                               | SSP20N60C3 |  |  |

| Primary clamp diode                                                            | ES1J       |  |  |

| Turn ratio of transformer (N <sub>p</sub> :N <sub>s1</sub> : N <sub>s2</sub> ) | 24:1:1     |  |  |

| Magnetizing inductance (L <sub>m</sub> )                                       | 1.68mH     |  |  |

| Leakage inductance (L <sub>lkg</sub> )                                         | 6.7uH      |  |  |

| Additional resonant inductance (L <sub>R</sub> )                               | 6.07uH     |  |  |

| Synchronous rectifiers                                                         | IRFB3907   |  |  |

| Output inductance                                                              | 1.2uH      |  |  |

| Output capacitance                                                             | 990uF      |  |  |

#### Reference

- [1] Waseem A. Roshen, "A Practical, Accurate and Very General Core Loss Model for Nonsinusoidal Waveforms", IEEE Transaction on Power Electronics, Vol 22, No.1, pp30~40, 2007, January.

- [2] Richard Redl, Nathan O. Sokal, Laszio Balogh, "A Novel Soft-Switching Full-Bridge DC/DC Converter: Analysis, Design Considerations, and Experimental Results at 1.5kWm 100kHz", IEEE Transaction on Power Electronics, Vol 6, No.3, pp408~418, 1991, July.

- [3] Yungtaek Jang, Milan M. Jovanovic, Dave L. Dilman, "Hold-Up Time Extension Circuit With Integrated Magnetics", IEEE Transaction on Power Electronics, Vol 22, No.2, pp394~400, 2006, March.

- [4] Wu Chen, Xinbo Ruan, Rongrong Zhang., "A Novel Zero-Voltage-Switching PWM Full Bridge Converter", IEEE Transaction on Power Electronics, Vol 23, No.2, pp793~801, 2008, March.

- [5] Gwan-Bon Koo, Gun-Woo Moon, Myung-joong Youn, "New Zero-Voltage-Switching Phase-Shift Full-Bridge Cnverter With Low Conduction Loss Losses", IEEE Transaction on Industrial Electronics, Vol 52, No.1, pp228~235, 2005, February.