# 공진요소를 포함한 고전압 플라이백 컨버터의 특성해석

고태석, 정용준, 이재광, 정동열, 한상규, 홍성수, 김진욱\*, 이효범\*, 노정욱 국민대학교 전력전자 연구소, 삼성전기 (주) P&m 사업부\*

## A Characteristic Analysis of High Voltage Flyback Converter including Resonant Element

Tae-Seok Ko, Yong-Joon Jung, Jae-Kwang Lee, Dong-Yeol Jung, Sang-Kyoo Han, Sung-Soo Hong, Jin-Wook Kim\*, Hyo-Bum Lee\*, Chung-Wook Roh Kookmin University Power Electronics Center, Samsung Electro-Mechanics Co. LTD.\*

#### **ABSTRACT**

본 논문은 공진요소를 포함한 고전압 플라이백 컨버터의 설계 절차를 제시하는 것으로써, 고압 플라이백 컨버터 설계 시기존 플라이백 컨버터의 Power Stage 설계 식을 적용하였을 때 원하는 출력 전압을 얻지 못한다. 고전압을 발생시키기 위한 고전압 플라이백 변압기는 2차 측의 많은 권선수와 높은 전압 때문에 기생 커패시턴스(parasitic capacitance)가 매우 크고, 과도상태에서 컨버터 전류 및 전압의 기생 공진(parasitic resonance)이 심각하게 발생한다. 이러한 공진요소를 고려하여고전압 플라이백 컨버터의 특성을 해석하고 설계 절차를 제시한다. 이를 통해 고전압 플라이백 컨버터의 소형화 및 경량화를 도모하고, 고압 전원장치의 기술 축적을 위해 연구되었다. 제안된 회로의 동작원리를 설명하고, 타당성을 실험을 통하여검증한다.

## 1. 서 론

일반적으로 플라이백 컨버터는 적은 수의 소자와 간단한 제어방식, 다출력 구성이 용이하다는 장점 때문에 중소형 용량의회로방식에 적극 이용 되고 있다.<sup>[1]</sup> 특히 플라이백 회로의 스위치에 흐르는 전류가 불연속 모드에서 동작하는 경우 자연스럽게 영전류 스위칭이 가능하기<sup>[2]</sup> 때문에 소용량에서 대용량까지폭넓게 이용되고 있다.

고전압 플라이백 컨버터의 설계에 있어서 Power Stage 설계에 관한 사항은 제공된 바가 없는데, 이유는 HVPS(High Voltage Power Supply) 설계 시 기존 플라이백 컨버터의 Power Stage 설계 식을 적용하였을 때 원하는 출력 전압을 얻지 못하기 때문이다. 고전압을 발생시키기 위한 고전압 플라이백 변압기는 2차 측의 많은 권선수와 높은 전압 때문에 기생커패시턴스(parasitic capacitance)가 매우 크고, 과도상태에서 컨버터 전류 및 전압의 기생 공진(parasitic resonance) 집에 심각하게 발생한다. 이런 기생공진이 스위칭 디바이스에 전류 스트레스를 증가시키고 컨버터의 스위칭 주파수를 제한하는 요소로 작용한다. 제안된 방식은 기존 방식에 비해 제어 방식이나설계가 복잡하지만, HVPS 의 소형화 및 경량화를 도모하고,고압 전원장치의 기술 축적을 위해 연구가 필요한 방식이다.

본 논문에서는 이러한 공진형 플라이백 컨버터의 동작원리, 설계 과정 그리고 실험결과를 제시하여 그 타당성을 검증한다.

## 2. 공진요소를 포함한 플라이백 컨버터 동작특성

#### 2.1 회로구성

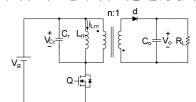

그림 1은 공진요소를 포함한 높은 전압 변환 비를 갖는 DC/DC 플라이백 컨버터의 회로도이다. 회로의 구성은 일반적은 플라이백 컨버터와 유사하고(스위치Q, 자화 인덕턴스  $L_m$ , 출력 다이오드 d, 출력 커패시터  $C_0$ 로 구성됨), 공진요소를 포함하기 위해 스위치 기생 커패시터  $C_p$ , 다이오드 기생 커패시터  $C_p$ , 다이오드 기생 커패시터  $C_p$ , 다이오드 기생 커패시터  $C_p$ , 모유용량  $C_{ws}$ 를 고려하였다. 높은 전압 변환비를 가져트랜스포머의 1차 측 대 2차 측 권선비가 큰 것(n 이 1보다 작음)이 특징이다. 여기서 n은 트랜스포머의 2차 측 권선수대 1차 측 권선수의 비이다. 트랜스포머의 권선비가 큼에 따라 트랜스포머 포유용량( $C_{ws}$ ) 등의 2차 측 커패시턴스 성분을 1차 측에서 바라봤을 때, 일반적인 플라이백 컨버터와 비교하여 큰 기생 커패시턴스 값을 가지게 된다. 이 기생 커패시턴스 성분과 자화 인덕턴스의 공진으로 인하여 비교적 큰 공진구간이 존재하게 된다.

그림 1의 C값은 스위치 기생 커패시터  $C_p$ , 다이오드 기생 커패시터  $C_s$ , 포유용량  $C_w$ 를 하나의 공진 커패시터 성분으로 변환한 값으로 식 (1)과 같이 나타난다.

$$C_r = C_p / \frac{C_{ws}}{n^2} / \frac{C_s}{n^2} \tag{1}$$

## 2.1.1 동작 원리

제안된 회로의 동작을 살펴보기 위해 다음 사항을 가정한다. - 모든 반도체 소자는 이상적이다.

- 회로는 정상상태에서 동작한다. 자화 인덕턴스  $L_m$ 의 전류는 Boundary Conduction Mode(BCM) 로 동작하고 스위치 도통시 영전압 스위칭(ZVS)을 한다.

- 커패시턴스  $C_o$  의 값이 충분히 커서 커패시터에 인가되는 양단 전압은  $V_o$  의 DC 전압으로 근사화 할 수 있다.

- 스위칭 주파수 대 공진 주파수 비율  $f_{ns}(f_{s}/f_{o})$ 와 일차 측으

그림 1 공진요소를 포함한 플라이백 컨버터

로 반영된 로드저항과 특성 임피던스 비율  $Q_p(n^2R_I/Z_0)$ 을 정의한다. 여기서 특성 임피던스  $Z_0$ 는  $L_m/C_r$ 이다.

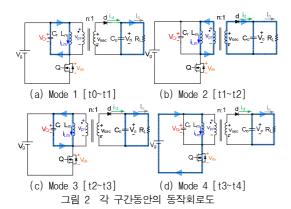

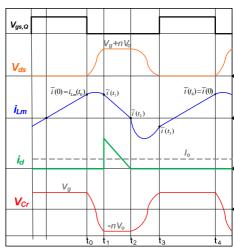

공진요소를 포함한 플라이백 컨버터를 그림 2와 같이 4개의 동작모드로 나타낼 수 있다. 그림 3는 각각의 모드에 대한 각 부 주요 전압, 전류 파형도이며, Mode 1에서 Mode 4까지가 반 복된다.

#### **Mode 1** [ $t_0 \sim t_I$ , Resonant Interval]

$t=t_o$  이전구간에서는 스위치(Q)가 도통되어있다.  $t=t_o$ 에서 스위치가 턴-오프 될 때, 입력 에너지가 자화 인덕턴스  $L_m$ 에 선형적으로 충전되던 이전 구간이 종료된다. 이 공진구간동안 경로  $L_m-C_r$ 을 통해 자화 인덕턴스  $L_m$  전류가 그림 3과 같이 흐르게 된다.

#### **Mode 2** [ $t_1 \sim t_2$ , Discharging Interval]

$t=t_{I}$ 에서 공진 커페시터 C의 전압이  $-nV_{o}$ 까지 도달하게 되면, 2차 측의 출력 다이오드가 도통하는 조건이 된다. 출력 다이오드가 도통하면  $L_{m}$ 에 충전된 에너지가 2차 측으로 전달된다. 이 구간동안 자화 인덕턴스의 전류가 출력 측으로 전달되는 경로는  $L_{m}-d-C_{o}$ 이다. 출력 측으로 에너지를 다 전달하게되면 이 모드는 끝난다.

#### **Mode 3** [ $t_2 \sim t_3$ , Resonant Interval]

$t=t_{2}$ 는  $L_{m}$ 전류가 0A로 도달하여 출력 다이오드가 차단되는 시점이다. 이 공진구간에서는 경로  $L_{m}$ — $C_{r}$ 을 통해 자화 인덕턴  $\triangle$   $L_{m}$  전류가 그림 3과 같이 음의 방향으로 흐르게 된다. 자화 인덕턴스  $L_{m}$ 의 초기 전류는 0A이고, 공진 커패시터  $C_{r}$ 의 전압 은  $-nV_{r}$ 에서  $V_{g}$ 까지 상승하게 된다. 이 때, 스위치의  $V_{ds}$ 전압 은  $V_{g}$ + $nV_{r}$ 에서 0까지 하강하게 되어 스위치의 body diode 가도통하므로 ZVS 할 수 있는 조건이 된다.

## **Mode 4** [ $t_3 \sim t_4$ , Charging Interval]

$t=t_d$ 는 스위치가 도통되는 시점이다. 이 때, 스위치의 양단전 압  $V_{ds}$ 가 0이므로 스위치는 영전압 스위칭을 한다. 이 구간에서 경로  $V_g-L_m-Q$ 의 전류 패스를 통해 입력의 에너지가 자화 인덕턴스에 전달된다. 자화 인덕턴스  $L_m$ 의 전류는 직선의 기울 기로 상승한다. 공진 커패시터 C의 전압은  $V_g$ 를 유지한다.

## 2.1.2 입출력 관계식

공진요소를 포함한 DC/DC 플라이백 컨버터의 회로도의 입출력 관계식은 앞서 설명한 각 모드별  $i_{lm}(t)$ 값을 정리하여 식을 구하면 식 (2)와 같고 도출된 입출력 관계식을 살펴보면, 두개의 공진구간인  $t_1-t_0$ ,  $t_3-t_2$ 가 0이면 식 (3)과 같이 일반적인 BCM 모드의 DC/DC 플라이백 컨버터 입출력 관계식과 동일함을 확인할 수 있다.

그림 3 각 구간동안의 주요파형

$$\begin{split} &\frac{V_o}{V_g} = \frac{1}{n} \frac{\theta_4 \cos\theta_1 + \sin\theta_1}{\theta_2 + \cos\theta_1 \sin\theta_3} \\ &= \frac{1}{n} \frac{(t_4 - t_3) \cos\frac{(t_1 - t_0)}{\sqrt{L_m C_r}} + \sqrt{L_m C_r} \sin\frac{(t_1 - t_0)}{\sqrt{L_m C_r}}}{(t_2 - t_1) + \sqrt{L_m C_r} \cos\frac{(t_1 - t_0)}{\sqrt{L_m C_r}} \sin\frac{(t_3 - t_2)}{\sqrt{L_m C_r}}} \end{split} \tag{2}$$

$$\frac{V_o}{V_g} = \frac{1}{n} \frac{(t_4 - t_3)}{(t_2 - t_1)} = \frac{1}{n} \frac{D}{1 - D}$$

(3)

여기서,  $D=t_2-t_3$ 으로 정의하고  $1-D=t_2-t_1$ 으로 정의한다. 'D는 스위치 도통 시의 시비율 이고, '1-D는 스위치 차단 시의 시비율 이다.

## 2.2 설계방법

앞서 설명한 해석을 바탕으로 공진요소를 포함한 높은 전 압 변환 비를 가지는 DC/DC 플라이백 컨버터의 설계 절차를 제시한다.

Step 1 컨버터 사양 확정: 입력 전압  $V_{in}$ , 출력 전압  $V_o$ , 출력 전압  $P_o$ , 스위칭 주파수  $P_o$ , 스위칭 기생 커패시터  $P_o$ , 다이 오드 기생 커패시터  $P_o$ , 예상되는 최소의 포유용량  $P_o$  작가 다음 사양들을 확정한다.

**Step 2** *Q*<sub>0</sub>와 *f*<sub>ns</sub> 선택: 스위치의 Power Loss를 제일 우선으로 고려한다.

Step 3 M과  $\Theta_{I}$   $\Theta_{4}$  도출: 선택한  $Q_{p}$ 와  $f_{ns}$  에 따른 입력 대일차 측으로 반영된 출력 비 M과 각 구간의 위상 정보  $\Theta_{I}$   $\Theta_{4}$  가 비선형 5월 5차 방정식을 통해 구해진다.

**Step 4** 턴 비, *L<sub>m</sub>*, *C*,의 공진 설계 값 도출: 위 과정에서 도출된 *M*을 통하여 턴 비를 구하는 식은 식 (4)와 같다.

$$n = M \frac{V_g}{V_c} \tag{4}$$

식 (4)로부터 구해진 턴 비와  $Q_p$ ,  $f_{ns}$ 를 이용하여 식 (5)와 같이 특성 임피던스  $Z_o$ , 공진 주파수  $f_o$ 를 구한다.

$$Z_o = \frac{n^2 R_L}{Q_p}, \quad f_o = \frac{f_s}{f_{ns}} \tag{5}$$

식 (5)로부터 구해진 특성 임피던스와 공진 주파수를 이용하여 식 (6)과 같이 자화 인덕턴스  $L_m$ 과 공진 커패시터  $C_r$ 을 구할 수 있다.

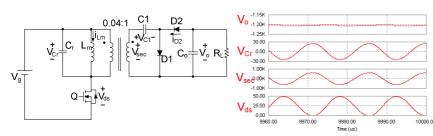

그림 4 플라이백 컨버터 예제 회로

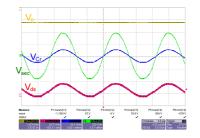

그림 5 시뮬레이션 결과 파형과 실험 결과 파형

$$L_m = \frac{Z_o}{2\pi f_o}, \qquad \qquad C_r = \frac{1}{2\pi Z_o f_o} \label{eq:crossing}$$

(6,

여기서 공진 커패시터  $C_{\alpha}$ 값이 입력 데이터에 주어진 스위치기생 커패시터  $C_{p}$ 와 일차 측으로 반영된 다이오드 기생 커패시터  $C_{s}$ , 포유용량  $C_{ws}$ 의 합인  $C_{r,min}$ 보다 큰 값인지 여부를 확인한다. 만약 공진 커패시터  $C_{r}$ 이  $C_{r,min}$ 보다 작으면 Step 2 과정을 반복한다.

Step 5 스위치 전압 및 전류 스트레스: 전류 피크 값과 스위치 차단 시 양단 최대전압, 출력 다이오드 차단 시 양단 최대전압을 구한다. 반도체 소자의 사양을 구한 값을 참조하여소자를 선정한다. 여기서 전류 피크는 식 (7)과 같이 표현되고,스위치 차단 시 양단 최대전압, 출력 다이오드 차단 시 양단최대전압은 식 (8)과 같다.

$$i_{Lm,pk} = \sqrt{\left(\frac{V_g}{Z_o}\right)^2 + \left(\tilde{i}(0)\right)^2} \tag{7}$$

$$V_{ds, \text{max}} = V_g + n V_o, \quad V_{d, \text{max}} = V_o + \frac{1}{n} V_g$$

(8)

## 2.2.1 설계 예시

다음에 주어진 사양을 고려하여 150mW급의 높은 전압 변환 비를 갖는 DC/DC 플라이백 컨버터를 앞의 설계절차를 따라 그림 4와 같은 회로를 설계 한다.

Step 1 컨버터 사양

- · 입력전압범위:  $V_{gmin}$ =24V,  $V_{gmax}$ =27V

- · 출력전압:  $V_o = -1.22 \mathrm{kV}$  (2배 전압 채배기 플라이백 회로 사용:  $V_{cI} = 610 \mathrm{V}$ )

- · 부하범위: 12.2uA<=I<sub>0</sub><=122uA

- · 스위칭 주파수: f<sub>s</sub>=70kHz

- · 최소 커패시터 값: C<sub>0</sub>=90pf, C<sub>s</sub>=10pF, C<sub>ws</sub>=20pF

**Step 2** *Q*<sub>p</sub>와 *f*<sub>ns</sub> 선택: 스위치의 Power Loss를 우선 고려하여 *Q*<sub>p</sub>=84와 *f*<sub>ns</sub>=0.993을 선택한다.

Step 3 M과  $\Theta_{I'}$   $\Theta_{I}$  도출: step 2를 통해서 선택한  $Q_p$ =84와  $f_{ns}$ =0.993에 따라 입력 대 일차 측으로 반영된 출력 비 M과 각 구간의 위상 정보  $\Theta_{I'}$   $\Theta_{I}$ 를 비선형 5원5차 방정식을 통해 구한다. M=1.0163,  $\Theta_{I}$ =2.362,  $\Theta_{I'}$ =0.338,  $\Theta_{I'}$ =3.321,  $\Theta_{I'}$ =0.253의 해가구해졌다.

Step 4 권선 비,  $L_m$ , C의 공진 설계 값 도출: step 3으로부터 도출한 M과  $\Theta_{I'}$   $\Theta_{I'}$ 를 식 (4), (5), (6)을 각 값을 구하면, n=0.04,  $Z_o$ =44.66 $\Omega$ ,  $f_o$ =70.45kHz로 도출되고 공진 설계값인 자화 인덕턴스  $L_m$ =100.8uH, 공진 커패시터  $C_r$ =50.58nF이 구해진다. 구해진 공진 커패시터 값이  $C_{r,min}$ =18.86nF 값보다 크므로 step 5 과정을 수행한다.

Step 5 스위치 전압 및 전류 스트레스: 식(7)을 이용하여 전

류 피크 값은 iLm,pk=586mA 임을 확인하고, 식(8)을 통

| 구 분                     | 실험결과 값    | 시뮬레이션 값   | 오차       |

|-------------------------|-----------|-----------|----------|

| $V_O$                   | -1226 [V] | -1205 [V] | 1.71 [%] |

| $V_{ce,\mathrm{max}}$   | 50.3 [V]  | 48.5 [V]  | 3.58 [%] |

| $V_{G\!r,\mathrm{max}}$ | 24.7 [V]  | 24.0 [V]  | 2.83 [%] |

| $V_{G,\min}$            | -26.0 [V] | -24.0 [V] | 5.80 [%] |

| $V_{ m sec, max}$       | 637 [V]   | 600 [V]   | 5.81 [%] |

| V <sub>sos min</sub>    | -655 [V]  | -613 [V]  | 6.41 [%] |

표 1 하드웨어 · 시뮬레이션 결과 비교 데이터

하여 스위치 차단 시 양단 최대전압은  $V_{d,max}$ =1210V임이 확인된다. 마진을 고려하여 스위치는 KSD526-Y, 출력 다이오드는 718을 선정한다.

#### 2.3 실험결과

그림 5는 시뮬레이션 결과와 실험 결과 파형이다. 표 1에 실제 실험 결과 값과 시뮬레이션 결과 값을 비교 하였다. 출력전압의 시뮬레이션과 실험의 비교 결과 값이 각각 -1226[V]와 -1205[V]로 오차 1.71%에서 일치하는 것을 볼 수 있다.

## 3. 결 론

본 논문에서는 고전압 플라이백 컨버터에서 나타나는 기생 커패시턴스와 자화 인덕턴스를 고려한 공진요소를 분석하였다. 이 공진요소를 바탕으로 고전압 플라이백 컨버터의 동작모드 해석을 수행하였다. 모드별 해석에 근거하여 자세한 설계절차를 제시하였으며, 이를 검증하기 위해 PSIM 시뮬레이션과실험을 수행하였다. 공진형 플라이백 컨버터의 동작모드의 수치적인 해석과 그 결과 값을 적용한 시뮬레이션 파형이 일치함을 볼 수 있었으며, 수치적인 모델링과 해석의 타당성을 검증할 수 있었다. 공진요소를 포함한 고전압 플라이백 컨버터의특성해석으로 높은 출력전압이 필요한 응용분야에 제시된 설계절차를 널리 적용될 수 있으리라 기대된다.

#### 이 논문은 삼성전기의 연구비 지원에 의하여 연구되었음

## 참 고 문 헌

- [1] H, Mohan, Modern Power Electronics, Mc-Graw Hill, 1999.

- [2] F.C. Lee, "High-frequency quasi-resonant converter technologies," Proc. of the IEEE, vol. 76, no. 4, Apr. 1988, pp. 377-390.

- [3] Staff of the Dept of EE, MIT, Magnetic Circuits and Transformer, MIT Press, 1995