## 계통연계형 인버터에서 대칭 구조를 갖는 LCL 필터 설계 및 제어

이귀준, 박남주, 현동석 한양대학교

# Design of an LCL Filter employing a Symmetric Geometry and its Control in Grid-connected Inverter Applications

Kui-Jun Lee, Nam-Ju Park, Dong-Seok Hyun Hanyang University

## ABSTRACT

An inductor-capacitor-inductor (LCL) filter are widely adapted in grid-connected inverter applications. In this paper, the harmonic attenuations of the LCL filter are quantitatively analyzed, and then the design optimization of two inductance values, which are related on a cost and a size, is illustrated. Based on the design optimization, the LCL filter employing a Symmetric Geometry is proposed. Through the equivalent circuit analysis of the proposed LCL filter, the operating characteristics and validity are presented in detail. In addition, simple proportional-integral (PI) current controller suitable for the LCL Filter is designed to mitigate the resonance problem. From simulation results, it is seen that the proposed LCL filter and control method have a sufficient attenuation and stability for the high frequency distortions and load variations.

## 1. 서 론

분산발전 시스템과 계통과의 연계 필요성이 증가함으 로 인해, 계통연계형 인버터에 대한 수요가 점차 증가하 고 있으며, 시스템의 저비용, 고효율, 고신뢰성을 만족시 키기 위한 많은 연구가 진행되고 있다. 계통연계형 인버 터의 주요 쟁점은 정현파 전류를 만들기 위한 전류 제어 이지만, PWM 기법으로 인한 고조파는 제어될 수 없으 며, 이를 위해 L 필터 혹은 LCL 필터와 같은 저역통과 필터가 사용된다. L 필터는 단순한 구조로 인해 구현이 용이하지만 충분한 고조파 저감을 위해 큰 인덕턴스와 높은 스위칭 주파수가 요구되는 반면에 LCL 필터는 L 필터보다 우수한 고조파 저감 특성을 갖지만 공진으로 인해 전류 제어기 설계에 있어 주의가 요구된다[1]. 공진 문제를 해결하기 위해 커패시터에 직렬로 저항을 삽입하 는 수동 보상 기법과 제어기를 재구성하는 능동 보상 기 법이 제안되었다<sup>[2-3]</sup>. 또한 문헌<sup>[4]</sup>은 시스템의 안정성이 LCL 필터의 피드백 변수에 상당히 의존함을 보여주며, LCL 필터 설계가 시스템의 안정성에 큰 영향을

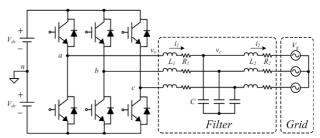

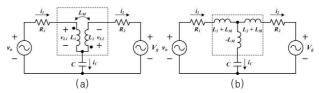

그림 1 LCL 필터를 갖는 3상 계통연계형 인버터 시스템

Fig. 1 Three-phase grid connected inverter with an LCL filter

미치기 때문에 안정성, 전류 제어 능력, 효율, 비용을 고려할 필요가 있다.

본 논문은 계통연계형 인버터에서 대칭 구조를 갖는 새로운 LCL 필터를 제안된다. 이를 위해 LCL 필터의 고조파 저감에 대한 정량적 분석과 IEEE std. 519-1992를 만족시키기 위한 필터값이 제시되며, 이러한 분석을 근거로 두 인덕터를 하나의 코어에 결합시켜 부피, 비용, 코어 손실을 줄일 수 있는 LCL 필터를 제안한다. 제안된 LCL 필터의 타당성은 등가모델과 시뮬레이션 결과를통해 증명한다.

## 2. 3상 계통연계형 인버터 시스템

그림 1은 LCL 필터를 갖는 3상 계통연계형 인버터의 회로도이다. 전류 제어기를 잘 설계하면 인버터 출력 전류( $i_1$ ,  $i_2$ )의 저차 고조파 왜곡을 저감할 수 있지만, PWM 스위칭 혹은 계통 전압의 왜곡으로 인한 고조파 전류 왜곡 성분은 전류 제어기의 대역폭 제한으로 인해 여전히 존재한다. 이러한 성분을 줄일 수 있는 유일한 대안은 출력 필터이며, IEEE std. 519-1992 는 계통연계시 만족시켜야 할 total demand distortion(TDD)이 5% 이하가되어야 함을 제시한다.

고조파 특성을 분석하기 위해, 일반적인 반주기 대칭배열 방식의 PWM 기법을 적용한다<sup>[5]</sup>. 해석의 편의상 전류 제어기는 넓은 대역폭을 갖고 저주파수의 전류 리플은 완전히 저감됨을 가정하며, 인덕터의 등가직렬저항은 무시한다. 그림 1의 3상 인버터에서 레그 a 와 b 의 선간전압은 식 (1)로 표현되며, M 은 변조지수,  $\omega_{o}$ 는

#### 표 1 설계 사양

Table 1 Design Specifications

| 인버터 출력 파워 ( <i>P,</i> )          | 1.5 kW   |

|----------------------------------|----------|

| 계통 선간전압 ( <i>E<sub>n</sub></i> ) | 110 Vrms |

| 계통 주파수                           | 60 Hz    |

| DC-Link 전압 (Vdc)                 | 300 V    |

| <br>변조지수 ( <i>M</i> )            | 0.8      |

| 샘플링 주파수                          | 20 kHz   |

| 스위칭 주파수                          | 10 kHz   |

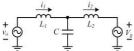

그림 2 등가 단상 LCL 필터

Fig. 2 Equivalent single-phase LCL filter

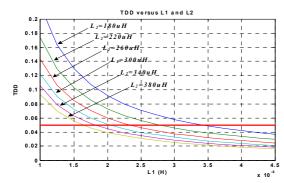

그림 3 인덕턴스에 따른 TDD 변화

Fig. 3 Relation between TDD and inductances in LCL filter

기본파 주파수,  $\omega_c$  는 캐리어 주파수이다. 식 (1)로부터 출력 선간전압은 기본파 주파수와 캐리어 주파수 부근의 고조파 성분들로 구성됨을 알 수 있다. 또한 최적의 필터 파라미터를 선정하기 위해, 분석에 사용된 설계 사양은 표 1과 같다.

그림 2는 한 상에 대한 LCL 필터의 등가 회로이다. 만약 계통 전압( $V_g$ )에 고조파가 존재하지 않는다고 가정하면, 계통측 인덕터( $L_2$ )에 흐르는 고조파 전류는 식 (2)로 구해지며,

$$i_{L2h} = \frac{v_o - v_{o1}}{(j\omega)^3 L_1 L_2 C + j\omega (L_1 + L_2)}$$

(2)

커패시터는 식 (3)에 의해 10 µF 으로 선정된다.

$$C_f < 0.05 \times \frac{P_n/3}{\omega_o \times \left(E_n/\sqrt{3}\right)^2} \tag{3}$$

그림 3은 LCL 필터의 인덕터 값들( $L_1$ ,  $L_2$ )을 변화시키면서 식 (2)를 이용하여 TDD 를 계산한 결과를 보여준다. 결과적으로 두 개의 인덕터 값이  $L_1=L_2=250~\mu\mathrm{H}$ 로 동일할 때, 총 인덕터의 합이 최소화 됨을 알 수 있다. 그러나 공진 주파수를 고려해야 하며, 본 논문에서는시스템의 안정성을 확보하기 위해 인덕터의 값을  $L_1=L_2=1.5~\mathrm{mH}$ 로 증가시켰다. 이에 따른 공진 주파수는  $1.8~\mathrm{kHz}$ 가 되며, 증가된 인덕터로 인해 TDD 는 0.11%

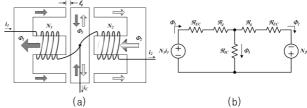

그림 4 대청구조를 갖는 제안된 인덕터 구조 (a) 물리적 모델 (b) 자기 회로 모델

Fig. 4 The proposed inductor configuration with symmetric geometry (a) Physical model (b) Magnetic circuit model

그림 5 (a) 결합구조를 갖는 전기적 모델(b) 결합구조를 갖지 않는 등가 전기적 모델

Fig. 5 (a) Electrical model with coupling structure (b)

Equivalent electrical model with no coupling structure

로 더욱 감소했다. 그러나 LCL 필터는 인덕터의 분리된 구조로 인해 야기될 수 있는 부피와 비용의 증가를 최소 화시키는 필터 설계가 요구된다.

### 3. 제안된 LCL 필터와 전류 제어

앞선 결과로부터 동일한 인덕터 값은 TDD 를 가장 최소화시킴을 알 수 있다. 또한 LCL 필터 구조는 기본 주파수 영역에서 C 의 임피던스가 매우 크기 때문에, 두 개의 인덕터( $L_I$ ,  $L_2$ )에 동일한 전류가 흐른다고 가정할 수 있다. 본 논문에서는 이러한 두 특성을 활용하기 위해, 그림 4(a)와 같은 페라이트 EIE 코어를 이용하여 대칭 구조를 갖는 LCL 필터를 제안한다.

그림 4(a)에서,  $N_I$ 과  $N_2$ 는 각각 전류  $i_I$ 과  $i_2$ 가 흐르는 도체의 턴 수이고,  $I_g$ 는 E 코어와 I 코어 사이의 공극길이다.  $\Phi_I$ ,  $\Phi_2$ ,  $\Phi_3$ 는 해당 코어에 흐르는 자속을 나타낸다. 제안된 LCL 필터의 장점과 동작 특성은 다음의회로 모델을 통해서 자세히 설명된다.

그림 4(b)는 그림 4(a)의 자기 회로 모델을 보여준다. 전압원으로 표시된  $N_Ii_I$ 은  $N_I$  턴에 전류 $(i_I)$ 가 흐를 때발생하는 기자력이며,  $N_2i_2$ 도 유사하게 모델링된다.  $\mathcal{R}_{EC}$ ,  $\mathcal{R}_{IC}$ ,  $\mathcal{R}_g$ 는 각각 E 코어, I 코어, 공극의 릴럭턴스이며,  $\mathcal{R}_{EC} = \mathcal{R}_{IC} = 1/\mu_r\mu_oA_c$ ,  $\mathcal{R}_g = 1/g\mu_oA_c$ 로 주어진다. 여기서 I은 해당 코어의 자기 경로 길이이며,  $A_c$ 는 코어의 유효 단면적이다.

$$v_{ab}(t) = \sqrt{3}V_{dc}M\cos\left(\omega_{o}t + \frac{\pi}{6}\right) + \frac{8V_{dc}}{\pi}\sum_{m=1}^{\infty}\sum_{n=-\infty}^{\infty}\frac{1}{m}J_{n}\left(m\frac{\pi}{2}M\right)\sin\left([m+n]\frac{\pi}{2}\right)\sin\left(n\frac{\pi}{3}\right) \times \cos\left(m\omega_{c}t + n\left[\omega_{o}t - \frac{\pi}{3}\right] + \frac{\pi}{2}\right)$$

$$(m = 1, 2, ..., \infty , n = -\infty, ..., -1, 0, 1, ..., \infty)$$

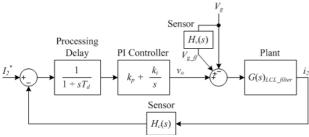

그림 6 PI 전류 제어 블록도

Fig. 6 Block diagram of the synchronous PI current controller

야기되는  $\Phi_{12}$ 의 합으로 표현될 수 있다.

$$\Phi_{1} = \Phi_{11} + \Phi_{12}$$

$$\Phi_{11} = \frac{N_{1}i_{1}}{\Re_{EC} + \Re_{g} + [\Re_{IC} //(\Re_{g} + \Re_{EC})]}$$

$$\Phi_{12} = \frac{N_{2}i_{2}}{\Re_{EC} + \Re_{g} + [\Re_{IC} //(\Re_{g} + \Re_{EC})]}$$

$$\times \frac{\Re_{IC}}{(\Re_{EC} + \Re_{g}) + \Re_{IC}}$$

(4)

유사하게  $\Phi_2$  와  $\Phi_3$  도 각각 표현될 수 있으며, 이를 이용하면, 한 상에 대한 제안된 LCL 필터의 등가 전기회로 모델을 그림 5(a)처럼 표현할 수 있다. 식 (4)로부터 인덕터 $(L_1)$ 에 인가된 전압은 패러데이 법칙으로부터 유추된다. 또한 그림 5(a)는 그림 5(b)의 결합구조를 갖지 않는 등가 전기회로 모델로 변환될 수 있다.

만약  $N_I$  과  $N_2$  가 같다라고 가정하면, 상호 인덕턴스  $(L_M)$ 는 매우 작은 값을 갖기 때문에, 커플링에 의한 영향은 무시할 수 있다. 이로 인해, 제안된 LCL 필터는 기존의 독립적인 LCL 필터를 추가적인 보상없이 대체할수 있고, 부피와 무게에 있어서 장점을 가지며, 뿐만 아니라 사용된 I 코어의 폭은 실질적으로 매우 짧아질 수있다.

그림 6은 계통측 인덕터의 전류를 제어하기 위한 전류 제어 블록도이다. 기준값 $(I_2^*)$ 은 계통측 인덕터의 전류 기준값이고, 계통 전압 $(V_g)$ 은 기본파와 저차 고조파를 포함한 왜란으로 간주된다. 전류 제어를 위해 동기 PI 제어기가 사용되며, 처리 지연 블록과 계통 전압의 왜곡 효과를 보상하기 위한  $V_{g,ff}$  가 추가된다. 처리 지연 블록에서  $T_d$ 는 샘플링 시간 $(=T_s)$ 과 PWM 지연 $(\approx 0.5\ T_s)$ 의합으로 표현된다. 제어기의 게인은  $k_p=0.1,\ k_i=40$ 로 선정된다.

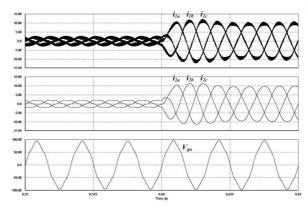

## 4. 시뮬레이션

그림 7은 계통 전압에 5%의 5차 고조파와 3%의 7차 고조파가 존재할 때, 20% 부하에서 풀 부하로 가변 시전류가 잘 추종함을 보여준다. 비록 전류에 약간의 왜곡이 발생하지만 위상 검출을 위해 사용된 위상고정루프 (PLL)의 성능을 향상시키거나  $H_v(s)$ 의 차단 주파수를 증가시키면 개선될 수 있다.

## 5. 결 론

그림 7 계통 전압에 5%의 5고조파와 3%의 7고조파 존재 시 인덕터 전류 파형

Fig. 7 Inductor currents and grid voltage waveform using LCL filter with 5% fifth and 3% seventh grid voltage harmonic. Time: 25 ms/div.,  $i_1$ : 5 A/div.,  $i_2$ : 5 A/div.,  $V_{\alpha\beta}$ : 50 V/div

LCL 필터의 두 인덕턴스 값이 같을 때 고조파 저감효과가 가장 우수함을 이용하여 대칭 구조를 갖는 LCL 필터 구조를 제안하고, 등가모델을 통해 제안된 LCL 필터의 특성을 살펴보았다. 제안된 LCL 필터는 EIE 코어구조를 가지며 형태상으로 두 인덕터를 하나의 코어에결합시키는 구조로써 부피와 무게를 감소시킬 수 있다. 제안된 LCL 필터의 타당성은 시뮬레이션을 통해 증명하였다.

본 연구는 산업자원부 전력IT사업 중 "분산발전 및 산업용 인버터 응용을 위한 전력반도체 기술개발"의 지원에 의하 여 수행되었음.

## 참 고 문 헌

- [1] E. Twining and D. G. Holmes, "Grid current regulation of a three-phase voltage source inverter with an LCL input filter," IEEE Trans. Power Electron., Vol. 18, no. 3, pp. 888-895, May 2003.

- [2] M. Liserre, A. Dell'Aquila, and F. Blaabjerg, "Stability improvements of an LCL-filter based three-phase active rectifier," in Proc. of IEEE PESC, Cairns, Australia, pp. 1195-1201, June 2002.

- [3] M. Liserre, A. Dell'Aquila, and F. Blaabjerg, "Genetic algorithm-based design of the active damping for an LCL-filter three-phase active rectifier," IEEE Trans. Power Electronics., vol. 19, pp. 76-86, Jan. 2004.

- [4] T. Abeyasekera, C. M. Johnson, D. J. Atkinson, and M. Armstrong, "Suppression of line voltage related distortion in current controlled grid connected inverters," IEEE Trans. Power Electronics., vol. 20, pp. 1393-1401, Nov. 2005.

- [5] D. G. Holmes, T. A. Lipo, Pulse Width Modulation for Power Converters – Principle and practice, IEEE Press, 2003.