# 2.4GHZ CMOS LC VCO with Low Phase Noise

Cheng Qian, and Nam Young Kim

Department of Electronics Engineering, Kwangwoon University

Abstract: This paper presents the design of a 2.4 GHz low phase noise fully integrated LC Voltage-Controlled-Oscillator (VCO) in 0.18 µm CMOS technology. The VCO is without any tail bias current sources for a low phase noise and, in which differential varactors are adopted for the symmetry of the circuit. At the same time, the use of differential varactors pairs reduces the tuning range, i.e., the frequency range versus VTUNE, so that the phase noise becomes lower. The simulation results show the achieved phase noise of -138.5 dBc/Hz at 3 MHz offset, while the VCO core draws 3.9mA of current from a 1.8V supply. The tuning range is from 2.28GHz to 2.55 GHz.

Key Words: varactor, phase noise, tail bias current source, voltage controlled oscillator(VCO), Submicron CMOS

## 1. Design of VCO

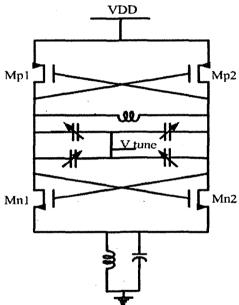

The LC VCO core is based on a fully-differential cross-coupled topology and is shown in Fig. 1. Differential topologies are generally preferred since they offer better power supply and substrate noise rejection over single-ended designs. Although a complementary cross-coupled topology is attractive because of its higher tank voltage amplitude for a given bias current and LC tank configuration, this benefit should be carefully weighted against its reduced headroom, increased parasitics, and additional noise sources.

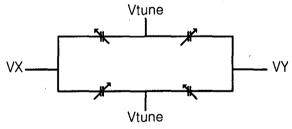

The 2.4 GHz LC CMOS VCO using differential varactors without tail bias current source is shown in Fig. 1. The differential varactor pair is used to enhance the symmetry of the circuit, shown in Fig. 2, while the differential varactor pair will reduce the tuning range more quickly than a constant capacitor used, but for a narrow band VCO, it is enough.

PMOS devices were chosen to reduce flicker noise at the expense of reduced transconductance for a given aspect ratio. Despite the fact that the conductive channel is no longer buried as in older technologies, close scrutiny of the available flicker noise data revealed PMOS devices to have slightly lower flicker noise in the expected operating regimes. As an additional benefit, the device N-WELL provides some amount of isolation from the substrate.

Also, considering AM-PM conversion, the AM-PM conversion results from the capacitors dependent on voltage and varactors used to tune the VCO output frequency. These components make the VCO frequency  $\omega_{\circ}$  dependent on the oscillator amplitude A. So any modulation of the oscillation amplitude leads to a phase shift of the waveform, and AM noise translates into phase noise. The differential varactor pair reduces the tuning range, and hence reduces the AM-PM conversion. This means the phase noise will reduce for the same AM noise.

Figure 1. Circuit schematic of cross-coupled LC VCO

Figure 2. Differential varactors

Cross-coupled pair is also a noise source, so it is easy to think to increase the width of the transistors, then we can get a low flicker noise (See Eq. (1)).

$$\overline{i_{1/f}^2} = \frac{k_f}{fC_{ox}WL} \Delta f \tag{1}$$

However, the contribution of the cross-coupled pair is not only the noise source; but also the switching mechanism, power assumption and start-oscillation are very important. Because there is no tail bias current source in the circuit, so the total current will be controlled by the transistors of the cross-coupled pair, we can adjust the transistor size so as to assume low current and hence low power assumption. The cross-coupled pair is also the function of negative resistors, in terms of energy, the energy of negative resistors should be larger than that of the parallel resistor in the tank, and then the VCO can start oscillation. Also if we increase the transistor width in order to reduce the flicker noise, then the parasitic capacitors of transistors will increase, which will reduce the tuning range, and they are nonlinear capacitors and hence result in AP-MP conversion [7].

For a large output waveform amplitude, the MOS transistors will be in triode region for a while, when we can consider it as a resistor, then it will be loaded into the LC tank and hence degrade the quality factor Q, where the quality factor is called loaded Q. The loaded Q is given by Eq. (2):

$$Q_{Load} = \frac{Q_{Unload} R_L}{Q_{Unload} \omega_0 L + R_L}$$

(2)

As published by Leeson in 1966 [8], the phase noise of an LC VCO can be described as Eq. (3):

$$L(f_o) = \frac{2kTR_{eq}F}{A_o^2} \left(\frac{f_0}{2Q\Delta f}\right)^2 \left(1 + \frac{\Delta f_{f_o}}{\Delta f}\right)$$

(3)

According to the equation, we can see that what determine the phase noise at the offset frequency  $\Delta f$  are loaded quality factor of the LC tank Q, voltage swing amplitude A0, corner frequency of the device's flicker noise  $\Delta f_{1/13}$ , and the oscillation frequency f0. The equation suggests that the most effective way to lower the phase noise while maintaining the same bias current is to improve the loaded quality factor of the LC tank.

With regard to the foregoing issue, a filter technique can be used. The filter is working in  $2\omega_o$  to stop the second harmonic flow into the ground, and hence prevent the MOS transistors from being loaded into the LC tank, resulting in reduced Q. Because the even harmonic will flow in the common mode path, the odd harmonic will flow in the differential mode path.

In the design, the bias current is removed. As being known, the bias noise is a large noise source, which includes thermal noise and low frequency flicker noise. These noises will be up-converted into phase noise due to the switching mechanism of the cross-coupled pair as a single balanced mixer [9] and AP-MP conversion. Generally the thermal noise is converted into  $1/f^2$  and the flicker noise is converted into  $1/f^2$  region[10]. As to AM-PM conversion, in fact, in order to reduce the AM-PM conversion factor we

can reduce the transistors width of the cross-coupled pair to increase the gate overdrive V<sub>gs</sub>-V<sub>t</sub>, and hence increase the linearity of the transistors [5]. And as the width is reduced, the nonlinear parasitic resistor will be reduced and hence is reduced the AM-PM conversion dependent on the transistors of cross-coupled pair. We can also minimize the varactor sensitivity (MHz/V) and reduce the AM-PM conversion of the varactor at the cost of a reduced tuning range. A tail current source must match a current mirror, the mirror will also add noise to the bias MOS transistor, and then is converted into phase noise. Due to the above issue, so in the design, we remove the tail bias current source.

#### 2. Simulation Results

The VCO is optimized based on phase noise reduction in the last section. The LC VCO is designed in  $0.18\mu m$  CMOS technology. With simulation, phase noise of -138.5 dBc/Hz at 3 MHz offset, is obtained with  $f_0$ =2.4 GHz. Adjusting the differential varactor pair to compensate the symmetry of the circuit, at the same time we must consider the tuning range, which is decided by varactors and parasitic capacitors[11].

$$FTR = \frac{C_P + C_{\nu,\text{max}}}{C_P + C_{\nu,\text{min}}} \tag{4}$$

The tuning range is simulated to be from 2.28 GHz to 2.55GHz.

Table 1 summarizes the simulated performance results of the proposed VCO.

TABLE 1 Performance summary of the VCO

| Items                    | Performance  |

|--------------------------|--------------|

| Power Supply             | 1.8V         |

| Frequency                | 2.4GHz       |

| Tuning Range             | 270MHz       |

| Power Consumption        | 7mW          |

| Phase Noise@ 3MHz offset | -138.5dBc/Hz |

In order to make comparisons between different VCOs with respect to power, carrier frequency and phase noise, a VCO figure-of-merit is used:

$$FOM = -L(\Delta f) + 20\log(\frac{f_0}{\Delta f}) - 10\log(p)$$

(5)

Where  $f_0$  is the carrier frequency,  $\Delta f$  is the offset frequency from carrier frequency,  $L(\Delta f)$  is the phase noise, and p is the power consumption by the VCO. The FOM of VCO is calculated to be -188.1.

# 3. Conclusion

The 2.4GHz VCO is designed in 0.18 µm CMOS

technology. The VCO uses differential varactors for the symmetry of the circuit, in which 3.9 mA current flows though VCO core from the 1.8 V power supply. And the tuning range is from 2.28GHz to 2.55GHz with 0-1.8V tuning voltage. Running simulation, the phase noise is -138.5 dBc/Hz at 3 MHz offset frequency with 2.4 GHz oscillation frequency. It should be noted the VCO just uses a filter, in other words, it uses only two inductors, so that it will reduce the layout area largely.

#### Acknowledgement

This research was supported by Nano IP/SoC Promotion Group, 3D Micro-system Packaging of Seoul R&BD Program, the MKE (Ministry of Knowledge Economy), Korea under the ITRC (Information Technology Research Center) Support program supervised by the IITA (Institute of Information Technology Advancement)" (IITA-2008-C1090 -0801-0018) and also by research grant of Kwangwoon University, 2008.

## References

- H. M. Wang, "Comments on Design Issues in CMOS Differential LC Oscillators," IEEE Transactions on Solid State Circuits, VOL. 35, NO. 2, February 2000.

- [2] J. Rael and A. Abidi, "Physical processes of phase noise in differential LC oscillators," IEEE Custom Integrated Circuits Conf. (CICC),2000, pp. 569 - 572.

- [3] E. Hegazi, H. Sjoland, and A. A. Abidi, "A filtering technique to lowerLC oscillator phase noise," IEEE J. Solid-State Circuits, vol. 36, no. 12, pp. 1921 - 1930, Dec. 2001.

- [4] S. Levantino, C. Samori, A. Bonfanti, S. L. J. Gierkink, A. L. Lacaita, and V. Boccuzzi, "Frequency dependence on bias current in 5-GHz CMOS VCOs: Impact on tuning range and flicker noise upconversion," IEEE J. Solid-State Circuits, vol. 37, no. 8, pp. 1003 1011, Aug. 2002.

- [5] Albert Jerng, Charles G.Sodini, "The Impact of Device Type and Sizing on Phase Noise Mechanisms", IEEE journal of solid-state circuits, VOL. 40, NO. 2, February 2005.

- [6] S. Levantino, C. Samori, A. Zanchi, and A. L. Lacaita, "AM-to-PM Conversion in Varactor\_tuned Oscillators," IEEE Transactions on Circuits and Systems - II: Analog and Digital Signal Processing, VOL. 49,NO. 7, July 2002.

- [7] B. Soltanian, and P. Kinget, "AM-FM Conversion by the Active Devices in MOS LC-VCOs and its Effect on the Optimal Amplitude" IEEE.

- [8] D. B. Leeson, "A simple model of feedback oscillator

- noise spectum," IEEE, 1966..

- [9] E. Hegazi, H. S. Asad A. Abidi, "A Filtering Technique to Lower LC Oscillator Phase Noise", IEEE journal of solid-state circuits, VOL. 36, NO. 12, December 2001.

- [10] A. Hajimiri, Thomas H.Lee, "A General Theory of Phase Noise in Electrical Oscillators", IEEE journal of solid-state circuits, VOL. 33, NO. 2, February 1998.

- [11] Jonghae Kim, Jean-Olivier Plouchart, Noan Zamder, Melanie Sherony, Yue Tan, Meeyoung Yoon, Robert Trzcinsiki, Mohamed Talbi, John Safran, Asit Ray Lawrence Wangner, "A Power-Optimized widely\_tunable 5GHz monolithic VCO in a digital SOI CMOS Technology on High Resistivity Substrate," ISLPED'03,2003, Seoul Korea.